# Introducing the Compute Express Link<sup>™</sup> 2.0 Specification

Dr Debendra Das Sharma

Intel Fellow, Director I/O Technology and Standards, Intel Compute Express Link Board Technical Task Force Co-chair

Ahmad Danesh

Product Marketing and Strategy, Data Center Solutions, Microchip Technology Compute Express Link Marketing Workgroup

# Industry Landscape

Cloudification of the Network & Edge

#### Proliferation of Cloud Computing

Growth of Al & Analytics

Compute Express Link<sup>™</sup> and CXL<sup>™</sup> Consortium are trademarks of the Compute Express Link Consortium.

T's a d

12/10/2020

### CXL Delivers the Right Features & Architecture

#### Challenges

Industry trends driving demand for faster data processing and next-gen data center performance

Increasing demand for heterogeneous computing and server disaggregation

Need for increased memory capacity and bandwidth

Lack of open industry standard to address next-gen interconnect challenges

CXL An open industry-supported cache-coherent interconnect for processors, memory expansion and accelerators

#### **Coherent Interface**

Leverages PCIe with 3 mix-and-match protocols

#### Low Latency

.Cache and .Memory targeted at near CPU cache latency

#### Asymmetric Complexity

Eases burdens of cache coherent interface designs

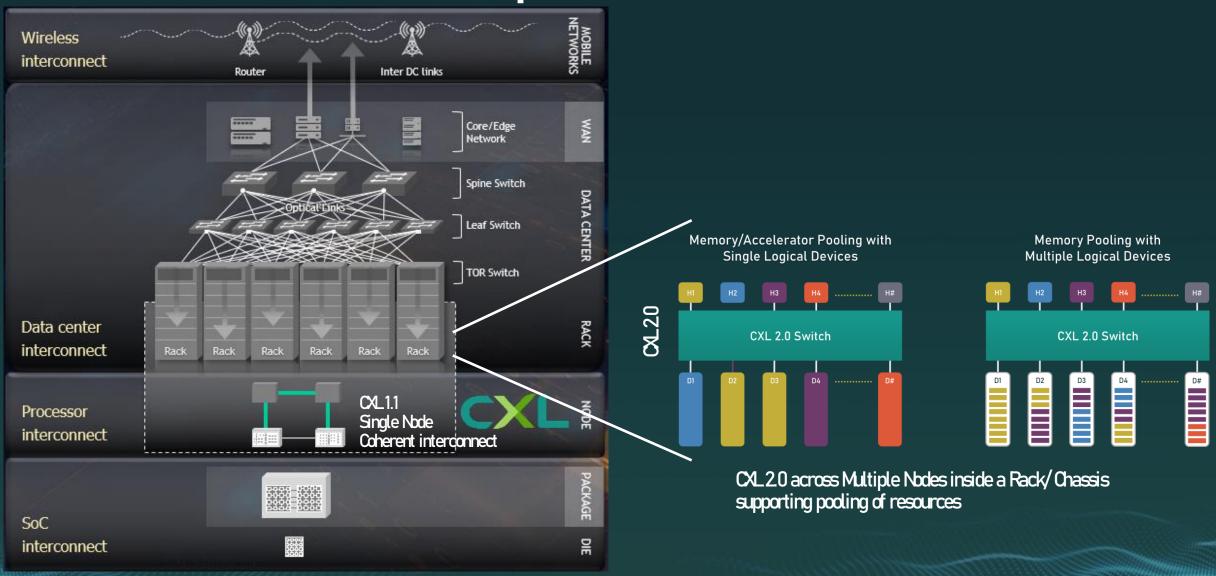

### Data Center: Scope of CXL2.0 over CXL1.1

### Representative CXL Usages

### CXL20 Introduces New Features and Usage Models

- Fully backward compatible with CXL1.1 and 1.0

- Switching and pooling

- Hot-plug support

- Fabric Manager API

- Persistent memory support

- Security

- Built in Compliance & Interop program

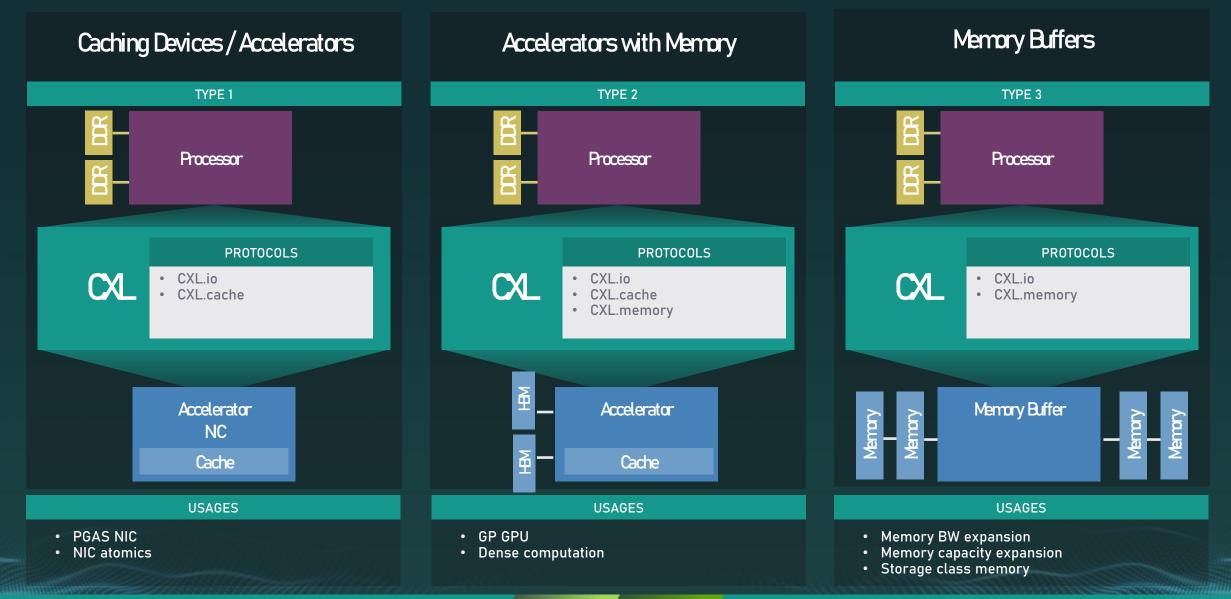

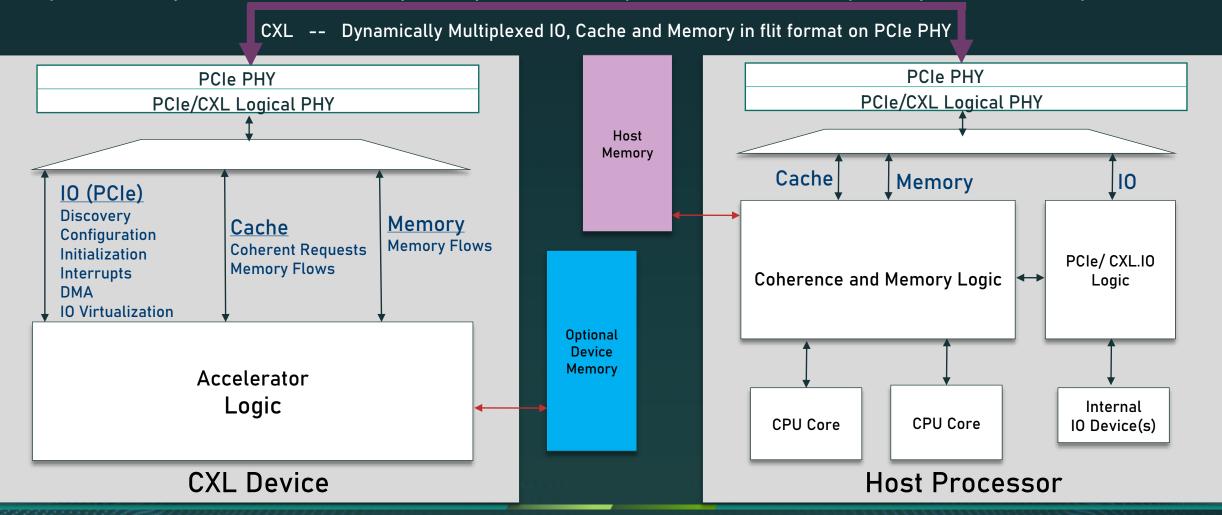

### CXL Multiprotocol Support with Asymmetry

CXL.IO – PCIe based – discovery, register access, interrupts, initialization, I/O Virtualization, DMA CXL.Cache – supports device caching of host memory with host processor orchestrating the coherency management CXL.Memory – memory access protocol, host manages (coherency) device attached memory similar to host memory Simple coherency flows for device w/ asymmetry => ease of adoption w/ backward compatibility for investment protection

## CXL2.0 Scope: Hot-Plug, Persistence, Switching, and Disaggregation

| Feature                                                                                    | Description                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CXL PCIe End-Point                                                                         | CXL device to be discovered as PCIe Endpoint<br>Support of CXL 1.1 devices directly connected to Root-Port or Downstream Switch Port                                                                                                                                                                            |  |  |  |  |

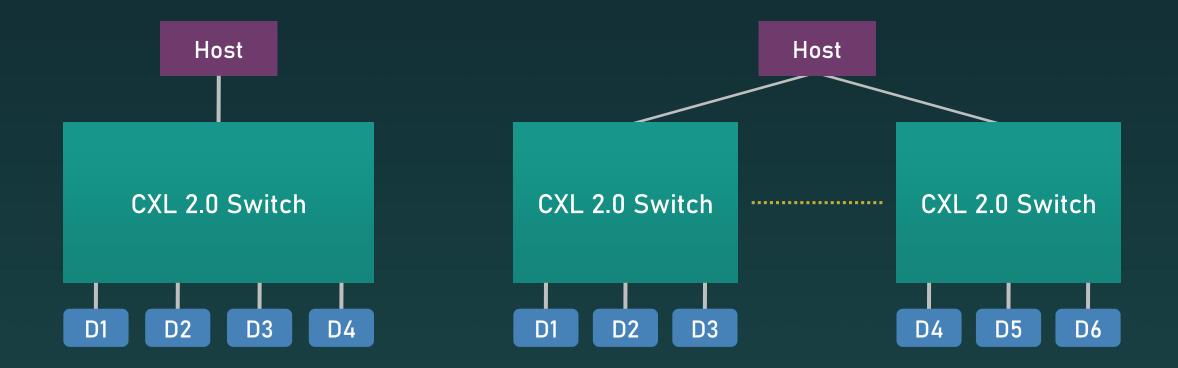

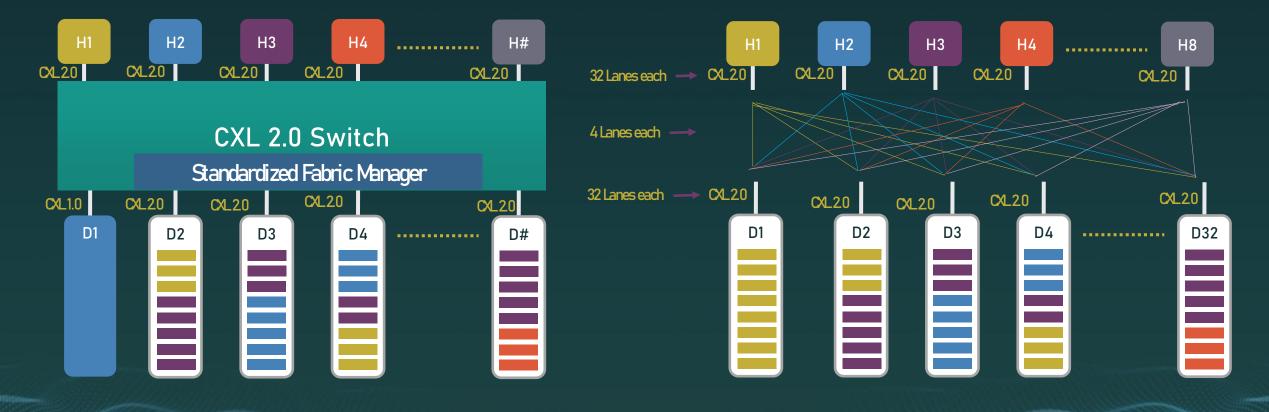

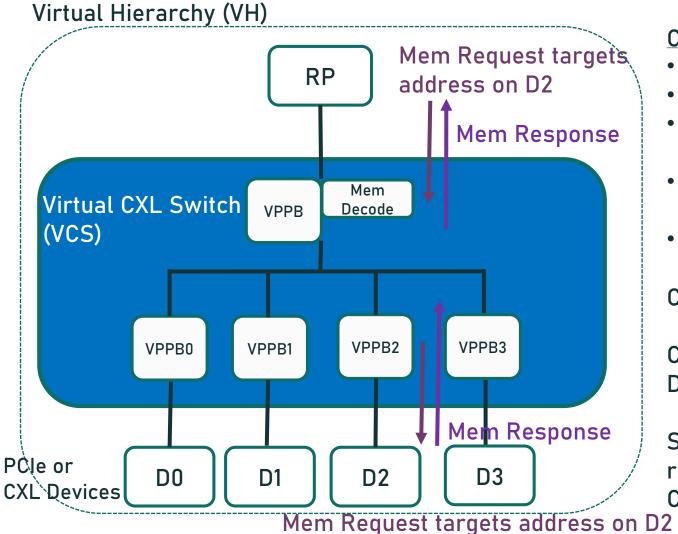

| Switching                                                                                  | Single level of switching with multiple Virtual Hierarchies (cascaded possible in a single hierarchy)<br>CXL Memory Fan-Out & Pooling with Interleaving<br>CXL.Cache is direct routed between CPU and device with a single caching device within a hierarchy.<br>Downstream port must be capable of being PCIe. |  |  |  |  |

| Resource Pooling                                                                           | Memory Pooling for Type3 device – Multiple Logical Device (MLD), a single device to be pooled across<br>16 Virtual Hierarchies.                                                                                                                                                                                 |  |  |  |  |

| CXL.cache and<br>CXL.mem<br>enhancements                                                   | Persistence (Global Persistence Flush), Managed Hot-Plug, Function Level Reset Scope Clarification,<br>Enhanced FLR for CXL Cache/Mem, Memory Error Reporting and QoS Telemetry                                                                                                                                 |  |  |  |  |

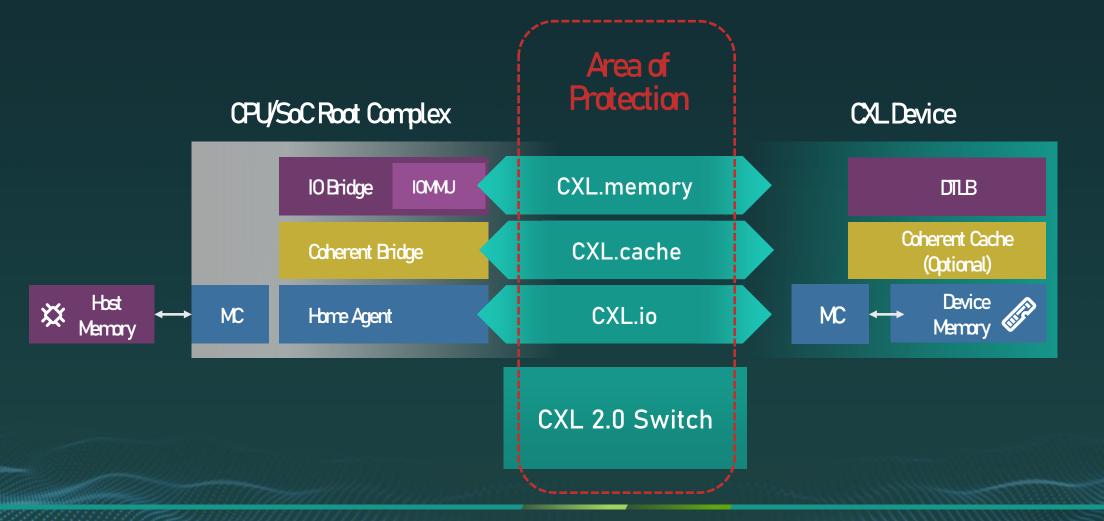

| Security                                                                                   | Authentication and Encryption – CXL.10 uses PCIe IDE, CXL defines similar capability for CXL.\$Mem                                                                                                                                                                                                              |  |  |  |  |

| Software<br>Infrastructure/ API                                                            | ACPI & UEFI ECNs to cover notification and management of CXL Ports and devices<br>CXL Switch API for a multi-host or memory pooled CXL switch configuration and management                                                                                                                                      |  |  |  |  |

| CXL 2.0 is <u>fully backwards compatible</u> with CXL 1.0/1.1 (see next slide for details) |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

Predictable spec release cadence by CXL consortium to help the ecosystem plan better.

12/10/2020

# CXL2.0: Backwards compatible with CXL1.0/1.1

| CPU – Device<br>Connectivity   | CXL 1.X (1.1/1.0)<br>EP |                       | CXL 2.0 EP |                                                                                                                                     | PCIe EP/<br>Switch | Comments                                                              |

|--------------------------------|-------------------------|-----------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|

| CPU with CXL<br>1.x            | CXL 1.x                 |                       | CXL 1.x    |                                                                                                                                     | PCIe               | CXL 2.0 EP needs to support both<br>RCiEP and EP modes                |

| CPU with CXL<br>2.0            | CXL 1.x                 |                       | CXL 2.0    |                                                                                                                                     | PCIe               | CXL 2.0 CPU also needs to be bi-<br>modal for backwards compatibility |

| CXL 2.0 Switch<br>Connectivity |                         | Operation             |            | Comments                                                                                                                            |                    |                                                                       |

| Upstream: CPU                  |                         | Only CXL 2.0          |            | Since switch definition is with CXL 2.0, the platform requirement is upstream port be a CXL 2.0 CPU                                 |                    |                                                                       |

| Downstream: CXL Device         |                         | CXL 1.x or<br>CXL 2.0 |            | All downstream CXL ports work as CXL 1.x or CXL 2.0 – mix and match to the device's capability                                      |                    |                                                                       |

| Downstream: PCIe EP/<br>Switch |                         | 1                     |            | Any CXL switch downstream Port must be able to support a PCIe hierarchy, either an EP or a PCIe switch but assigned to *one* domain |                    |                                                                       |

| Downstream: CXL Switch         |                         | N/A                   |            | CXL 2.0 is defined only as a single level switch for multiple virtual hierarchies (no cascading of CXL switches)                    |                    |                                                                       |

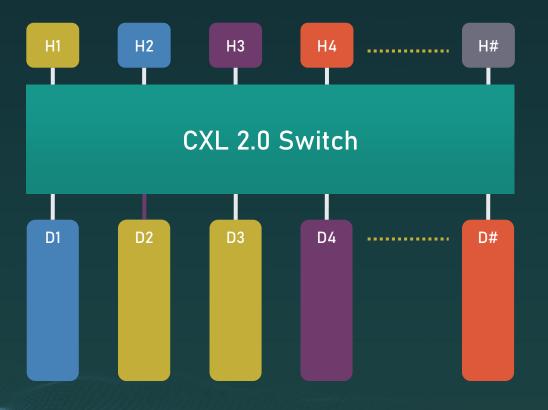

#### Benefit of CXL2.0 Switching Expansion

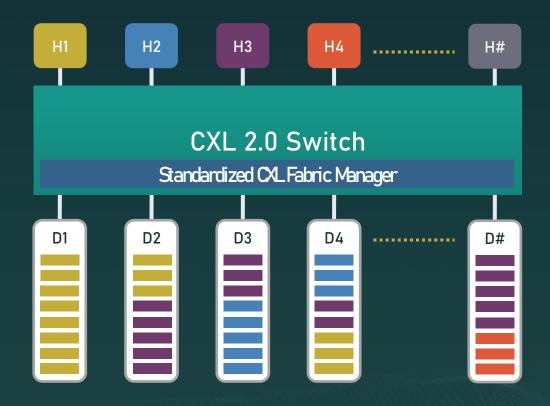

### Benefit of CXL2.0 Switching Pooling

#### Memory/Accelerator Pooling with Single Logical Devices

#### Memory Pooling with Multiple Logical Devices

## CXL2.0 Pooling without a Switch

#### Memory Pooling with Single/ Multiple Logical Devices

#### Memory Pooling with through direct connect

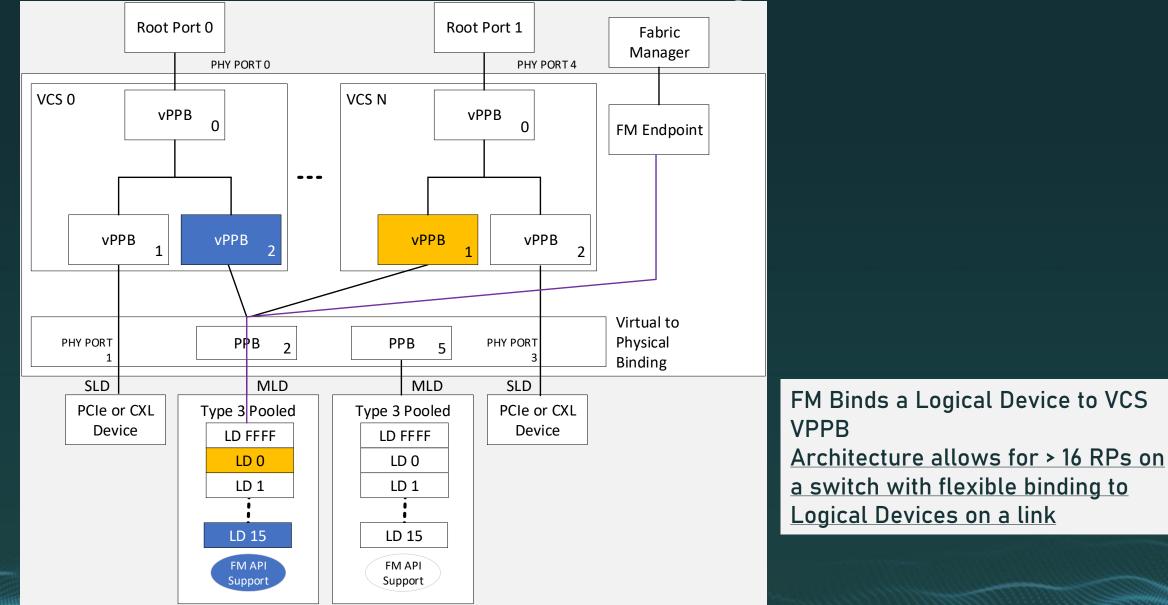

# CXL2.0 Hbt-Plug Support

#### Managed Hot Remove (Off-lining)

#### Managed Hot Add (On-lining)

>\_

CXL 2.0 Switch

CXL 2.0 Switch

Request host to remove device D3 from H

Host H quiesces traffic from D3 and indicates device is safe to remove

added to pool

CXL 2.0 Switch

Host H2 requests a device Fabric Manager assigns D3 through Switch and Initiates a Hot-add flow

Normal traffic flow to/from DB as a part of H2

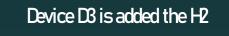

### CXL20 Memory Fan-Out Request Routing

#### CXL 2.0 Defines Memory Decode Mechanism

- Supports memory expansion

- Supports Interleave across devices

- 2 way, 4 way and 8 way Interleave options supported

- Determines the Downstream VPPB to route requests to

- Responses always routed to VPPB

CXL.IO same as PCIe decode

CXL.Cache – no fanout. Software must enable Single Device with CXL.Cache in Virtual Hierarchy

Switch does Address Look-Up and forwards request/ response between Downstream Port(s) and RP for CXL.IO and CXL.Mem

### CXL20 Fabric Manager View

#### Benefits of CXL20 and Persistent Memory

| Moves Persistent Memory<br>from Controller to CXL |                  |                             | rdized Management<br>ry and Interface | Supports a Wide Variety<br>of Industry Form Factors |                   |

|---------------------------------------------------|------------------|-----------------------------|---------------------------------------|-----------------------------------------------------|-------------------|

|                                                   |                  |                             |                                       |                                                     |                   |

| λ                                                 | XX CPU           |                             |                                       | 10 <sup>0</sup>                                     |                   |

| Memory                                            | DRAM CXL 1.1/1.0 |                             |                                       | 10 <sup>1</sup>                                     |                   |

| ž                                                 |                  | CXL 2.0                     |                                       |                                                     | CXL+PM            |

|                                                   | <b>E</b>         | Persistent Memory           |                                       | 10 <sup>2</sup> –10 <sup>3</sup>                    | Fills<br>the Gap! |

| D                                                 | đ                | Performance SSD             |                                       | 10 <sup>4</sup>                                     |                   |

| xorage                                            | Capacity SSD     |                             |                                       | 10 <sup>5</sup>                                     |                   |

| א                                                 | HDD              |                             |                                       | 106                                                 |                   |

|                                                   |                  | annon and the second second | Latency -                             | nanoseconds                                         |                   |

### CXL20 Security Benefits

CXL2.0 provides Integrity and Data Encryption of traffic across all entities (Root Complex, Switch, Device)

# In Summary

#### CXLConsortium momentum continues to grow

- 130+ members and growing

- Celebrating first anniversary of incorporation – second generation specification

- Responding to industry needs and challenges

#### CXL20 introduces new features & usage models

- Switching, pooling, fabric manager API, persistent memory, security, hot-plug

- Fully backward compatible with CXL1.1 and 1.0

- Built in Compliance & Interop program

#### Call to action

Jain CXL Consortium

• Follow us on <u>Twitter</u> and LinkedIn for more updates!

y in

Compute Express

Please share your questions in the Question Box

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

------

### Thank You