# Cache Coherent Interconnect for Accelerators

# CCIX<sup>®</sup> Base Specification Revision 1.0 Version 1.0

February 15, 2019

#### LEGAL NOTICE

#### © 2016-2019 CCIX CONSORTIUM, INC. ALL RIGHTS RESERVED.

This **CCIX Base Specification Revision 1.0 Version 1.0** (this "<u>document</u>") is proprietary to CCIX Consortium, Inc. (sometimes also referred to as "<u>Company</u>") and/or its successors and assigns.

#### 5 NOTICE TO USERS WHO ARE CCIX CONSORTIUM, INC. MEMBERS:

Members of CCIX Consortium, Inc. ("<u>CCIX Member(s)</u>") may use and/or implement this **CCIX Base Specification Revision 1.0 Version 1.0** subject, however, to the CCIX Member's compliance with all of the terms and condition of the Company's Intellectual Property Policy, Bylaws, and all other Company policies and procedures ("<u>CCIX Governing Documents</u>") and the CCIX Member's Participation Agreement.

- 10 Each CCIX Member hereby agrees that its use and/or implementation of this **CCIX Base Specification Revision 1.0 Version 1.0** and/or any of the specifications described herein are subject to the following additional terms and conditions:

- (i) The Company takes no position regarding, and each CCIX Member is solely responsible for determining on its own, the existence, validity, and/or scope of any intellectual property rights or any other rights (including without limitation any "Essential Claims" under the Company's Intellectual Property Policy) that any third party (including without limitation any other CCIX Member) may own or otherwise hold which may (or may not) pertain to or cover any implementation or other use of this CCIX Base Specification Revision 1.0 Version 1.0 or any specifications described herein.

- (ii) Each CCIX Member is solely responsible for:

- (a) determining whether any license or other consent (including without limitation any "FRAND License" under the Company's Intellectual Property Policy) from any third party (including without limitation from any other CCIX Member) is needed to implement or otherwise use this CCIX Base Specification Revision 1.0 Version 1.0 or any of the specifications described herein; and

- (b) Negotiating and obtaining, for itself, any such license or other consent (including without limitation any "FRAND License" under the Company's Intellectual Property Policy) from any and all such third parties (including without limitation from other CCIX Members).

#### NOTICE TO NON-MEMBERS OF CCIX CONSORTIUM, INC.:

If you are <u>not</u> a CCIX Member and you have obtained a copy of this document, you only have a right to review this document or make reference to or cite this document. Any such references or citations to this document must acknowledge CCIX Consortium's Inc.'s copyright ownership of this document. The proper copyright citation or reference is as follows: "©2016-2019 CCIX CONSORTIUM, INC. ALL RIGHTS RESERVED." When making any such citation or reference to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of CCIX Consortium, Inc. Nothing contained in this document shall be deemed as granting (either expressly or impliedly) to any party that is <u>not</u> a CCIX Member: (ii) any kind of license to implement or use this document or any specifications described therein or any of its contents, or any kind of license in or to any other intellectual property owned or controlled by CCIX Consortium, Inc., including without limitation any trademarks of CCIX Consortium, Inc.; or (ii) any benefits and/or rights as a CCIX Member under any CCIX Governing Documents.

If you are <u>not</u> a CCIX Member but still elect to implement this document or any of the specifications described herein, you are hereby given further notice that your election to do so does not give you any of the rights and/or protections of CCIX Members, including without limitation any of the rights and/or protections of CCIX Members under the Company's Intellectual Property Policy or other CCIX Governing Documents.

#### LEGAL DISCLAIMERS FOR ALL PARTIES:

THIS DOCUMENT AND ALL SPECIFICATIONS AND/OR OTHER CONTENT PROVIDED HEREIN IS PROVIDED ON AN "AS IS" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CCIX CONSORTIUM, INC. (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NONINFRINGEMENT. In the event this document makes any references (including without limitation any incorporation by

reference) to another party's ("<u>Third Party</u>") content or work, including without limitation any specifications or standards of a Third Party ("<u>Third Party Content</u>"), you may need to independently obtain a license or other consent from that Third Party in order to have full rights to implement or use that Third Party Content.

20

15

25

45

# Table of Contents

| Chapter 1.       | Document Overview                                                     | 18       |

|------------------|-----------------------------------------------------------------------|----------|

| 1.1 Spe          | CIFICATION OBJECTIVE                                                  | 18       |

| 1.2 Ter          | ms and Acronyms                                                       | 18       |

| 1.3 Ref          | ERENCE DOCUMENTS                                                      | 21       |

| Chapter 2.       | CCIX Overview                                                         | 22       |

| 2.1 INT          | RODUCTION                                                             | 22       |

| 2.2 Tor          | OLOGIES                                                               | 23       |

| 2.3 CC           | X Architecture Model                                                  | 24       |

| 2.3.             | Components of the CCIX Architecture                                   | 25       |

| 2.3.2            | Port Aggregation                                                      | 27       |

| 2.3.3            | CCIX Extended Data Rate Physical Layer                                | 28       |

| 2.4 CC           | X Management Framework                                                | 28       |

| 2.5 RA           | ARCHITECTURE                                                          | 28       |

| 2.6 AD           | DRESS TRANSLATION SERVICE                                             | 28       |

| 2.7 Sig          | NALING HOSTS FROM ACCELERATORS                                        | 29       |

| <b>2.8</b> Est   | ABLISHING TRUST WITH A CCIX ACCELERATOR                               | 29       |

| Chapter 3.       | Protocol Layer                                                        | 30       |

| 3.1 INT          | RODUCTION                                                             | 30       |

| 3.1.3            | CCIX Agents                                                           | 30       |

| 3.1.2            | 2 Discovery and Enumeration                                           | 32       |

| 3.1.3            | 3 Topologies                                                          | 33       |

| 3.2 ME           | SSAGE FIELDS                                                          | 34       |

| 3.2.3            | Request Message                                                       | 34       |

| 3.2.2            | 2 Snoop Message                                                       | 36       |

| 3.2.3            | Response Message                                                      | 37       |

| 3.2.4            | Field Descriptions                                                    | 37       |

| 3.3 Col          | IERENCE PROTOCOL                                                      | 42       |

| 3.3.3            | Cache States                                                          | 42       |

| 3.3.2            | ? Request Types                                                       | 44       |

| 3.3.3            | B Request Responses                                                   | 52       |

| 3.3.4            | Snoop Requests                                                        | 53       |

| February 15, 201 | 9 © 2016-2019 CCIX Consortium, Inc. ALL RIGHTS RESERVED. CONFIDENTIAL | 3 of 400 |

### **Table of Contents**

| 3.3.5 Snoo        | p Responses                                                         | 58       |

|-------------------|---------------------------------------------------------------------|----------|

| 3.3.6 Misc        | Op Encoding                                                         | 61       |

| 3.3.7 Proto       | ocol Error Report                                                   | 61       |

| 3.3.8 Requ        | est Cache State Transitions                                         | 61       |

| 3.3.9 State       | e Transitions at Snoopee                                            | 64       |

| 3.3.10 Sile       | nt Cache State Transitions                                          | 66       |

| 3.3.11 Con        | ntrolling the use of Evict and WriteEvictFull transactions          | 67       |

| 3.3.12 Sim        | ultaneous Outstanding Requests                                      | 68       |

| 3.3.13 Req        | uest to Snoop Hazard                                                | 68       |

| 3.4 TRANSACT      | ION STRUCTURE                                                       | 71       |

| 3.4.1 Requ        | est Transactions                                                    | 71       |

| 3.4.2 Snoo        | p Transactions                                                      | 75       |

| 3.5 Address,      | CONTROL, AND DATA                                                   | 77       |

| 3.5.1 Addr        | ess and Data Alignment                                              | 77       |

| 3.5.2 Requ        | est Attributes                                                      | 77       |

| 3.5.3 Perm        | nitted Memory Type for Requests                                     | 80       |

| 3.5.4 Data        | and Byte Enables                                                    | 80       |

| 3.6 ORDERING      |                                                                     | 84       |

| 3.6.1 Mult        | i-copy Atomicity                                                    | 84       |

| 3.6.2 Com         | pletion Response and Ordering                                       | 85       |

| 3.6.3 Com         | pAck                                                                | 85       |

| 3.6.4 Com         | p and Outstanding CompAck Dependency                                | 86       |

| 3.7 FLOW CON      | TROL AND PROTOCOL CREDITS                                           | 86       |

| 3.7.1 Proto       | ocol Credits                                                        | 86       |

| 3.7.2 Cred        | it Exchange                                                         | 87       |

| 3.8 MISCELLAN     | NEOUS MESSAGES                                                      | 90       |

| 3.8.1 Uncr        | edited Misc Messages                                                | 90       |

| 3.8.2 Cred        | ited Misc Messages                                                  | 90       |

| 3.8.3 ID Na       | amespace                                                            | 90       |

| 3.8.4 Exter       | nsion Fields in Misc Message                                        | 90       |

| 3.9 Error Ha      | NDLING                                                              | 90       |

| 3.9.1 Error       | Classification                                                      | 90       |

| 3.10 PACKET H     | leader                                                              | 91       |

| 3.10.1 Pac        | ket Header                                                          |          |

| February 15, 2019 | © 2016-2019 CCIX Consortium, Inc. ALL RIGHTS RESERVED. CONFIDENTIAL | 4 of 400 |

### **Table of Contents**

| 3.10.2 Message Packing                                                                | 94       |

|---------------------------------------------------------------------------------------|----------|

| 3.11 Message Formats                                                                  | 95       |

| 3.11.1 Read Request                                                                   | 95       |

| 3.11.2 Write Request                                                                  | 95       |

| 3.11.3 Response without Data                                                          |          |

| 3.11.4 Response with Data                                                             |          |

| 3.11.5 Snoop                                                                          |          |

| 3.11.6 Miscellaneous Message type                                                     |          |

| 3.11.7 Request Chaining                                                               | 100      |

| 3.11.8 Snoop Chaining                                                                 | 101      |

| 3.11.9 Extension fields                                                               | 101      |

| 3.12 Optional Features and Parameters                                                 | 104      |

| 3.12.1 CompAck Removal                                                                | 104      |

| 3.12.2 Partial Cache States                                                           | 104      |

| 3.12.3 Cache Line Size                                                                | 105      |

| 3.12.4 Address Width                                                                  | 105      |

| 3.12.5 Packet Header                                                                  | 105      |

| 3.12.6 Message Packing Enable                                                         | 105      |

| 3.12.7 Maximum Packet Size                                                            | 105      |

| 3.12.8 Summary of Properties                                                          | 105      |

| 3.13 Message Routing and Agent ID Assignment                                          | 106      |

| 3.13.1 Message Routing                                                                | 106      |

| 3.13.2 Broadcast Snoop Routing                                                        | 109      |

| 3.13.3 TxnID Assignment                                                               | 109      |

| 3.13.4 Agent ID                                                                       | 110      |

| 3.13.5 Target ID Determination                                                        | 111      |

| 3.13.6 Agent ID assignment Summary                                                    | 111      |

| 3.14 Memory Expansion                                                                 | 112      |

| 3.14.1 Concurrent Memory Expansion                                                    | 113      |

| 3.15 Port Aggregation                                                                 | 113      |

| 3.15.1 Port Aggregation Routing                                                       | 114      |

| 3.16 TERMINOLOGY                                                                      | 115      |

| 3.17 Transaction Flow Examples                                                        | 118      |

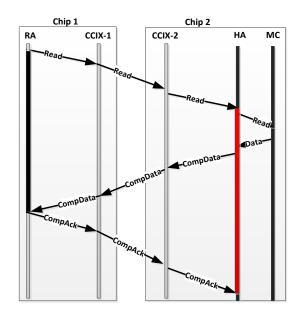

| 3.17.1 Read Request with End-to-End CompAck                                           | 118      |

| February 15, 2019 © 2016-2019 CCIX Consortium, Inc. ALL RIGHTS RESERVED. CONFIDENTIAL | 5 of 400 |

### **Table of Contents**

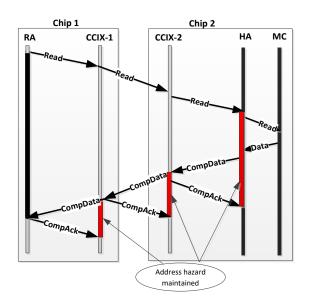

| 3.17.2            | 2 Read Request with an Early CompAck                                | 118      |

|-------------------|---------------------------------------------------------------------|----------|

| 3.17.3            | 3 Write Request                                                     | 119      |

| Chapter 4.        | CCIX Transport Layer                                                | 120      |

| 4.1 INTRO         | DDUCTION                                                            | 120      |

| 4.1.1             | CCIX Transaction Layer                                              | 122      |

| 4.1.2             | PCle Transaction Layer                                              | 123      |

| 4.1.3             | PCIe Data Link Layer                                                | 123      |

| 4.1.4             | CCIX Physical Layer                                                 | 123      |

| 4.2 TRAN          | SACTION LAYER                                                       | 124      |

| 4.2.1             | CCIX Transaction Layer Architecture                                 | 124      |

| 4.2.2             | Transaction Layer Protocol - Packet Definition                      | 125      |

| 4.2.3             | CCIX Virtual Channel                                                | 129      |

| 4.2.4             | Handling of Received TLPs                                           | 130      |

| 4.2.5             | Transaction Ordering Rules                                          | 133      |

| 4.2.6             | Virtual Channel (VC) Mechanism                                      | 133      |

| 4.2.7             | Transaction Layer Flow Control                                      | 134      |

| 4.2.8             | Data Integrity                                                      | 134      |

| 4.2.9             | Completion Timeout Mechanism                                        | 135      |

| 4.2.10            | ) Link Status Dependencies                                          | 135      |

| 4.3 CCIX          | DATA LINK LAYER                                                     | 135      |

| 4.3.1             | REPLAY_TIMER Limits for 20.0 GT/s and 25.0 GT/s                     | 135      |

| 4.3.2             | AckNak_LATENCY_TIMER Limits for 20.0 GT/s and 25.0 GT/s             | 135      |

| 4.4 CCIX          | Physical Layer Logical Block                                        | 135      |

| 4.4.1             | Introduction                                                        | 135      |

| 4.4.2             | CCIX Logical Sub-block                                              | 136      |

| 4.4.3             | Retimers                                                            | 145      |

| Chapter 5.        | Electrical PHY Layer                                                | 146      |

| 5.1 INTRO         | DDUCTION                                                            | 146      |

| 5.2 EDR           | 25-SR Electrical Specification                                      | 146      |

| 5.2.1             | General Specification                                               | 146      |

| 5.2.2             | Transmitter Specification                                           | 148      |

| 5.2.3             | Receiver Specification                                              | 152      |

| 5.2.4             | PCIe-Specific Specifications                                        | 162      |

| 5.2.5             | Reference Clock Specification                                       | 163      |

| February 15, 2019 | © 2016-2019 CCIX Consortium, Inc. ALL RIGHTS RESERVED. CONFIDENTIAL | 6 of 400 |

### **Table of Contents**

| 5.2.6 Channel Compliance                                 | 164 |

|----------------------------------------------------------|-----|

| 5.3 EDR25-LR ELECTRICAL SPECIFICATION                    |     |

| 5.3.1 General Specification                              | 172 |

| 5.3.2 Transmitter Specification                          | 174 |

| 5.3.3 Receiver Specification                             | 178 |

| 5.3.4 PCIe-Specific Specifications                       | 189 |

| 5.3.5 Reference Clock Specification                      | 189 |

| 5.3.6 Channel Compliance                                 | 191 |

| 5.4 EDR16 ELECTRICAL SPECIFICATION                       |     |

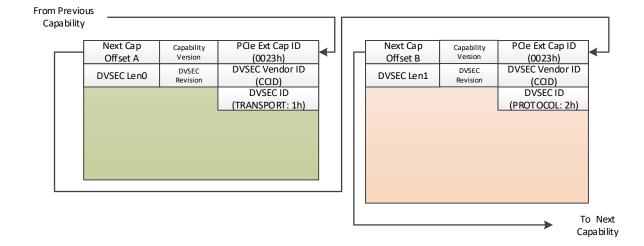

| Chapter 6. Protocol Layer and Transport Layer DVSEC      | 200 |

| 6.1 Overview                                             | 200 |

| 6.2 PROTOCOL LAYER DVSEC                                 | 201 |

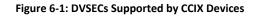

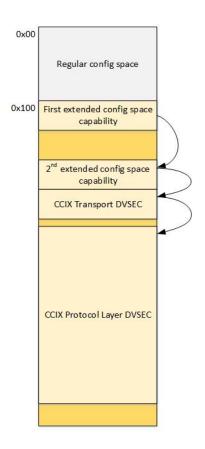

| 6.2.1 Introduction to CCIX Protocol Layer DVSEC          | 201 |

| 6.2.2 CCIX Component Structures                          | 222 |

| 6.3 TRANSPORT DVSEC                                      |     |

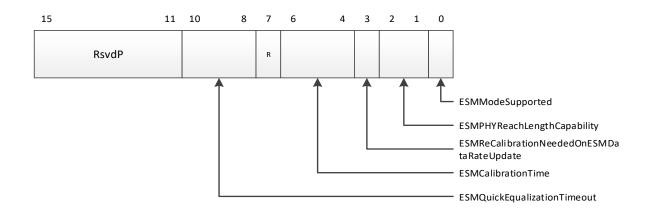

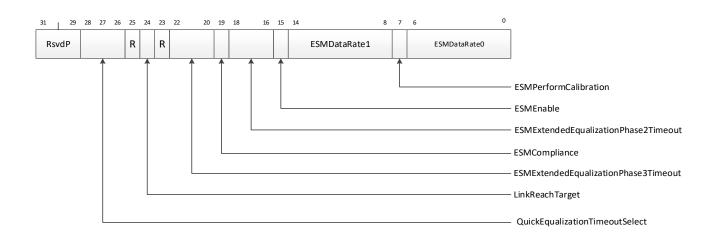

| 6.3.1 CCIXTransportCapabilities Register                 | 336 |

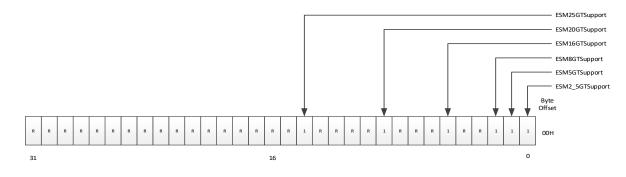

| 6.3.2 ESMMandatoryDataRateCapability Register            | 338 |

| 6.3.3 ESMOptionalDataRateCapability Register             | 339 |

| 6.3.4 ESMStatus Register                                 | 339 |

| 6.3.5 ESMControl Register                                | 340 |

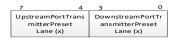

| 6.3.6 ESMLaneEqualizationControl Registers               | 346 |

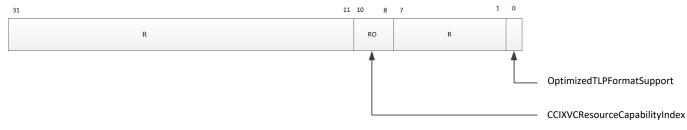

| 6.3.7 TransportLayerCapabilities Register                | 348 |

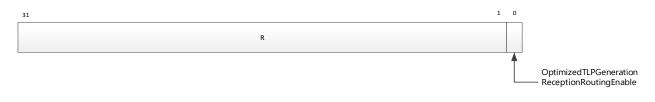

| 6.3.8 TransportLayerControl Register                     | 349 |

| 6.4 DVSEC DISCOVERY AND CONFIGURATION                    | 350 |

| 6.5 CCIX Switch Referenced Data Structures               | 351 |

| 6.6 EXAMPLES TO ILLUSTRATE PROTOCOL LAYER DVSEC USAGE    | 352 |

| 6.6.1 Simple CCIX Topology and Relevant Data Structures  | 353 |

| 6.6.2 Complex CCIX Topology and Relevant Data Structures | 360 |

| Chapter 7. CCIX RAS Overview                             |     |

| 7.1 Classification of Hardware Faults                    |     |

| 7.2 HARDWARE ERROR PROPAGATION                           |     |

| 7.3 CCIX PROTOCOL ERROR REPORTING (PER)                  |     |

| 7.3.1 CCIX PER Message Format                            |     |

10

15

20

| 7.3.2 CCIX PER Log Structures              | 373 |

|--------------------------------------------|-----|

| 7.3.3 Memory Error Type Structure          | 377 |

| 7.3.4 Cache Error Type Structure           | 380 |

| 7.3.5 ATC Error Type Structure             | 383 |

| 7.3.6 Port Error Type Structure            | 384 |

| 7.3.7 CCIX Link Error Type Structure       | 386 |

| 7.3.8 Agent Internal Error Type Structure  | 387 |

| 7.3.9 Vendor-Specific Log Info             | 388 |

| 7.4 CCIX Error Control & Status Structures | 389 |

| 7.4.1 Error Control Register Definitions   | 390 |

| 7.4.2 Device Error Control Flows           | 395 |

| hapter 8. CCIX ATS Specification           | 397 |

| 8.1 INTRODUCTION                           | 397 |

| 8.2 Address Translation Services           | 397 |

| 8.3 Invalidation Semantics                 | 398 |

| 8.4 Memory Type Information                | 398 |

| 8.4.1 Memory Type                          | 398 |

# List of Figures

| Figure 2-1: Example CCIX Direct-Attached topologies                                   | 23       |

|---------------------------------------------------------------------------------------|----------|

| Figure 2-2: Example CCIX Fully Connected topologies                                   | 24       |

| Figure 2-3: CCIX and associated PCIe layers                                           | 25       |

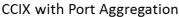

| Figure 2-4: Components of the CCIX Architecture                                       |          |

| Figure 2-5: Load distribution for address based requests across multiple CCIX Ports   | 27       |

| Figure 3-1: Illustrating CCIX Components                                              | 31       |

| Figure 3-2: Bits in MsgCredit field                                                   | 38       |

| Figure 3-3: Request to Snoop hazard                                                   | 68       |

| Figure 3-4: Coherent Read transactions with CompAck                                   |          |

| Figure 3-5: Non-coherent and IO coherent Read transactions                            | 73       |

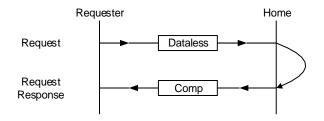

| Figure 3-6: Dataless transactions without CompAck                                     | 73       |

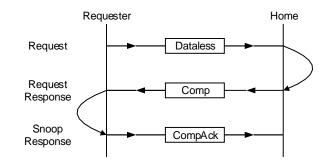

| Figure 3-7: Dataless transactions with CompAck                                        |          |

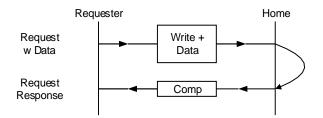

| Figure 3-8: Write transactions                                                        | 74       |

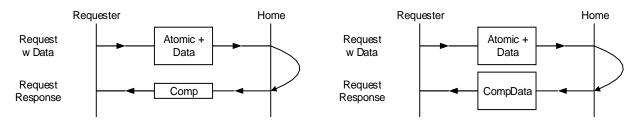

| Figure 3-9: Atomic transactions                                                       |          |

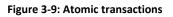

| Figure 3-10: Snoop transactions without Data response                                 | 76       |

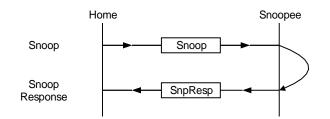

| Figure 3-11: Snoop transactions with Data response                                    | 76       |

| Figure 3-12: Data layout examples                                                     |          |

| Figure 3-13: Byte Enables Location in an 8B Data Message                              | 83       |

| Figure 3-14: Byte Enables Location in a 16B Data Message                              |          |

| Figure 3-15: Byte Enables Location in a 32B Data Message                              |          |

| Figure 3-16: Byte Enables Location in a 64B Data Message                              | 84       |

| Figure 3-17: Credit accumulation at the sender                                        |          |

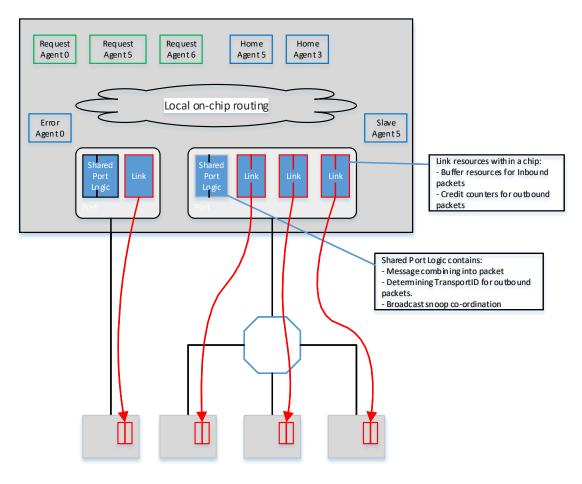

| Figure 3-18: Port, Link and Agent distribution example                                |          |

| Figure 3-19: PCIe-Compatible Header Format                                            |          |

| Figure 3-20: Optimized Header Format                                                  |          |

| Figure 3-21: Read Request Message Format                                              |          |

| Figure 3-22: Write Request Message Format                                             |          |

| Figure 3-23: Response without Data Message Format                                     |          |

| Figure 3-24: Response with Data Message Format                                        |          |

| Figure 3-25: Snoop Message Format                                                     |          |

| Figure 3-26: Credited Misc Message Format                                             |          |

| Figure 3-27: Credit Exchange Message Format                                           |          |

| Figure 3-28: NOP Message Format                                                       |          |

| Figure 3-29: PER Message Format                                                       |          |

| Figure 3-30: Fields in each Extension Type                                            |          |

| Figure 3-31: Aggregated Ports Example                                                 |          |

| Figure 3-32: A two Chip Topology with Example Internal CCIX Components                |          |

| Figure 3-33: Key Concepts and Terminology Diagram                                     |          |

| Figure 3-34: Read request with CompAck sent from Request Agent to Home Agent          |          |

| Figure 3-35: Example of a Read Transaction Flow                                       | 119      |

| February 15, 2019 © 2016-2019 CCIX Consortium, Inc. ALL RIGHTS RESERVED. CONFIDENTIAL | 9 of 400 |

| Figure 3-36: Write Request Transaction Flow                                               | 119 |

|-------------------------------------------------------------------------------------------|-----|

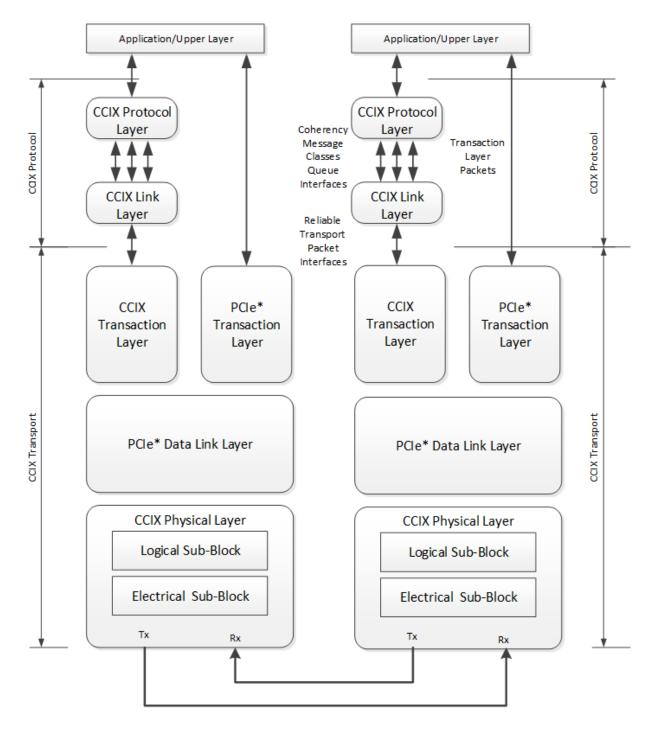

| Figure 4-1: CCIX Layering Diagram                                                         | 121 |

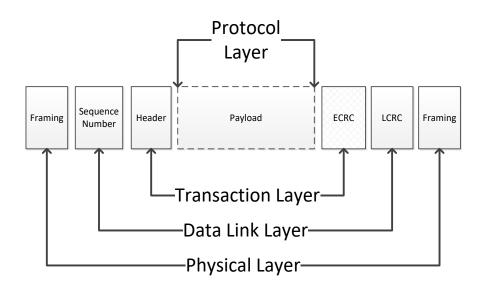

| Figure 4-2: Packet Flow through the Layers                                                | 122 |

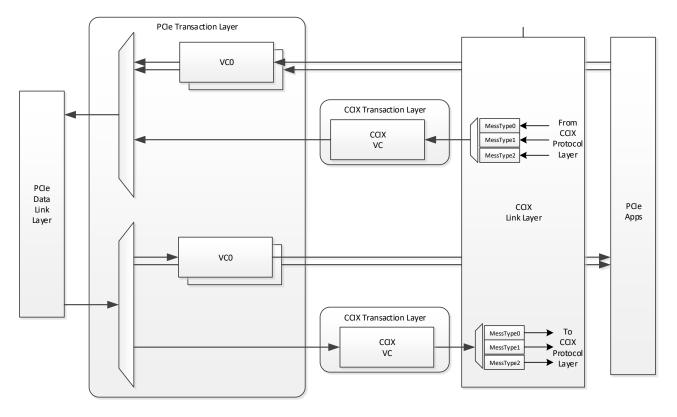

| Figure 4-3: CCIX Transaction Layer Architecture                                           | 125 |

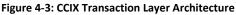

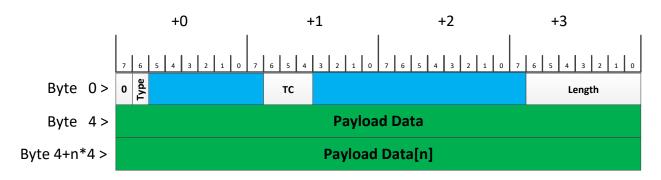

| Figure 4-4: PCIe Compatible TLP format                                                    |     |

| Figure 4-5: Optimized TLP Format                                                          | 128 |

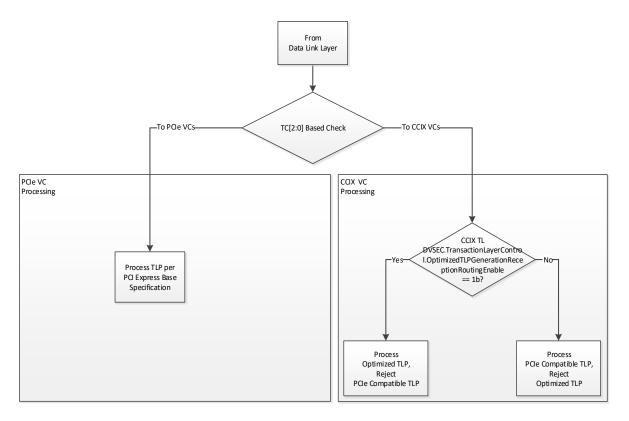

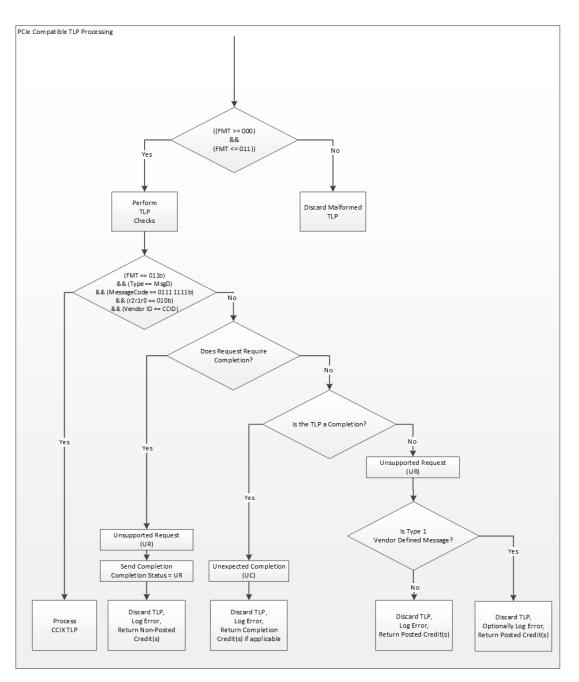

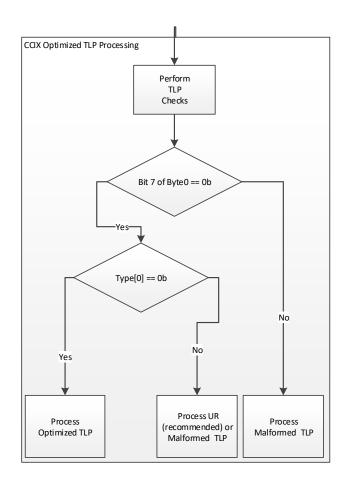

| Figure 4-6: CCIX Transaction Layer Received TLP Processing Flow                           | 130 |

| Figure 4-7: PCIe Compatible TLP Processing Flow                                           |     |

| Figure 4-8: Optimized TLP Processing Flow                                                 |     |

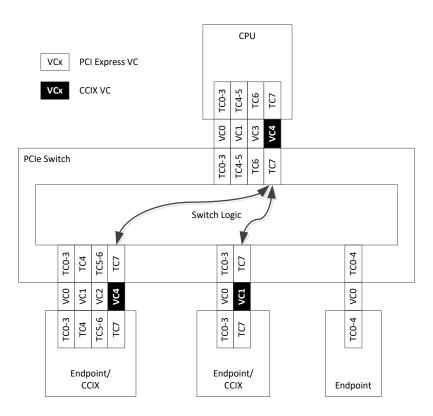

| Figure 4-9: Possible TC to VC Mapping                                                     |     |

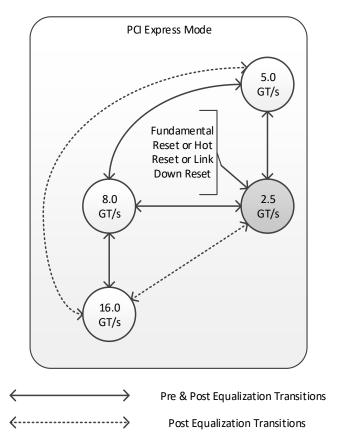

| Figure 4-10: PCI Express 16.0 GT/s Capable PHY                                            |     |

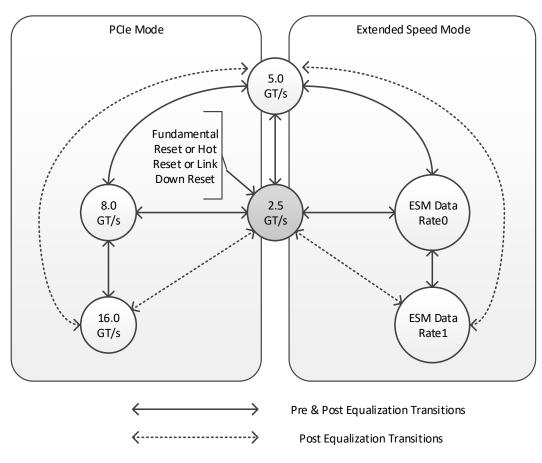

| Figure 4-11: Extended Data Rate PHY                                                       | 138 |

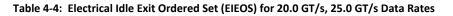

| Figure 4-12: Electrical Idle Exit Ordered Set (EIEOS) for 20.0 GT/s, 25.0 GT/s Data Rates | 144 |

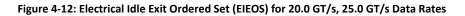

| Figure 4-13: Link-Up to ESM 25.0 GT/s through ESM 16.0 GT/s data rate                     | 144 |

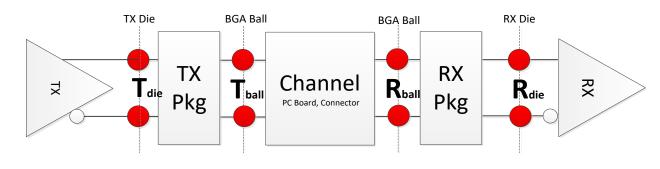

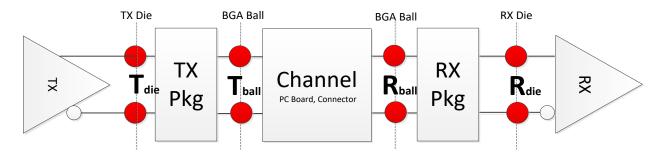

| Figure 5-1: Reference Model of EDR25-SR Link                                              |     |

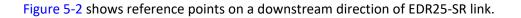

| Figure 5-2: Reference Points on a downstream direction of EDR25-SR link                   | 148 |

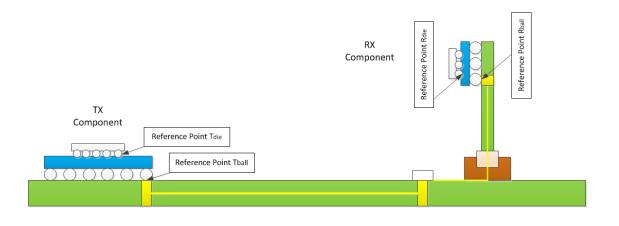

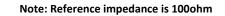

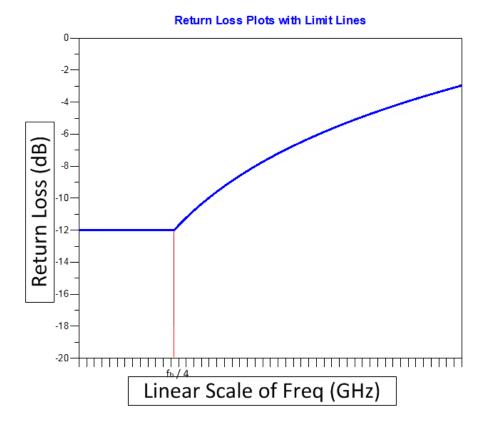

| Figure 5-3: Transmitter Differential Return Loss Mask for EDR25-SR PHY                    | 148 |

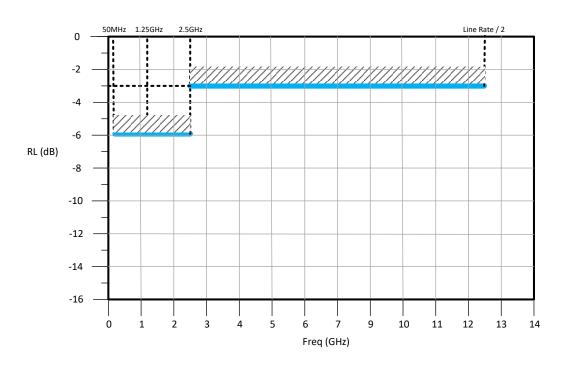

| Figure 5-4: Transmitter Common Return Loss Mask for EDR25-SR PHY                          | 149 |

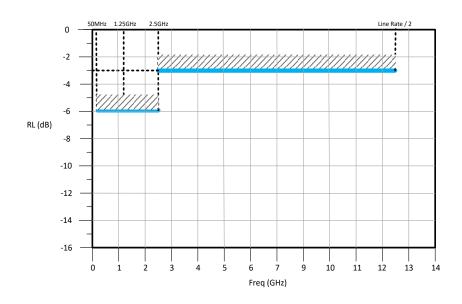

| Figure 5-5: Receiver Differential Return Loss Mask for EDR25-SR PHY                       |     |

| Figure 5-6: Common Mode Return Loss Mask for EDR25-SR PHY                                 | 153 |

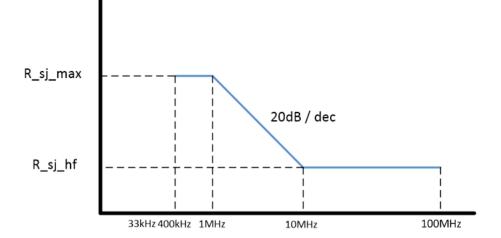

| Figure 5-7: Jitter Tolerance Mask of EDR25-SR Receiver                                    | 154 |

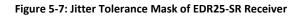

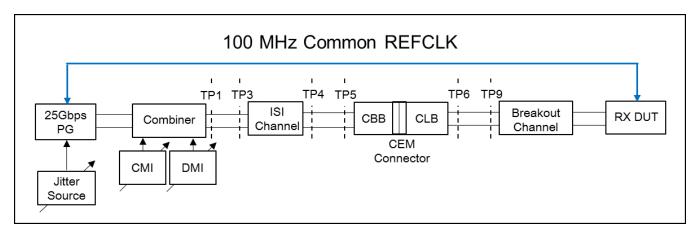

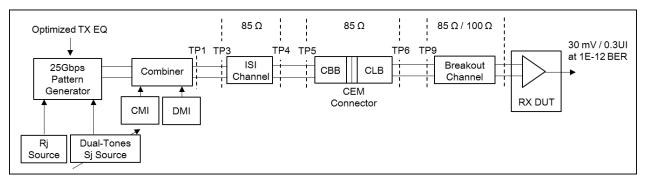

| Figure 5-8: RX Test Board Topology                                                        | 155 |

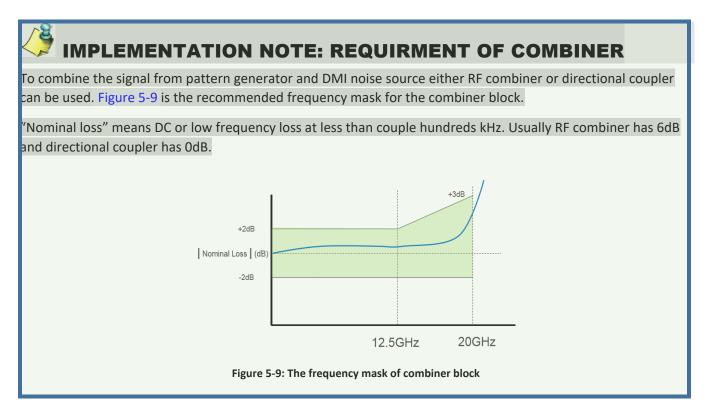

| Figure 5-9: The frequency mask of combiner block                                          | 159 |

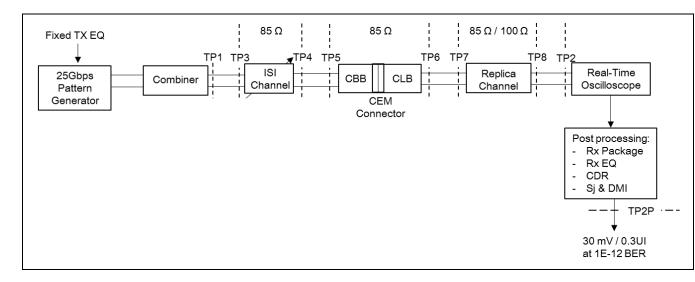

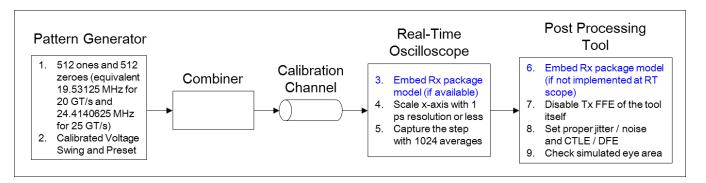

| Figure 5-10: Layout for Calibrating the Stressed Jitter Eye at ESM Rates                  |     |

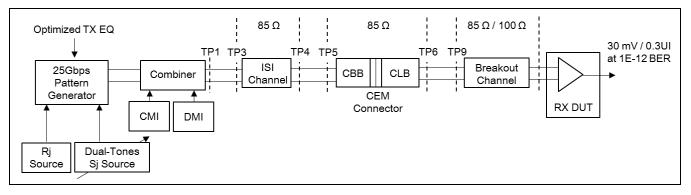

| Figure 5-11: Layout for Testing Rx DUT                                                    | 161 |

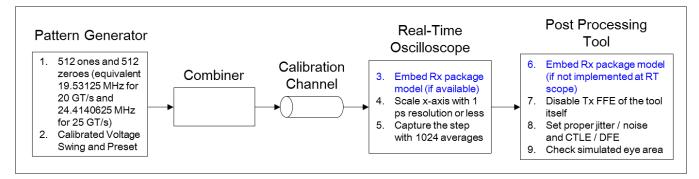

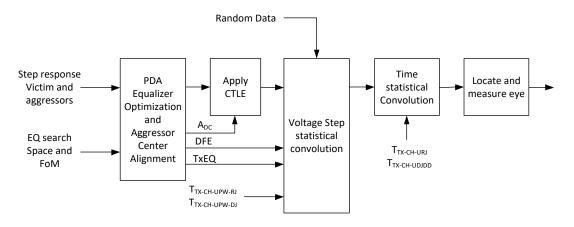

| Figure 5-12: General Flow for Using Post Processing Tool                                  | 162 |

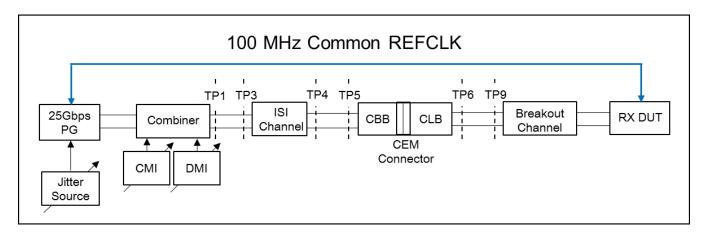

| Figure 5-13: Layout for Jitter Testing for Common Refclk Rx                               | 162 |

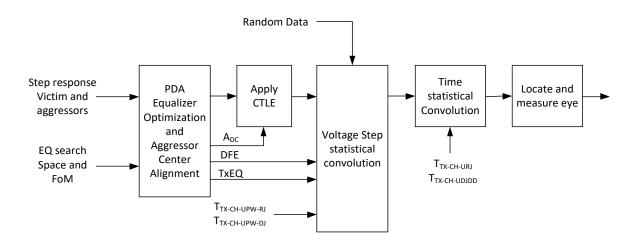

| Figure 5-14: Flow Diagram for Channel Tolerance at ESM Rates                              | 165 |

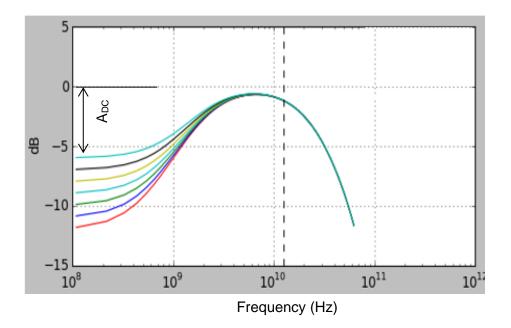

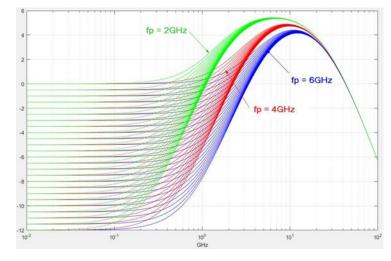

| Figure 5-15: Loss Curves for CCIX Behavioral CTLE of EDR25-SR PHY                         | 166 |

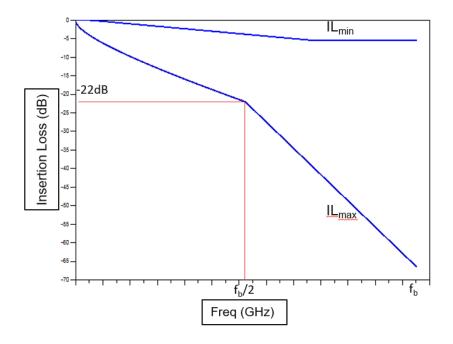

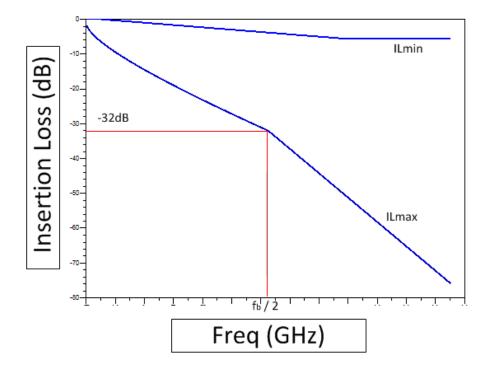

| Figure 5-16: Insertion Loss Mask for EDR25-SR Link                                        | 169 |

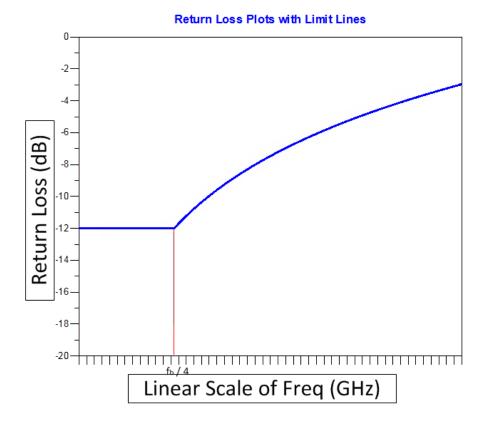

| Figure 5-17: Channel Differential Return Loss Mask for EDR25-SR Link                      | 170 |

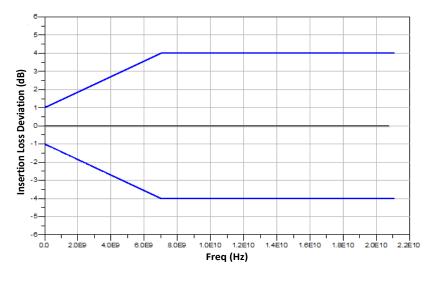

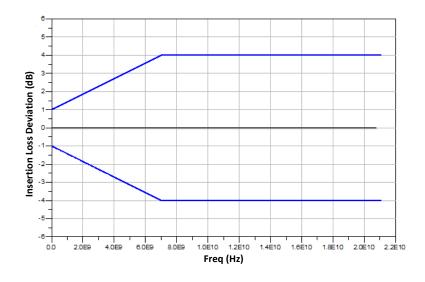

| Figure 5-18: Insertion Deviation Mask                                                     | 171 |

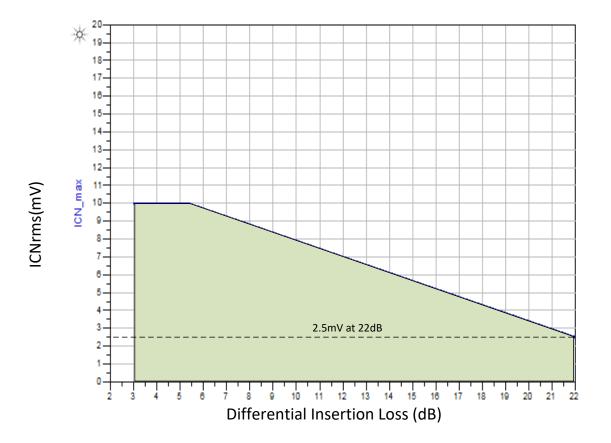

| Figure 5-19: ICN <sub>rms</sub> Mask vs Insertion Loss                                    | 172 |

| Figure 5-20: Reference Model of EDR25-LR Link                                             | 173 |

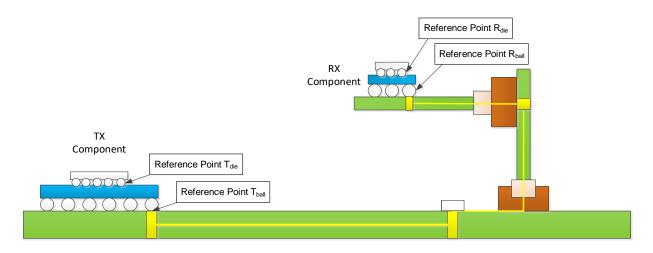

| Figure 5-21: Reference Points on a downstream direction of EDR25-LR link                  | 174 |

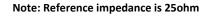

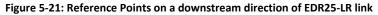

| Figure 5-22: Transmitter Differential Return Loss Mask for EDR25-LR PHY                   | 174 |

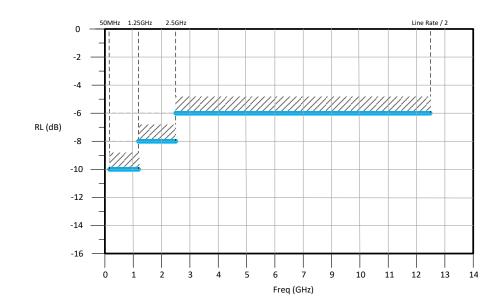

| Figure 5-23: Transmitter Common Return Loss Mask for EDR25-LR PHY                         | 175 |

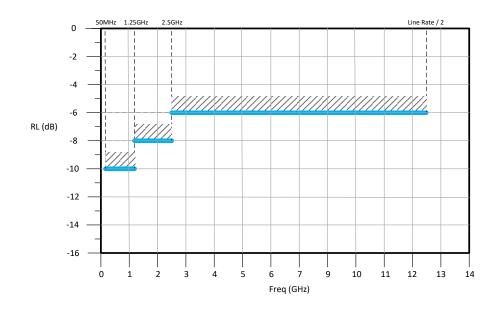

| Figure 5-24: Receiver Differential Return Loss Mask for EDR25-LR PHY                      | 178 |

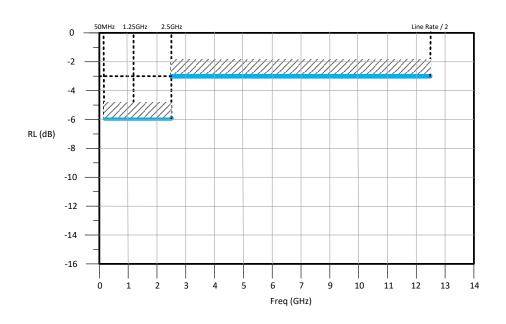

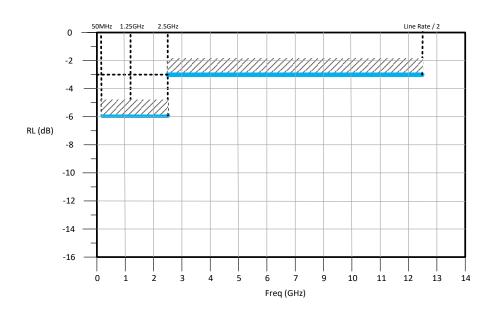

| Figure 5-25: Common Mode Return Loss Mask for EDR25-LR PHY                                | 179 |

| Figure 5-26: Jitter Tolerance Mask of EDR25-LR PHY                                        | 181 |

| Figure 5-27: RX Test Board Topology for EDR25-LR                                          | 182 |

| Figure 5-28: The frequency mask of combiner block                                         |     |

| Figure 5-29: Layout for Calibrating the Stressed Jitter Eye at ESM Rates                  |     |

| Figure 5-30: Layout for Testing Rx DUT                                                    |     |

| Figure 5-31: General Flow for Using Post Processing Tool                                  |     |

|                                                                                           |     |

| Figure 5-32: Layout for Jitter Testing for Common Refclk Rx                            | 189 |

|----------------------------------------------------------------------------------------|-----|

| Figure 5-33: Flow Diagram for Channel Tolerancing at ESM Rates                         | 191 |

| Figure 5-34: Loss Curves for CCIX Behavioral CTLE                                      | 193 |

| Figure 5-35: Insertion Loss Mask for EDR25-LR                                          |     |

| Figure 5-36: Channel Differential Return Loss Mask for EDR25-LR Link                   | 197 |

| Figure 5-37: Insertion Deviation Mask for EDR25-LR PHY                                 | 198 |

| Figure 5-38: ICN <sub>rms</sub> mask vs Insertion Loss                                 | 199 |

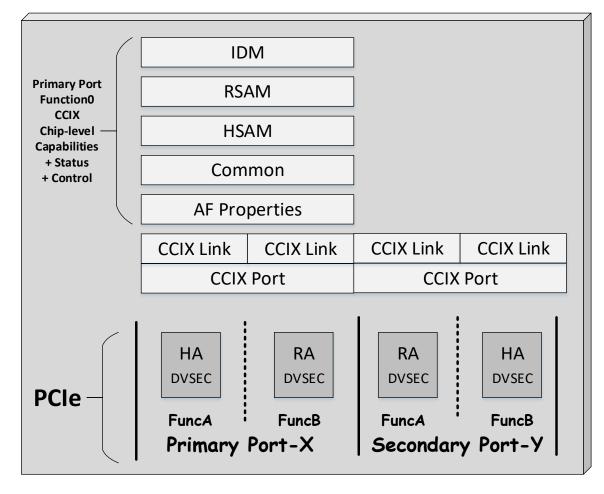

| Figure 6-1: DVSECs Supported by CCIX Devices                                           | 200 |

| Figure 6-2: CCIX Protocol Layer DVSEC located in PCIe Configuration Space              | 201 |

| Figure 6-3: CCIX Protocol Layer DVSEC structure types                                  | 202 |

| Figure 6-4: CCIX Protocol Layer DVSEC structures over various PCIe Ports and Functions | 203 |

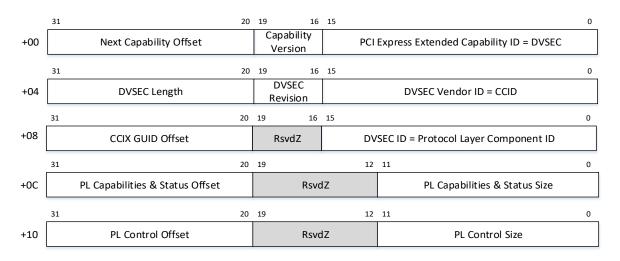

| Figure 6-5: CCIX Protocol Layer DVSEC Header                                           |     |

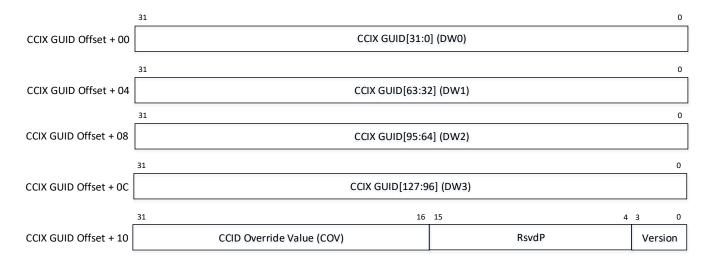

| Figure 6-6: CCID Override Structure                                                    | 206 |

| Figure 6-7: Sequence of CCIX Protocol Layer Component Structures                       |     |

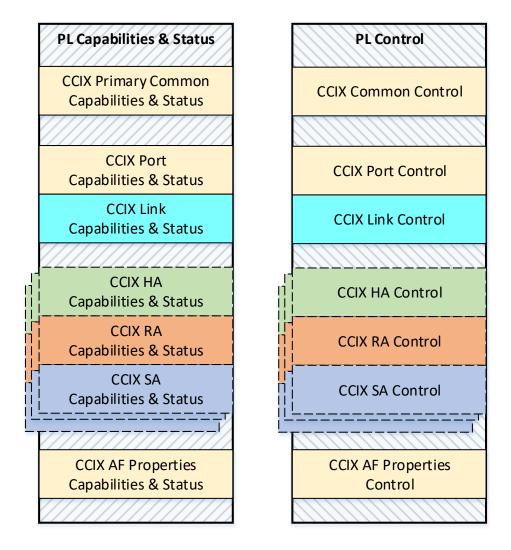

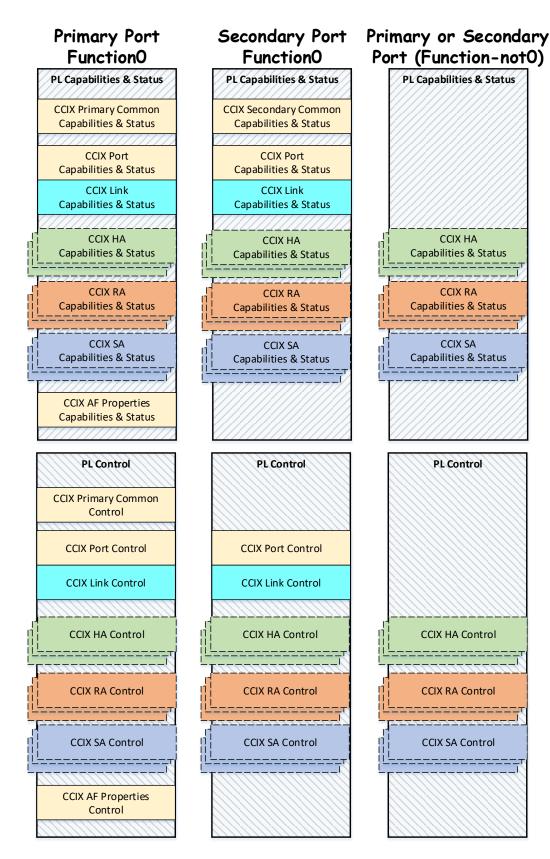

| Figure 6-8: Structures for multi-Port CCIX Devices                                     | 211 |

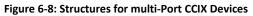

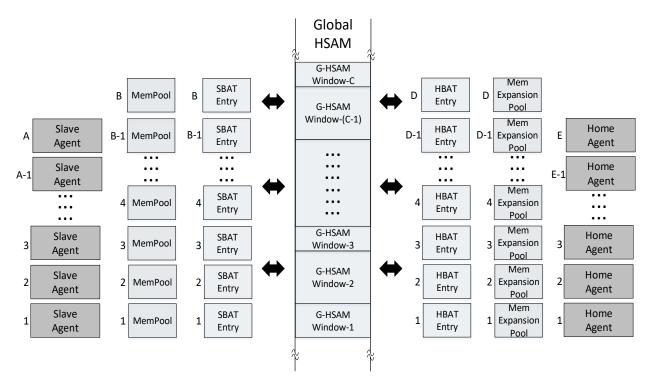

| Figure 6-9: CCIX Component's Capabilities & Status Registers                           | 212 |

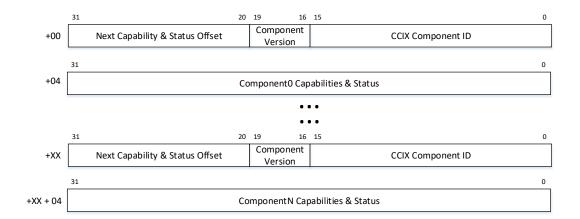

| Figure 6-10: CCIX Component's Control Registers                                        | 212 |

| Figure 6-11: Version Numbers and their impact on data structure definition             | 214 |

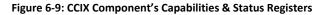

| Figure 6-12: G-RSAM and its relation to HAs, MemPools, and HBAT Entries                | 215 |

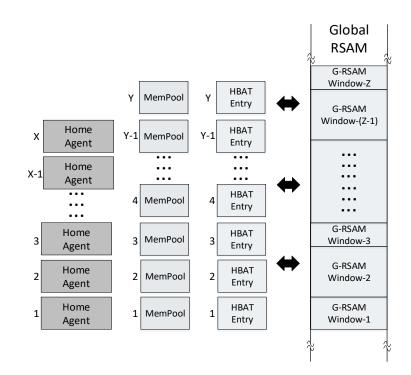

| Figure 6-13: G-HSAM and its relation to HAs with Memory Expansion Pools, and SAs       | 216 |

| Figure 6-14: Common Capabilities & Status structure                                    | 219 |

| Figure 6-15: CCIX Device SAM/IDM Tables                                                |     |

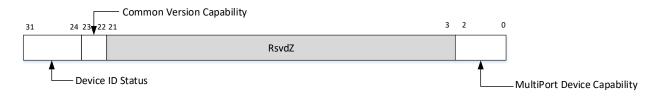

| Figure 6-16: ComnCapStat1 Register at Byte Offset-04h                                  | 222 |

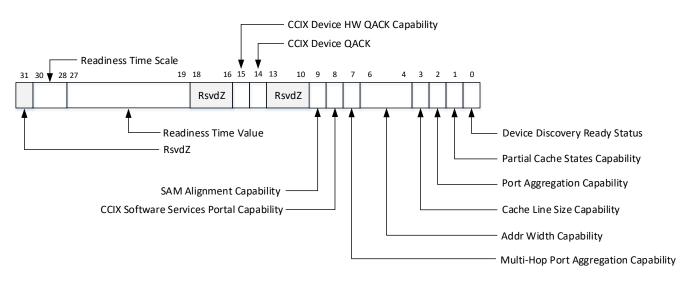

| Figure 6-17: ComnCapStat2 Register at Byte Offset-08h                                  | 224 |

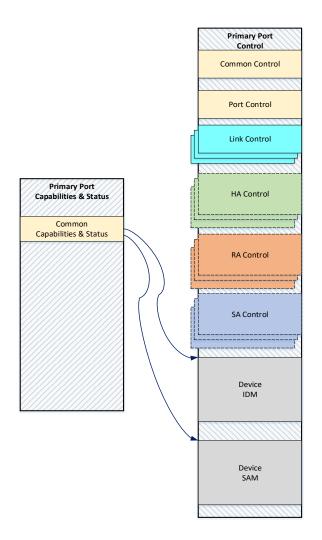

| Figure 6-18: Primary CCIX Port Common Control Structure                                | 231 |

| Figure 6-19: ComnCntl1 Register at Byte Offset-04h                                     | 232 |

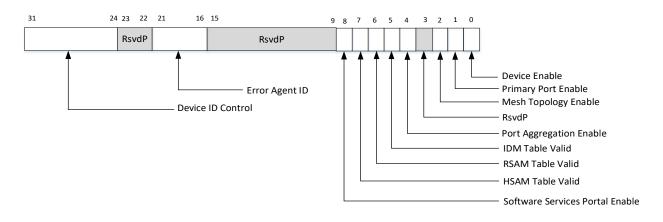

| Figure 6-20: ComnCntl2 Register at Byte Offset-08h                                     | 237 |

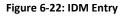

| Figure 6-21: IDM Table                                                                 | 242 |

| Figure 6-22: IDM Entry                                                                 | 242 |

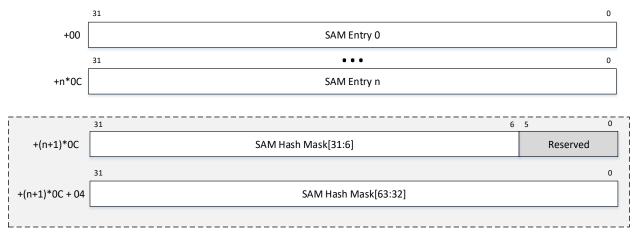

| Figure 6-23: SAM Table                                                                 | 247 |

| Figure 6-24: SAM Entry                                                                 | 247 |

| Figure 6-25: Aggregated Port Selection Function                                        | 252 |

| Figure 6-26: Memory Pool Capabilities & Status structure                               | 255 |

| Figure 6-27: Memory Pool Entry Capabilities & Status Registers                         | 255 |

| Figure 6-28: BAT Control structure                                                     | 259 |

| Figure 6-29: BAT Base Address Type Entry (BATBaseAddrTypeEntry) Control Registers      | 259 |

| Figure 6-30: BAT Fixed Offset Type Control Entry                                       | 261 |

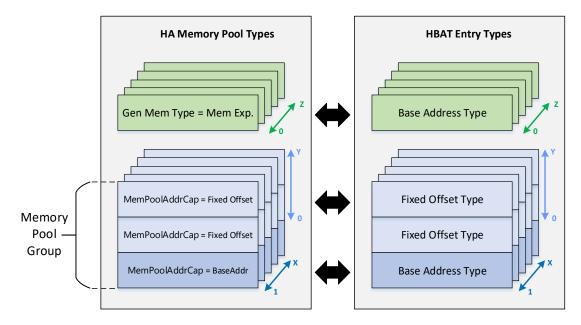

| Figure 6-31: Relation between HA Memory Pools and HBAT Entries                         | 263 |

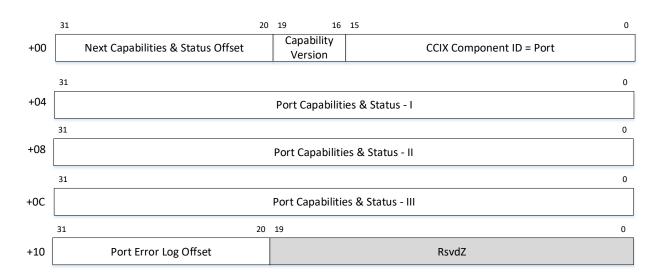

| Figure 6-32: CCIX Port Capabilities & Status Registers                                 | 265 |

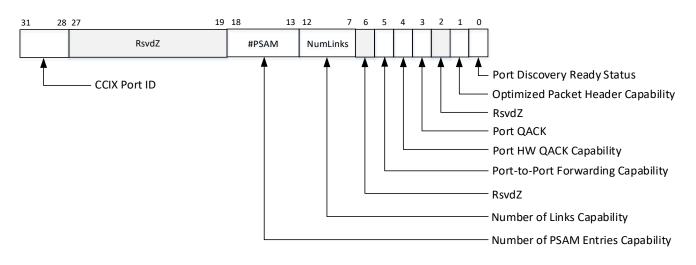

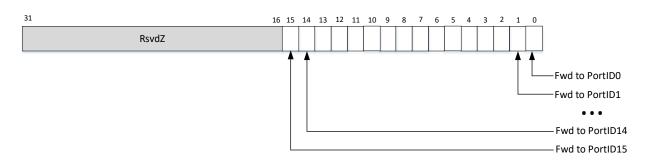

| Figure 6-33: PortCapStat1 Register at Byte Offset-04h                                  | 265 |

| Figure 6-34: PortCapStat2 Register at Byte Offset-08h                                  | 269 |

| Figure 6-35: PortCapStat3 Register at Byte Offset-0Ch                                  | 270 |

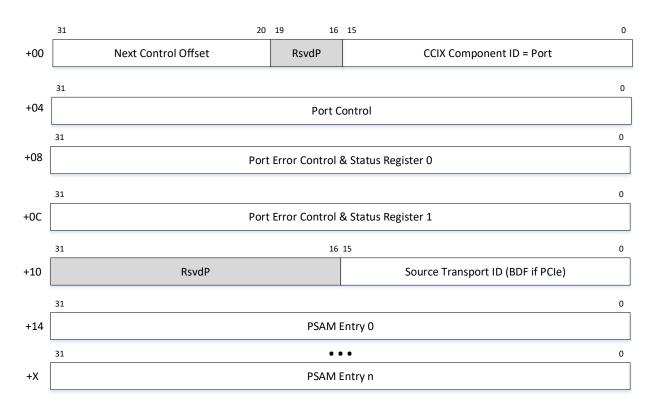

| Figure 6-36: Layout of the CCIX Port Control Structure                                 | 272 |

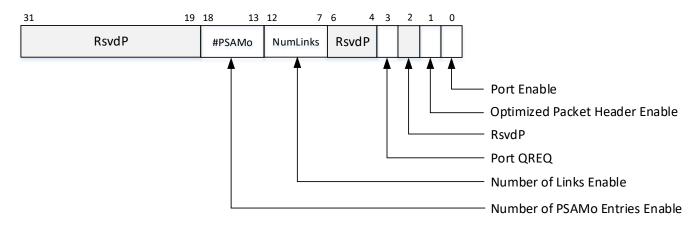

| Figure 6-37: PortCntl Register at Byte Offset-04h                                      | 272 |

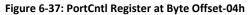

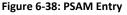

| Figure 6-38: PSAM Entry                                                                | 274 |

|                                                                                        |     |

### List of Figures

| Figure 6-39: CCIX Link Capabilities & Status Structure                   | 276 |

|--------------------------------------------------------------------------|-----|

| Figure 6-40: CCIX Link Capabilities & Status Register at Byte Offset-04h | 277 |

| Figure 6-41: LinkSendCap Registerat Byte Offset-08h                      | 280 |

| Figure 6-42: LinkRcvCap Register at Byte Offset-0Ch                      |     |

| Figure 6-43: LinkCreditMiscMsgCap Register at Byte Offset-10h            | 283 |

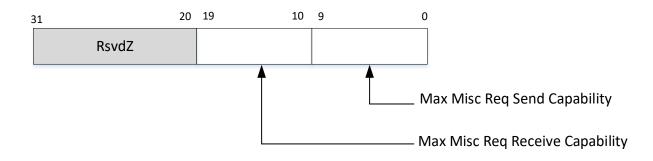

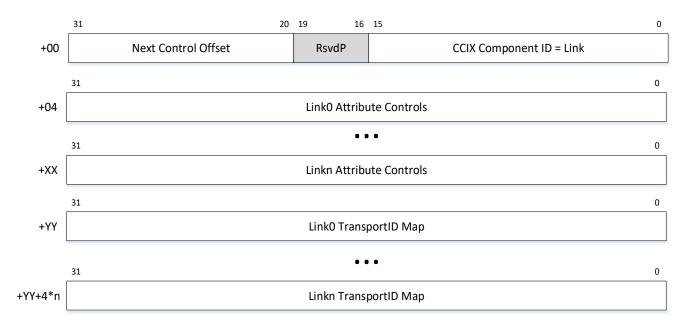

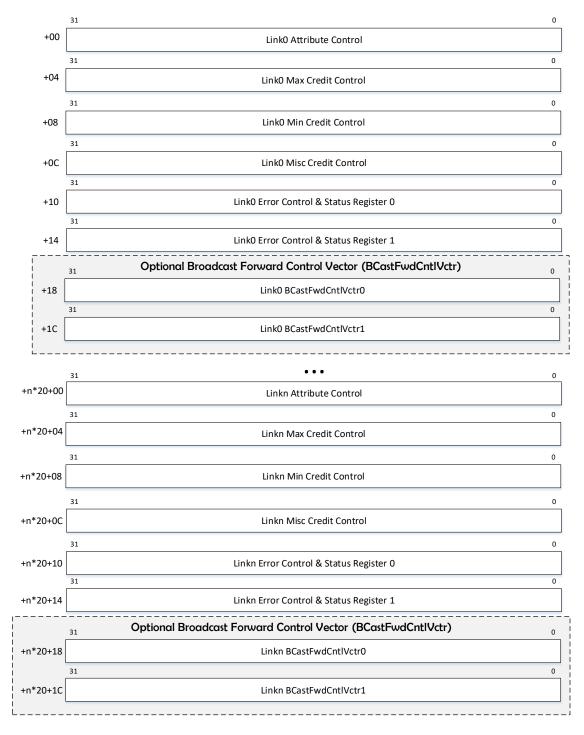

| Figure 6-44: CCIX Link Control structure                                 | 285 |

| Figure 6-45: CCIX Link Attribute Control Entries                         | 286 |

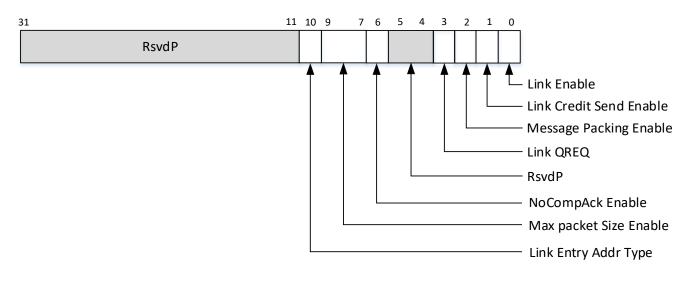

| Figure 6-46: LinkAttrCntl Entry at Byte Offset-00h                       | 287 |

| Figure 6-47: LinkMaxCreditCntl Entry at Byte Offset-04h                  | 290 |

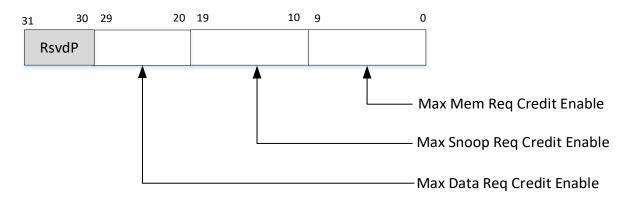

| Figure 6-48: LinkMinCreditCntl Entry at Byte Offset-08h                  | 292 |

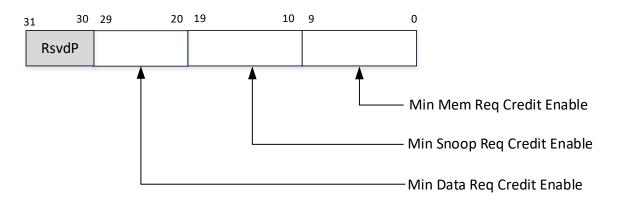

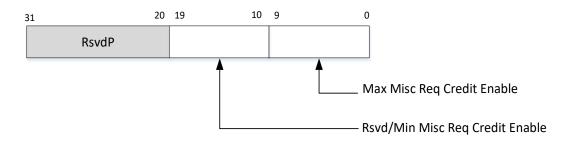

| Figure 6-49: LinkMiscCreditCntl Entry at Byte Offset-0Ch                 | 293 |

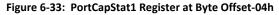

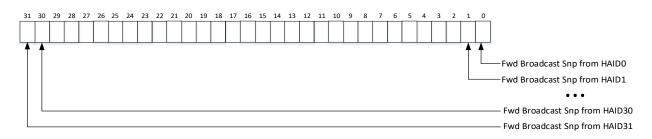

| Figure 6-50: BCastFwdCntlVctr0                                           | 295 |

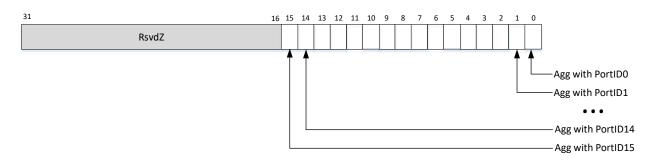

| Figure 6-51: BCastFwdCntlVctr1                                           | 295 |

| Figure 6-52: LinkTransportIDMapEntry Register                            | 296 |

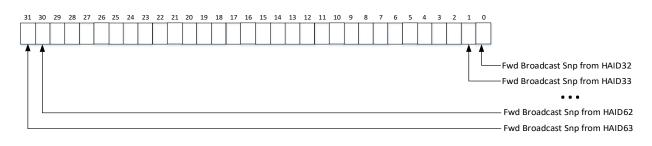

| Figure 6-53: Home Agent Capabilities & Status Structure                  | 297 |

| Figure 6-54: HACapStat Register at Byte Offset-04h                       | 298 |

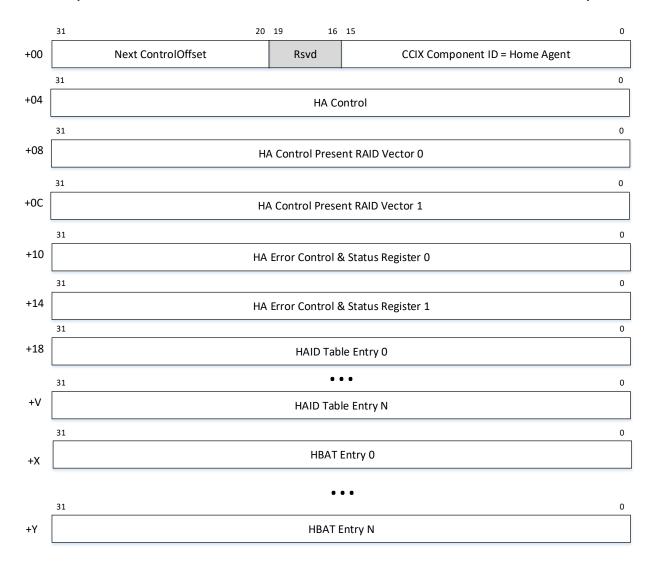

| Figure 6-55: Home Agent Control Registers                                |     |

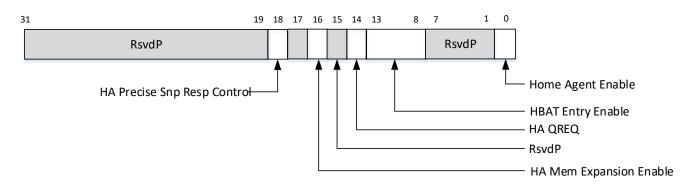

| Figure 6-56: HACntl Register at Byte Offset-04h                          |     |

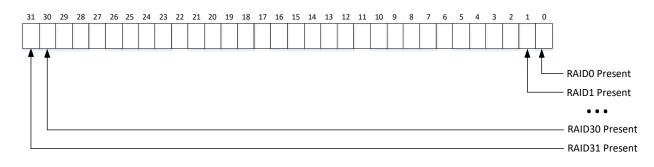

| Figure 6-57: HACntlPresentRAIDVctr0 Register                             |     |

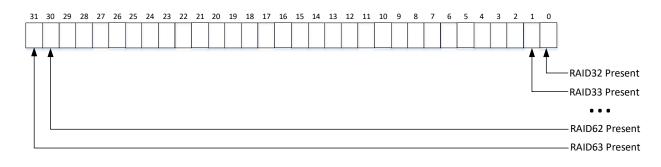

| Figure 6-58: HACntlPresentRAIDVctr1 Register                             |     |

| Figure 6-59: HAIDTblEntry0 Register at Byte Offset-18h                   |     |

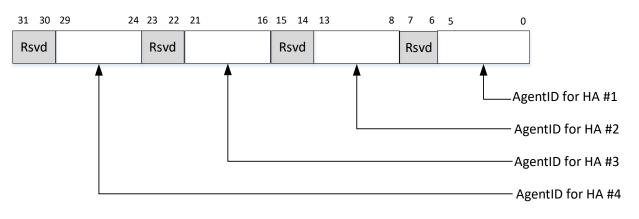

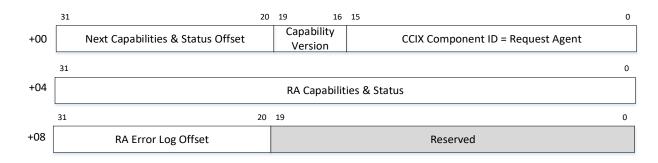

| Figure 6-60: RA Capabilities & Status Structure                          |     |

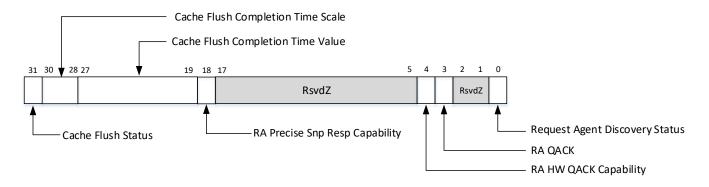

| Figure 6-61: RACapStat Register at Byte Offset-04h                       |     |

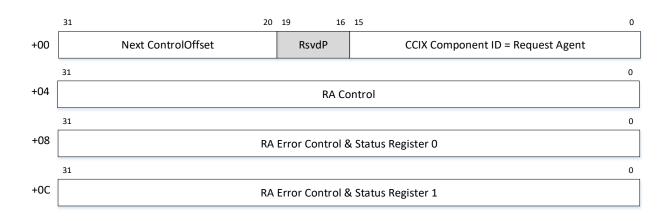

| Figure 6-62: Request Agent Control Registers                             | 315 |

| Figure 6-63: RACntl Register at Byte Offset-04h                          |     |

| Figure 6-64: Slave Agent Capabilities & Status Structure                 |     |

| Figure 6-65: SACapStat Register at Byte Offset-04h                       | 319 |

| Figure 6-66: Slave Agent Control Structure                               |     |

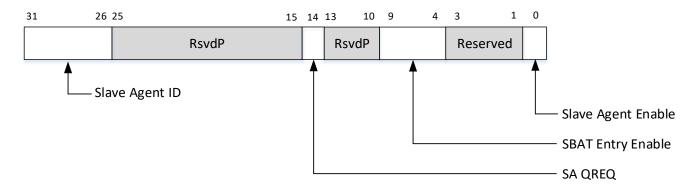

| Figure 6-67: SACntl Register at Byte Offset-04h                          | 324 |

| Figure 6-68: AF Properties Capabilities & Status Structure               | 326 |

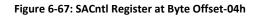

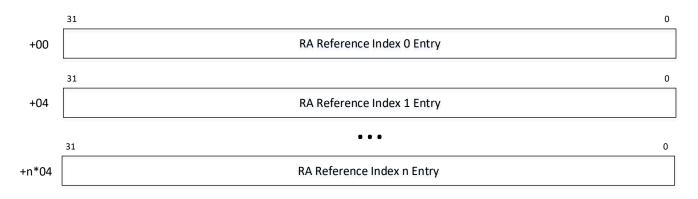

| Figure 6-69: RA Reference Index Structure                                | 328 |

| Figure 6-70: RA Reference Index Entry                                    | 328 |

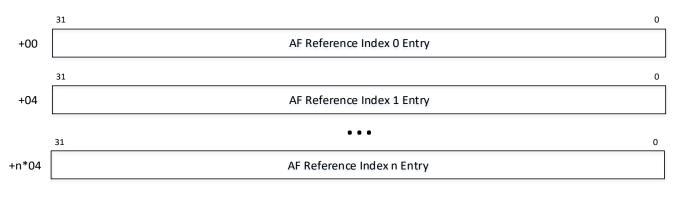

| Figure 6-71: AF Reference Index Structure                                | 329 |

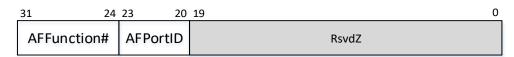

| Figure 6-72: AF Reference Index Entry                                    |     |

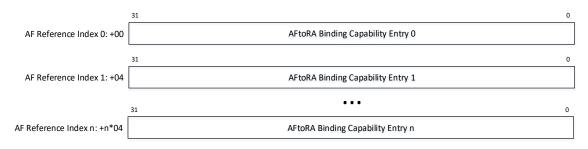

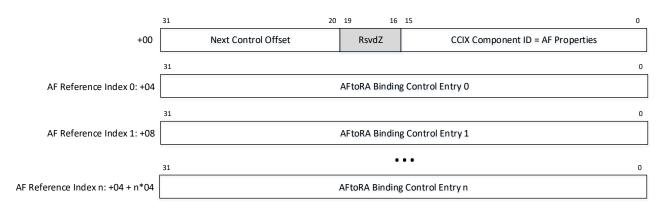

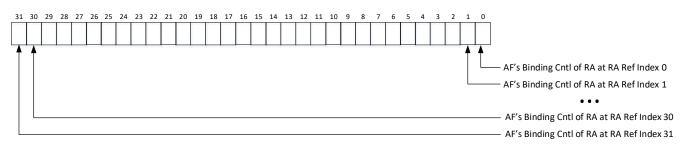

| Figure 6-73: AF to RA Binding Capability Structure                       |     |

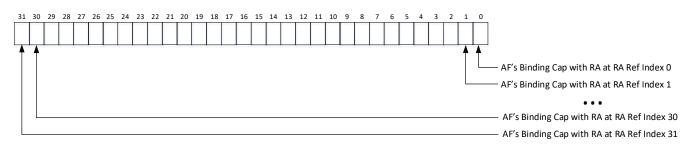

| Figure 6-74: AF to RA Binding Capability Entry                           |     |

| Figure 6-75: AF Properties Control Structure                             |     |

| Figure 6-76: AF to RA Binding Control Entry                              |     |

| Figure 6-77: CCIX Transport DVSEC                                        |     |

| Figure 6-78: CCIXTransportCapabilities Register                          |     |

| Figure 6-79: ESMMandatoryDataRateCapability Register                     |     |

| Figure 6-80: ESMStatus Register                                          |     |

| Figure 6-81: ESMControl Register                                         |     |

| Figure 6-82: ESMLaneEqualizationControl Registers                        |     |

| Figure 6-83: ESMLaneEqualizationControl Register Entry                   |     |

|                                                                          |     |

| Figure 6-84: TransactionLayerCapabilities Register                                       | 348 |

|------------------------------------------------------------------------------------------|-----|

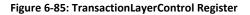

| Figure 6-85: TransactionLayerControl Register                                            | 349 |

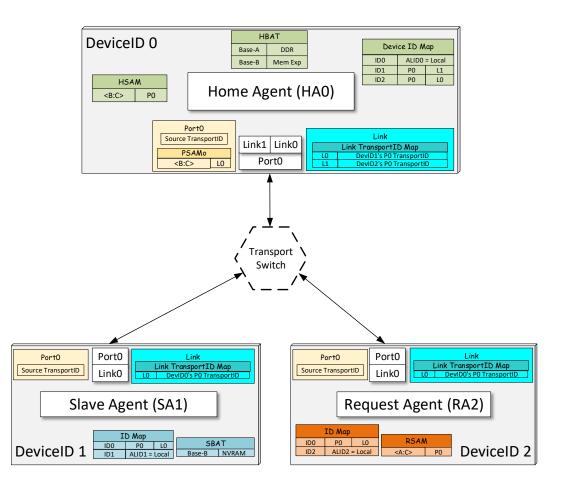

| Figure 6-86: Example simple CCIX Topology with relevant data structures                  | 353 |

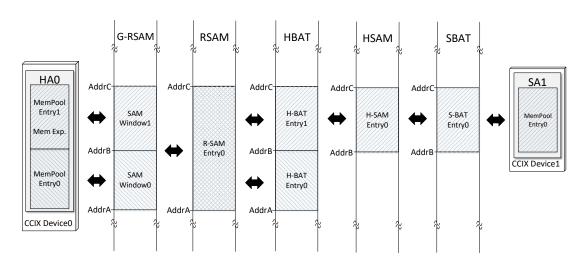

| Figure 6-87: SAM Windows and associated data structures for simple CCIX Topology example | 359 |

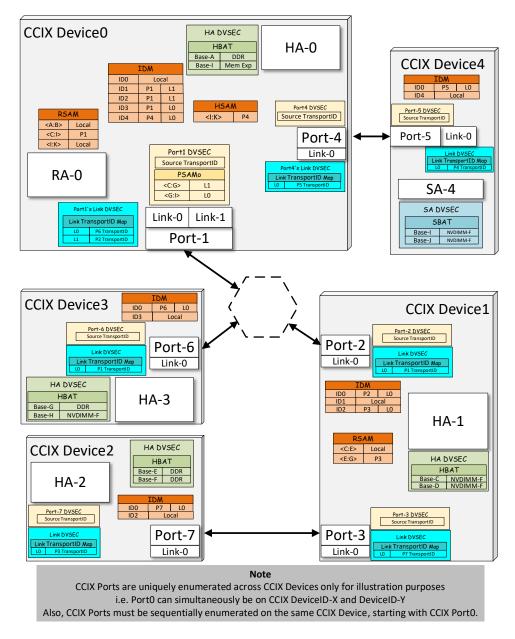

| Figure 6-88: Example complex CCIX Topology with relevant data structures                 | 360 |

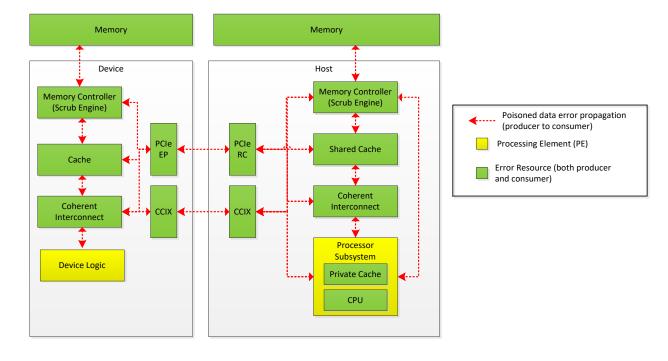

| Figure 7-1: Example Error Propagation Flow on CCIX devices                               | 365 |

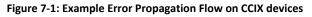

| Figure 7-2: CCIX Protocol Error Reporting (PER) Message Format                           | 367 |

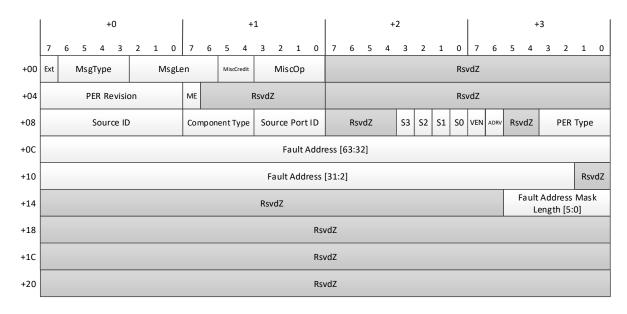

| Figure 7-3: CCIX PER Log Structure Format                                                | 374 |

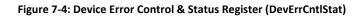

| Figure 7-4: Device Error Control & Status Register (DevErrCntlStat)                      | 390 |

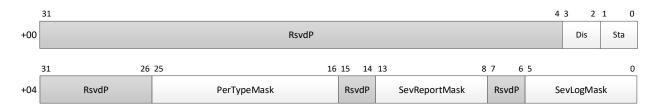

| Figure 7-5: Component Error Control & Status Registers (*ErrCntlStat0 and *ErrCntlStat1) | 390 |

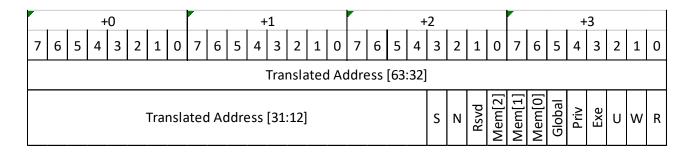

| Figure 8-1: ATS Translation Completion with Memory Attributes Format                     | 398 |

# List of Tables

| Table 3-1: Request message fields                                                          | 35        |

|--------------------------------------------------------------------------------------------|-----------|

| Table 3-2: Snoop message fields                                                            | 36        |

| Table 3-3: Response Message Fields                                                         | 37        |

| Table 3-4: MsgType field encoding                                                          | 38        |

| Table 3-5: MsgLen field encoding                                                           |           |

| Table 3-6: SnpCast field encoding                                                          |           |

| Table 3-7: Memory type encoding in ReqAttr field                                           | 40        |

| Table 3-8: Data Size encoding in ReqAttr field                                             | 41        |

| Table 3-9: ReqOp value for Requests                                                        | 51        |

| Table 3-10: AtomicLoad and AtomicStore Sub-opcodes                                         |           |

| Table 3-11: Endianess of Operations                                                        | 52        |

| Table 3-12: RespOp and Resp field encodings in Request response                            | 53        |

| Table 3-13: Snoop Type and Permitted Snoopee Transitions                                   | 56        |

| Table 3-14: SnpOp values for Snoops                                                        | 57        |

| Table 3-15: Request types and the corresponding Snoop requests                             | 58        |

| Table 3-16: RespOp and Resp field encodings in Snoop Response                              | 59        |

| Table 3-17: Misc message Opcodes                                                           | 61        |

| Table 3-18: Cache State Transitions at Requester Cache for Read Requests                   | 62        |

| Table 3-19: Cache State Transitions at Requester Cache for Dataless Requests               | 63        |

| Table 3-20: Cache State Transitions at Requester Cache for Write Requests                  | 63        |

| Table 3-21: Cache State Transitions at Requester Cache for Atomic Requests                 | 64        |

| Table 3-22: Cache state transitions at the Snoopee in response to a Snoop                  | 65        |

| Table 3-23: Legal Silent Cache State Transitions at Requester Cache                        | 66        |

| Table 3-24: Forwarded Snoop Response when Request Data is Transferred and Request Canceled | 70        |

| Table 3-25: RespErr Field Encoding.                                                        | 91        |

| Table 3-26: PCIe Compatible Header Field Description, CCIX Layer Use                       | 92        |

| Table 3-27: Optimized Header Field Description, PCIe Layer Use                             | 93        |

| Table 3-28: Optimized Header Field Description, CCIX Layer Use                             | 93        |

| Table 3-29: Packet Header Length Field Encoding                                            | 93        |

| Table 3-30: Ext and ExtType Field Description                                              | 102       |

| Table 3-31: Extension Field Description                                                    |           |

| Table 3-32: Protocol Properties and their Permitted Values                                 | 105       |

| Table 3-33: Routing of Messages                                                            | 106       |

| Table 3-34: Example IDM Table                                                              | 108       |

| Table 3-35: SrcID and TgtID Assignment Rules                                               | 111       |

| Table 4-1: Type [0] Field Values                                                           | 127       |

| Table 4-2: CCIX PHY Types & Operating Modes                                                | 138       |

| Table 4-3: PCI Express TSx Symbol 4 Description                                            | 143       |

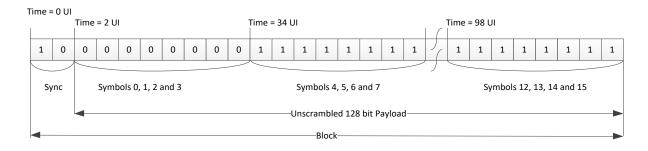

| Table 4-4: Electrical Idle Exit Ordered Set (EIEOS) for 20.0 GT/s, 25.0 GT/s Data Rates    | 144       |

| Table 5-1: CCIX PHY Types and Operating Modes                                              | 146       |

| February 15, 2019 © 2016-2019 CCIX Consortium, Inc. ALL RIGHTS RESERVED. CONFIDENTIAL      | 14 of 400 |

| Table 5-2: The Electrical Specification at Reference Point T <sub>ball</sub>                    | 150 |

|-------------------------------------------------------------------------------------------------|-----|

| Table 5-3: The Jitter Specification at Reference Point T <sub>ball</sub>                        | 151 |

| Table 5-4: Common receiver parameters                                                           | 153 |

| Table 5-5: Jitter Tolerance Specification                                                       | 154 |

| Table 5-6: Calibration Channel IL Limits for CCIX-SR                                            | 156 |

| Table 5-7: Calibration Parameters for Jitter Tolerance Test                                     | 157 |

| Table 5-8: The gain of adapted CTLE at 2.1GHz (dB)                                              |     |

| Table 5-9: Refclk Specification                                                                 | 163 |

| Table 5-10: Common Refclk PLL and CDR Characteristics for EDR25-SR PHY                          |     |

| Table 5-11: Reference Receiver Parameters for Channel Compliance                                |     |

| Table 5-12: Package Model Capacitances                                                          |     |

| Table 5-13: Jitter/Voltage Parameter of Behavioral Transmitter                                  |     |

| Table 5-14: Frequency Domain Channel Characteristic                                             |     |

| Table 5-15: Insertion Loss Break-Down                                                           |     |

| Table 5-16: Channel Integrated Crosstalk Aggressor Parameters                                   | 171 |

| Table 5-17: The Electrical Specification at reference point T <sub>ball</sub>                   |     |

| Table 5-18: The Jitter Specification at reference point T <sub>ball</sub>                       |     |

| Table 5-19: Common Receiver Parameters                                                          | 179 |

| Table 5-20: The Jitter Tolerance Specification                                                  |     |

| Table 5-21: Calibration Channel IL Limits for CCIX-LR                                           |     |

| Table 5-22: Calibration Parameters for Jitter Tolerance Test                                    |     |

| Table 5-23: The gain of adapted CTLE at 2.1GHz (dB)                                             |     |

| Table 5-24: Refclk specification                                                                |     |

| Table 5-25: Common Refclk PLL and CDR Characteristics for 20 GT/s and 25 GT/s                   | 191 |

| Table 5-26: Reference Receiver Parameters for Channel Compliance                                | 192 |

| Table 5-27: Package Model Capacitances                                                          | 194 |

| Table 5-28: Jitter/Voltage Parameter of behavioral transmitter                                  |     |

| Table 5-29: Channel Characteristic                                                              | 194 |

| Table 5-30: Insertion Loss Break-Down                                                           |     |

| Table 5-31: Channel Integrated Crosstalk Aggressor Parameters                                   | 198 |

| Table 6-1: CCIX PL DVSEC Header Register fields at Byte Offset 04h                              | 205 |

| Table 6-2: CCIX PL DVSEC Header Register fields at Byte Offset 08h                              | 206 |

| Table 6-3: CCID Override Structure Register fields from Byte Offset 00h through Byte Offset 0Ch | 207 |

| Table 6-4: CCID Override Structure Register fields at Byte Offset 10h                           | 207 |

| Table 6-5: CCIX PLCapStatPtr Register at Byte Offset-0Ch                                        | 208 |

| Table 6-6: CCIX PLCntlPtr Register at Byte Offset-10h                                           | 209 |

| Table 6-7: Capabilities & Status Version field                                                  | 213 |

| Table 6-8: CCIX Component ID Encodings                                                          | 213 |

| Table 6-9: IDMPtr Register fields                                                               | 219 |

| Table 6-10: SAMPtr Register /Fields                                                             | 220 |

| Table 6-11: SoftwareServicesPortal Register                                                     | 221 |

| Table 6-12: ComnCapStat1 Register fields at Byte Offset-04h                                     | 223 |

| Table 6-13: ComnCapStat2 Register fields at Byte Offset-08h                                     | 224 |

| Table 6-14: ComnCntl1 Register fields at Byte Offset-04h                                        | 232 |

| Table 6-15: ComnCntl2 Register fields at Byte Offset-08h                                        | 237 |

|                                                                                                 |     |

| Table 6-16: SnpReqHashMask0 Register field at Byte Offset-10h                   |     |

|---------------------------------------------------------------------------------|-----|

| Table 6-17: Common Control Register field at Byte Offset-14h                    | 241 |

| Table 6-18: Primary Port Control structure fields at Byte Offset-XXh            | 241 |

| Table 6-19: IDM Entry                                                           |     |

| Table 6-20: SAMEntryAttr Register fields at Byte Offset-00h                     |     |

| Table 6-21: SAMEntryAddr0 Register field at Byte Offset-04h                     |     |

| Table 6-22: SAMEntryAddr1 Register field at Byte Offset-08h                     | 250 |

| Table 6-23: SAMHashMask0 Register field at Byte Offset-00h of the SAM Hash Mask | 250 |

| Table 6-24: SAMHashMask1 Register field at Byte Offset-04h of the SAM Hash Mask | 251 |

| Table 6-25: MemPoolEntryCapStat0 Register fields at Byte Offset-00h             |     |

| Table 6-26: MemPoolEntryCapStat1 Register fields at Byte Offset-04h             | 258 |

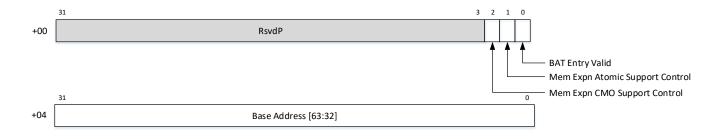

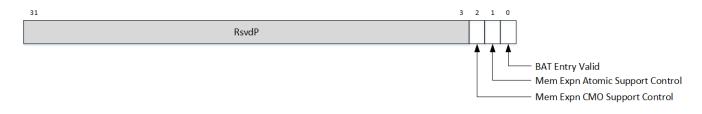

| Table 6-27: BATBaseAddrTypeEntryCntlO Register Fields at Byte Offset-00h        | 259 |

| Table 6-28: BATBaseAddrTypeEntryCntl1 Register fields at Byte Offset-04h        | 261 |

| Table 6-29: BATFixedOffsetTypeEntryCntl Register fields                         | 261 |

| Table 6-30: PortCapStat1 Register fields at Byte Offset-04h                     | 266 |

| Table 6-31: PortCapStat2 Register Fields at Byte Offset-08h                     | 270 |

| Table 6-32: CCIX Port Capabilities&Status Register Fields at Byte Offset-0Ch    | 271 |

| Table 6-33: PortCntl Register Fields at Byte Offset-04h                         | 273 |

| Table 6-34: PSAM Register Fields at Byte Offset-00h                             | 275 |

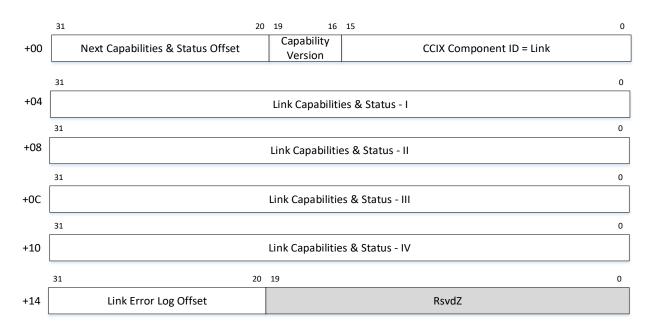

| Table 6-35: LinkCapStat Register Fields at Byte Offset-04h                      | 277 |

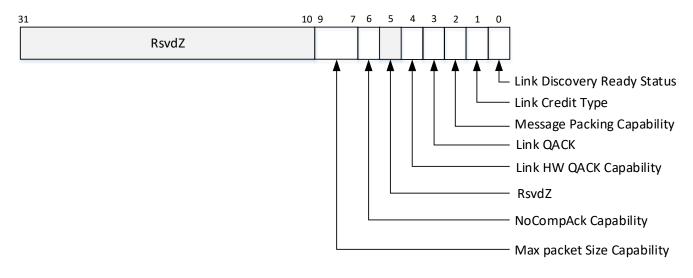

| Table 6-36: LinkSendCap Register Fields at Byte Offset-08h                      | 281 |

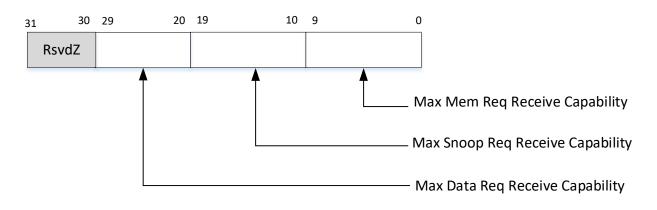

| Table 6-37: LinkRcvCap Register Fields at Byte Offset-0Ch                       | 282 |

| Table 6-38: LinkCreditMiscMsgCap Register Fields at Byte Offset-10h             | 284 |

| Table 6-39: LinkAttrCntl Entry Fields at Byte Offset-00h                        | 287 |

| Table 6-40: LinkMaxCreditCntl Entry Fields at Byte Offset-04h                   | 290 |

| Table 6-41: LinkMinCreditCntl Entry Fields at Byte Offset-08h                   | 292 |

| Table 6-42: LinkMiscCreditCntl Entry at Byte Offset-0Ch                         | 294 |

| Table 6-43: BCastFwdCntlVctr0 Register Fields                                   | 295 |

| Table 6-44: BCastFwdCntlVctr1 Register Fields                                   |     |

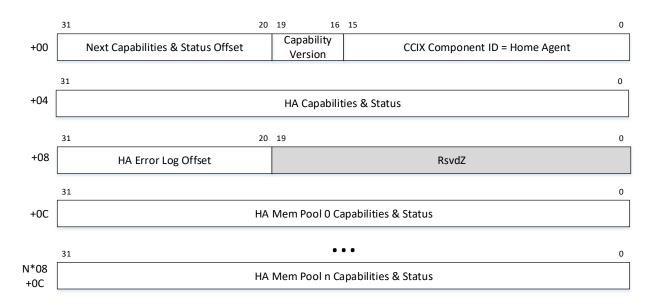

| Table 6-45: HACapStat Register Fields at Byte Offset-04h                        | 299 |

| Table 6-46: HACntl Register Fields at Byte Offset-04h                           | 306 |

| Table 6-47: HACntlPresentRAIDVctr0 Register Fields                              | 309 |

| Table 6-48: HACntlPresentRAIDVctr1 Register Fields                              | 310 |

| Table 6-49: HAIDTblEntry Register Fields                                        | 311 |

| Table 6-50: RACapStat Register Fields at Byte Offset-04h                        | 312 |

| Table 6-51: RACntl Register Fields at Byte Offset-04h                           | 316 |

| Table 6-52: SACapStat Register Fields at Byte Offset-04h                        | 320 |

| Table 6-53: SACntl Register Fields at Byte Offset-04h                           | 324 |

| Table 6-54: RARefIndexPtr Register fields                                       |     |

| Table 6-55: AFRefIndexPtr Register fields                                       | 326 |

| Table 6-56: AFtoRABindingCapPtr Register fields                                 | 327 |

| Table 6-57: RA Reference Index Entry Register Index fields                      |     |

| Table 6-58: AF Reference Index Entry Register fields                            |     |

| Table 6-59: AF to RA Binding Capability Entry Register fields                   | 331 |

| Table 6-60: AF to RA Binding Control Entry Register fields                      | 333 |

|                                                                                 |     |

### List of Tables

| Table 6-61: CCIXTransportCapabilities Register                                 | 336 |

|--------------------------------------------------------------------------------|-----|

| Table 6-62: ESMMandatoryDataRateCapability Register                            | 339 |

| Table 6-63: ESMOptionalDataRateCapability Register                             | 339 |

| Table 6-64: ESMStatus Register                                                 | 340 |

| Table 6-65: ESMControl Register                                                | 341 |

| Table 6-66: ESMLaneEqualizationControl Register Entry                          | 347 |

| Table 6-67: TransactionLayerCapabilities Register                              | 349 |

| Table 6-68: TransactionLayerControl Register                                   | 350 |

| Table 7-1: CCIX PER Message DW 1                                               | 368 |

| Table 7-2: CCIX PER Message DW 2                                               | 368 |

| Table 7-3: CCIX PER Log Header DW 0                                            | 375 |

| Table 7-4: CCIX PER Log Header DW 1                                            | 375 |

| Table 7-5: CCIX Error Severity Priorities (lowest to highest)                  | 376 |

| Table 7-6: CCIX PER Memory Error Type Structure                                | 377 |

| Table 7-7: CCIX PER Cache Error Type Structure                                 |     |

| Table 7-8: CCIX PER ATC Error Type Structure                                   |     |

| Table 7-9: CCIX PER Port Error Type Structure                                  |     |

| Table 7-10: CCIX Link Error Type Structure                                     |     |

| Table 7-11: CCIX PER Agent Internal Error Type Structure                       |     |

| Table 7-12: Vendor-Specific Log Info                                           |     |

| Table 7-13: Device Error Control & Status Register (DevErrCntlStat) Fields     |     |

| Table 7-14: Component Error Control & Status Register 0 (*ErrCntlStat0) Fields |     |

| Table 7-15: Component Error Control & Status Register 1 (*ErrCntlStat1) Fields | 394 |

| Table 8-1: Memory Attributes                                                   |     |

|                                                                                |     |

# **Chapter 1. Document Overview**

# **1.1 Specification Objective**

The current document provides all aspects of the specification that impact hardware design.

# **1.2 Terms and Acronyms**

- 5 The following is a list of terms and acronyms that are critical for broader understanding of the key aspects of the overall specification. The terms that are used within the context of the detailed specification of a chapter are not listed here and instead are listed within the chapter where they are used.

- 1 **Port** Port is associated with physical pins and has two sub-layers: a) CCIX<sup>®</sup> layer Port, referred to as CCIX Port and b) Transport layer Port, referred to as Transport Port.

- a. CCIX Port CCIX Port acts as an ingress and egress of the CCIX Protocol Layer messages from a given CCIX Device. Each CCIX Port must have an associated Transport Port as well.

- b. Transport Port A Transport Port is the Controller that acts as the gateway for ingress and egress of transport layer packets. Transport Port in this version of CCIX specification is based on PCI Express<sup>®</sup> (PCIe). Transport Port is referred to as PCIe Port for PCIe-based CCIX transport.

- 15 2 **CCIX Link** CCIX Link is a logical connection between a pair of CCIX ports. Each CCIX Link manages credits used for CCIX message communication.

- a. For each CCIX Link there may be one or more CCIX layer Credit Classes for CCIX layer message communication.

- 3 **PCIe Link** PCIe Link is a physical connection between the PCIe Ports. PCIe Link conforms to the Link definition in the PCIe specification.

- 4 **Transport Link** Transport Link is a generic term to refer to a physical link in the Transport Layer specification used to overlay the CCIX Protocol Layer.

- 5 **CCIX Components** CCIX Components are architected building blocks required to define the CCIX coherency protocol. The CCIX protocol defines the interaction between these building blocks to achieve data sharing while conforming to memory consistency requirements.

- 6 Acceleration Function Acceleration Function is an implementation specific source of a memory access request for coherency protocol that are represented by a CCIX Request Agent for communication by CCIX coherency layer.

- 7 **CCIX Device** A CCIX Device is a physical entity consisting of one or more CCIX Components that conform to the CCIX protocol. A CCIX Device must have at least one Port.

10

20

25

#### **Document Overview**

- 8 **CCIX Agent** Any CCIX protocol Component that can be a source or a target of a transaction is referred to as a CCIX agent. A CCIX Agent can be further classified as one of the following agent types:

- a. **Request Agent** A Request Agent (RA) is a CCIX Agent that is the source of read and write transactions. Each of the CCIX RAs may have one or more internal initiators, Acceleration Functions (AFs).

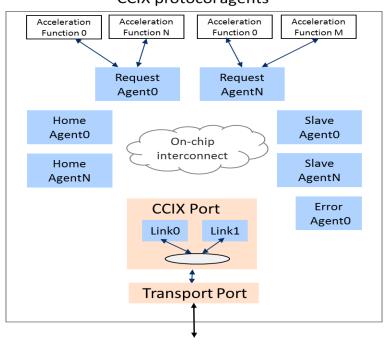

- b. Home Agent A Home Agent (HA) is a CCIX Agent that manages coherency and access to memory for a given address range. An HA manages coherency by sending snoop transactions to the required Request Agents when a cache state change is required for a cache line. Each CCIX Home Agent acts as a Point of Coherency (PoC) and Point of Serialization (PoS) for a given address.

- c. Slave Agent CCIX enables expanding system memory to include memory attached to an external CCIX Device. When the Home Agent resides on one chip and some or all of the physical memory associated with the Home Agent resides on a separate chip, the resulting new architectural component (the expansion memory) is referred to as Slave Agent (SA). A Slave Agent is never accessed directly by a Request Agent. A Request Agent always accesses a Home Agent, which in turn accesses the Slave Agent.

- d. **Error Agent** An Error Agent (EA) receives and processes protocol error messages. The protocol error messages are sent from CCIX components.

- 9 CCIX Functional Block CCIX Functional Blocks are building blocks that are needed to define functionality of CCIX Components; e.g., System Address Map (SAM).

- 10 **CCIX switch** CCIX switch is a CCIX Device consisting of two or more CCIX Ports capable of CCIX Port to Port forwarding. A CCIX switch may be embedded in a CCIX Device with Agents, or it may be a CCIX Device which has no CCIX Agents.

- 11 Packet Packet is the unit of transfer that is routed independently.

- 12 **SAM** System Address Map.

- 13 **G-SAM** Global System Address Map. This is the global view of the System Address Map of memory accessed by all Home and Slave Agents.

- 14 G-RSAM Global Request Agent System Address Map. This is the global view of the System Address Map of memory accessed by all Request Agents.

- 15 **G-HSAM** Global Home Agent System Address Map. This is the global view of the System Address Map of memory accessed by all Home Agents.

- 16 RSAM Request Agent's view of SAM for a given CCIX Device.

- 17 **HSAM** Home Agent's view of SAM for a given CCIX Device for the Requests to Slave Agents issued by HA.

- 18 PSAM SAM associated with a Port for outbound requests to allow mapping of an address range to a carrier CCIX Link for this request.

- 19 **PHY** Physical Layer of the interface.

- 20 **EDR** Extended Data Rate. The data rates for the PHY that are in addition to the standard PHY speeds defined by the *PCI Express Base Specification* (see <u>Reference Documents</u>).

15

20

35

10

- 21 **ESM** Extended Speed Mode ESM is a mechanism to allow PCIe Link speed transitions between the standard PCIe speeds and EDR speeds.

- 22 **DW** Double Word CCIX defines Double Word as a 4B-aligned 4B data element.

- 23 **DWord** DWord is another representation of DW with identical meaning.

- 5 24 **Snoop Hazard** A condition when a Snoop Request and a copyback request traveling in opposite directions are to the same cache line and have the same Target Agent and Source Agent respectively.

- 25 Switches CCIX topology supports multiple versions of a switch, these being:

- a. Transport Switch PCIe switch, where messages are sent between endpoints using the PCIe-compatible packet format.

- Protocol Aware Switch (or CCIX Switch) A switch that can use the optimized CCIX packet format and is aware of the routing of agents; capable of merging of snoop responses for snoop broadcast messages; detecting Snoop Hazards, and managing the coherence conflict.

- 26 **Message Type** CCIX uses six Message Types, these being Memory Request, Snoop Request, Misc (credited), Memory response, Snoop response, Misc (Uncredited).

- a. Memory Request, Snoop Request, and Misc (credited) are Credited message types.

- b. Memory Response, Snoop Response, and Misc (uncredited) message types require NO credits to be sent.

- 27 **CCIX Consortium Identifier (CCID)** The 16-bit common identifier in CCIX DVSEC structures and CCIX PCIe Compatible Header Protocol Messages.

- 28 **CCIX Consortium Unique Value (CCUV)** The hardware default 16-bit value in CCIX DVSEC structures and CCIX PCIe Compatible Header Protocol Messages. CCUV is also the CCID if the CCID has not been reprogrammed with a new 16-bit value. CCUV is obtained from the CCIX Consortium.

10

## **1.3 Reference Documents**

PCI SIG documents, available at <a href="https://pcisig.com/specifications">https://pcisig.com/specifications</a>:

- <sup>1</sup>PCI Express Base Specification, Revision 4.0, Version 1.0

- PCI Express Card Electromechanical Specification, Revision 4.0

- PCI Local Bus Specification, Revision 3.0

- PCI-X Addendum to the PCI Local Bus Specification, Revision 2.0

- PCI Hot-Plug Specification, Revision 1.1

- PCI Standard Hot-Plug Controller and Subsystem Specification, Revision 1.0

- PCI-to-PCI Bridge Architecture Specification, Revision 1.2

- PCI Bus Power Management Interface Specification, Revision 1.2

- PCI Firmware Specification, Revision 3.0

- Address Translation Services, Revision 1.1

- PCI Express Base Specification, Revision 1.0a, PCI-SIG

OIF Common Electrical I/O (CEI) Electrical and Jitter Interoperability Agreement for 25+ GT/s I/O, IA # OIF-CEI-

15

10

5

5 **03.1, February 18, 2014**

Unified Extensible Firmware Interface (UEFI) Specification, Version 2.7

<sup>&</sup>lt;sup>1</sup> All references to the *PCI Express Base Specification* in this document are to the PCI Express Base Specification, Revision 4.0, Version 1.0, unless indicated otherwise.

# **Chapter 2. CCIX Overview**

# **2.1 Introduction**

The Cache Coherent Interconnect for Accelerators (CCIX<sup>®</sup>) enables a new model of data sharing between a server host, accelerators and external interface attached memory. CCIX extends the existing data sharing paradigm for processor-to-processor and processor-to-memory interactions, to include data sharing between processor-to-accelerator, and accelerator-to-accelerator. Additonally, data sharing between processors and accelerators is expanded to include data in memory attached to PCI Express<sup>®</sup> (PCIe) devices. Thus, CCIX enables data to be shared freely between process threads on Host processor cores and Acceleration Functions (AFs), without software intervention (OS or driver) to manage the data movement between host and accelerators, similar to how data is shared between process threads executing on processor cores.

In addition, CCIX enables expansion of system memory to include peripheral attached memory. Memory attached to different devices, besides the default of being managed by a driver, can be optionally seen as an OS managed pool of memory with non-uniform latencies, as is the case for existing Non-Uniform Memory Access (NUMA) architectures.

15 CCIX allows all data structures to be referenced by a common set of Virtual Addresses (VA) between all processing entities (hosts, accelerators and IO devices - accelerators and IO device are here on referred to as accelerators). In order to achieve these capabilities, CCIX expands the Shared Virtual Memory (SVM) model to include the following key attributes:

#### **1 Expanded System Memory:**

CCIX allows expanding the System Memory domain beyond host attached memory. The host memory manager can optionally allocate and manage peripheral attached memory in the same manner that host memory is allocated and managed, as part of system memory.

Thus, with CCIX Memory Expansion, a host can expand its memory capacity and/or support new memory technologies beyond that available with the host's native memory capabilities. Note that the host's view of peripheral attached memory is consistent with the existing view of memory in a multi-node host system, the Non-Uniform Memory Access (NUMA) memory model.

#### 2 Software transparent data movement based on a processor's or accelerator's application access patterns:

CCIX enables hardware coherent caches in accelerators, and maintains a consistent view of shared data for both processor and accelerator accesses without explicit intervention from software.

In a CCIX system, caching allows implicit movement of shared data for further re-use or modification, based on the processor's or accelerator's access patterns, without the overhead of software migrating or maintaining multiple or modified copies between them.

There are use cases, for example the GPU-based co-processing model for numerical analysis, where OS (memory management) assisted implicit data movement is a suitable paradigm, and solutions do exist for

25

20

5

these use-cases. Due to the software overhead involved, OS assisted data movement is typically only done for bulk data at a coarse-grained level. However, there are fine-grained data sharing use cases for example, the offloading of large graph transversal, that benefit from hardware managed cache coherency provided by CCIX. Thus, CCIX has an inherent ability to support both coarse-grained and fine-grained data sharing use cases.

3 Application-managed movement of data from host to accelerator attached memory:

CCIX enables applications to orchestrate data movement from one memory node to another without requiring any OS assistance, and while still preserving the SVM data sharing model. This allows a producer of data to place that data next to the computational entity (processor or an Acceleration Function) that is the consumer of the data. The optimal memory location for placement of the data can be determined from CCIX provided proximity information of memory to the computational entity.

The combined capabilities form the basis of a new model of seamless data sharing and data movement between host memory and processors, and peripheral attached memory and accelerators. Data either naturally migrates to the optimal location based on an application's access patterns on the CCIX cache coherent network, or the application itself can orchestrate data movement between accelerator-attached and host-attached memory, all without requiring either OS or driver support.

# **2.2 Topologies**

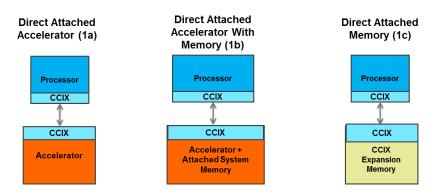

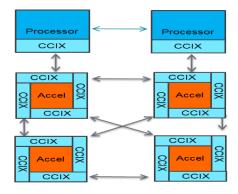

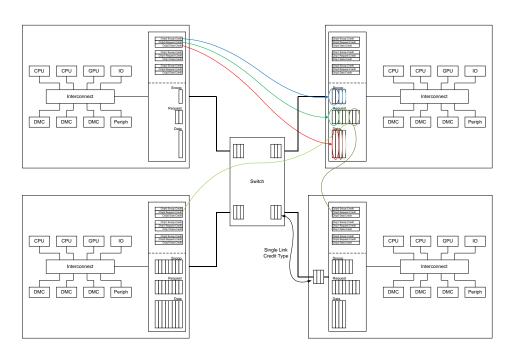

The CCIX standard enables multiple platform topologies for connecting hosts to I/O devices, starting with support for tree-topologies that are common to the PCI Express<sup>®</sup> (PCIe) interconnect. CCIX also supports mesh, ring and other flexible topologies that are overlaid over the PCIe transport or, in the future, additional transports. The figures illustrate a few of the direct-attached topologies and illustrate a few of the mesh topologies that can be enabled by CCIX. For illustrations in Figure 2-1 and Figure 2-2 with a CCIX-linked host, the host has a computational entity (Processor or an Acceleration Function) as well as host attached memory.

Figure 2-1: Example CCIX Direct-Attached topologies

5

10

15

#### **CCIX Overview**

Figure 2-2: Example CCIX Fully Connected topologies

- Figure 2-1 (1a): Illustrates a platform with a CCIX-linked host direct-attached to a peripheral with a CCIX accelerator. This platform enables application acceleration with data sharing between the accelerator and processors, with the data residing only in host attached memory.

- Figure 2-1 (1b): Illustrates a platform with a CCIX-linked host direct-attached to a peripheral that has a CCIX accelerator as well as peripheral memory on the same device that can be host-mapped as part of system memory. This platform extends the application acceleration capabilities of platform 1a to enable sharing between the accelerator and processors such that the data can reside not only in host attached memory but also reside in locally attached accelerator memory as part of expanded system memory.

- Figure 2-1 (1c): Illustrates a platform with a CCIX-linked host direct-attached to a peripheral that has memory that can be made part of the host system map. On this platform, the host has expanded memory capabilities. The expanded memory capability may offer either expansion of memory capacity and/or allow integration of new memory technology beyond that of the host's native capabilities.

- Figure 2-2: Illustrates a platform with the CCIX-linked host and CCIX accelerators, all nodes in a CCIX mesh topology. With CCIX links between the accelerators as well as between the accelerators and the host, fine-grained data sharing can occur across multiple accelerators and processors. In addition, system memory may be expanded to include accelerator attached memory when present, such that the shared-data can reside in either host-attached memory or accelerator-attached memory, for optimized data movement.

# **2.3 CCIX Architecture Model**

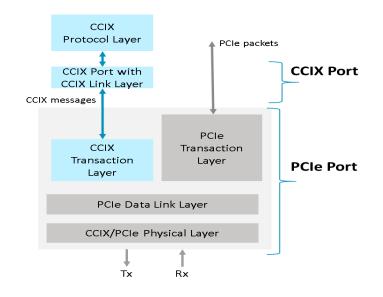

CCIX specifies a cache coherent interconnect that is overlaid on a PCIe transport. The overlay nature of the coherency interconnect makes it possible for CCIX coherency interconnect traffic to be carried over transports other than PCIe in the future. For the case of CCIX over a PCIe transport, CCIX also enhances PCIe to allow the carrying of coherency traffic in a manner that minimizes the impact to latency due to the PCIe transaction layer. In order to achieve the lower latency for CCIX communication, CCIX creates a light weight transaction layer that can independently co-exist alongside the standard PCIe transaction layer. Additionally, a CCIX link layer (that is overlaid on a physical transport like PCIe) ensures the availability of sufficient transaction channels necessary for deadlock free communication of CCIX protocol messages.

10

15

20

25

#### **CCIX Overview**

#### **Hardware Specification**

CCIX's PCIe-based Transport layer utilizes the common data link and Physical (PHY) layers to carry PCIe and CCIX transactions. For the PHY layer, the CCIX standard supports all standard data rates in the *PCI Express Base Specification*, and additionally defines two new data transfer rates - 20GT/s and 25GT/s.

The CCIX model of overlaying the CCIX coherency interconnect over PCIe transport, and the associated enhancements to the PCIe Transport are shown in Figure 2-3.

#### Figure 2-3: CCIX and associated PCIe layers

Chapter 4 provides the CCIX Transaction Layer specification.

The sections below define the key components and features of the CCIX architecture.

# **2.3.1 Components of the CCIX Architecture**

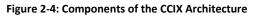

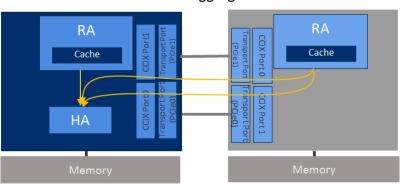

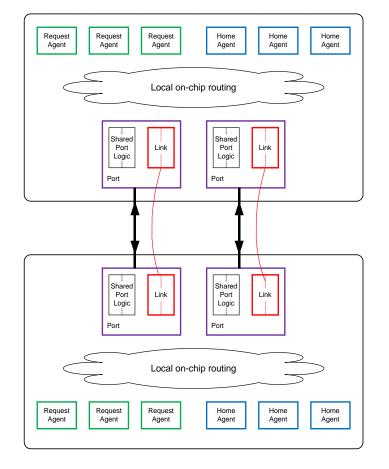

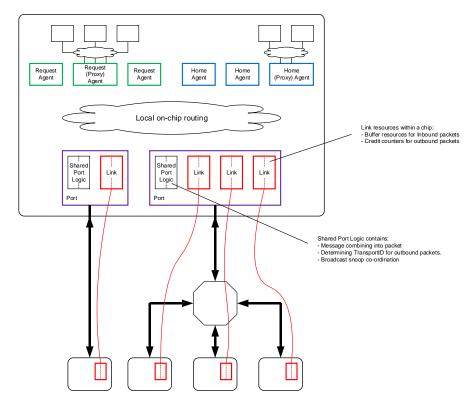

CCIX defines the memory access protocol in terms of CCIX Components. Each CCIX device contains a selection of CCIX Agents, and communication Ports and associated Links with associated resources, as illustrated in Figure 2-4. An Agent can either be a Request Agent, a Home Agent, a Slave Agent, or an Error Agent. An Agent is identified within the protocol using an Agent ID value. A brief description of each agent type is given below:

- Request Agent A Request Agent (RA) performs read and write transactions to addresses within the system. An RA can choose to cache the memory locations accessed. Each of the CCIX RAs may have one or more internal initiators, referred to as Acceleration Functions (AFs).

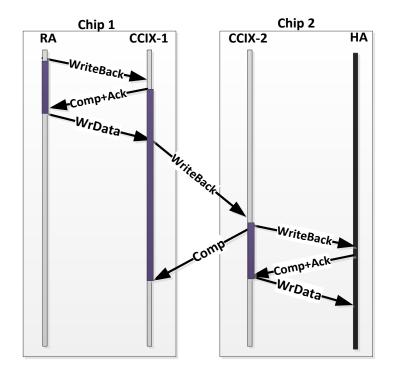

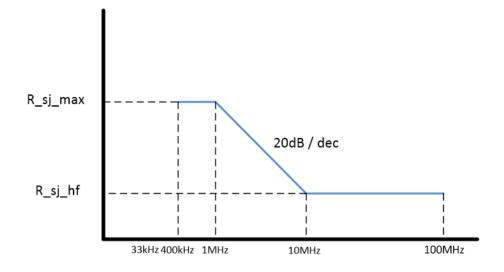

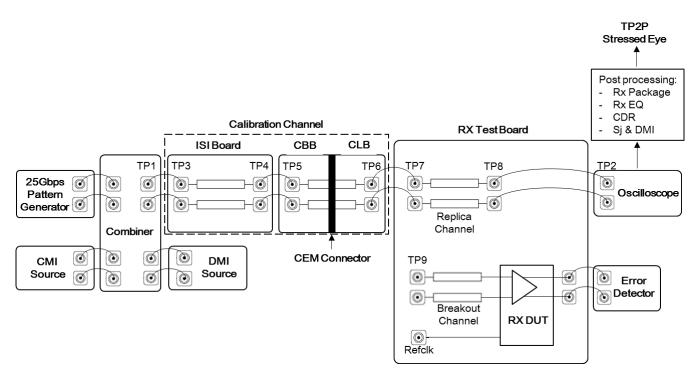

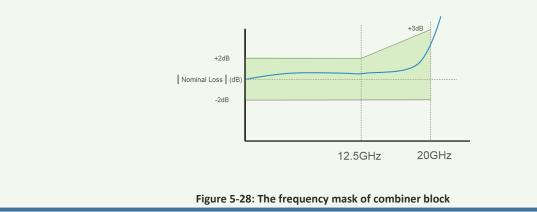

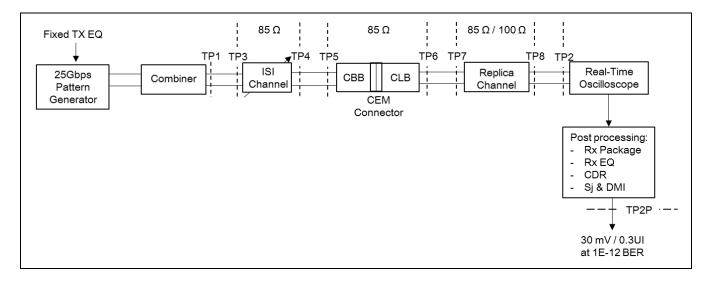

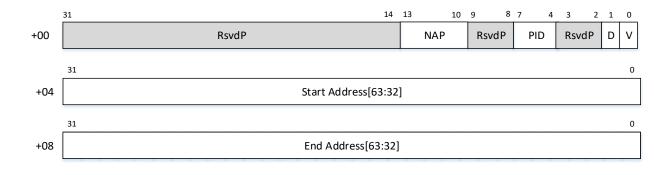

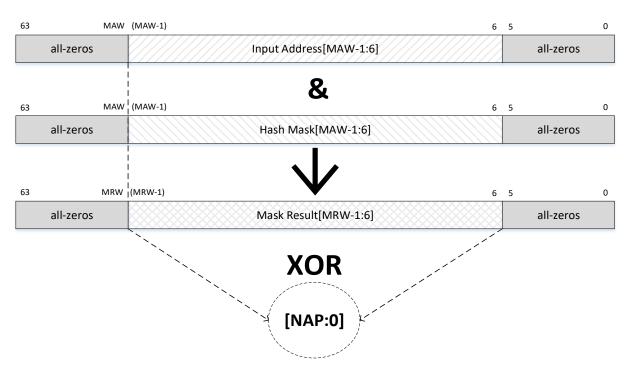

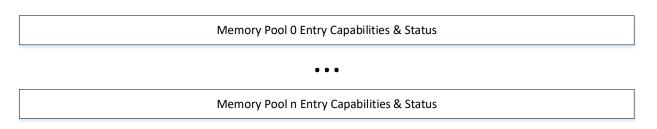

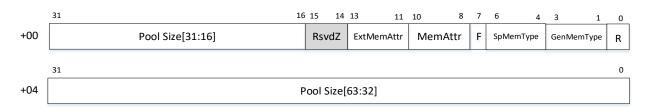

- Home Agent A Home Agent (HA) is responsible for managing coherency and access to memory for a pre-determined address range. It manages coherency by sending snoop transactions to the required Request Agents when a cache state change is required for a cache line. Each CCIX Home Agent acts as a Point of Coherency (PoC) and Point of Serialization (PoS) for a given address.