October 2019

EVALUAT

Errata for the Compute Express Link Specification Rev 1.1

The copyright in this Specification is owned by CXL as a Contractual SIG. Use of this Specification and any related intellectual property (collectively, the "Specification"), is governed by the terms of the Promoter, Contributor or Adopter Agreement (collectively, "Agreement") as available by request from admin@computeexpresslink.org. This specification may only be used by (a) a party to the Agreement, and in compliance with its terms, or (b) non-parties to the Agreement who have accepted an approved disclaimer of liability and acknowledgement of IP protections.

Any use or implementation of this specification is expressly subject to the terms and conditions described in the CXL Promoter, Contributor, and/or Adopter Agreement, as appropriate for your status. The implementation or use of industry specifications made available by any other standards body, such as PCIe, if referenced in a CXL Final Specification (as such term is defined in those agreements) is not governed by CXL policies and procedures, and may be subject to patent, copyright, and other intellectual property right protection (collectively "IPR"). Licensing of such IPR in a referenced industry specification shall be governed by the policies and procedures of the organization promulgating such industry specification.

This document is provided 'as is' with no warranties, express or implied, including any warranty of merchantability, fitness for a particular purpose, noninfringement of any third-party intellectual property rights, or any warranty otherwise arising out of any proposal, specification or sample. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

CXL is a trademark of the CXL Contractual SIG

All other product names are trademarks, registered trademarks, or servicemarks of their respective

©2019 CXL

## Contents

| E1  | CXL.AL and Flex Bus.AL Typo5                                  |

|-----|---------------------------------------------------------------|

| E2  | Control SKP Ordered Set Frequency5                            |

| E3  | CXL Downstream Port Supported PCIe Capabilities5              |

| E4  | CXL Upstream Port Supported PCIe Capabilities6                |

| E5  | CXL Power Management Messages7                                |

| E6  | CXL Configuration Space Registers                             |

| E7  | CXLCM Flit Packing Rules9                                     |

| E8  | CXLCM Slot Format Diagram Updates9                            |

| E9  | CLFlush Definition and Clarification for Biasing15            |

| E10 | Buried Cache State Rules and Multiple Access Over CXL.cache16 |

| E11 | ARB/MUX Virtual LSM Resolution Table Clarifications           |

| E12 | Text Updates in CXLCM Link Layer Chapter19                    |

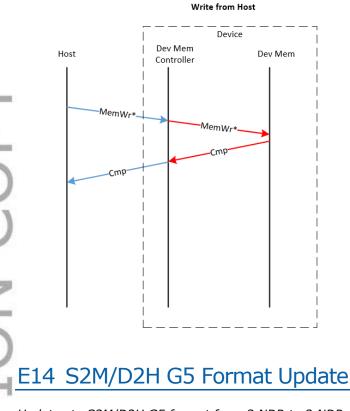

| E13 | Fixed Typos in Figure depicting Write from Host19             |

| E14 | S2M/D2H G5 Format Update20                                    |

| E15 | PM timeout value                                              |

| E16 | Figure 65 Title                                               |

## **Revision History**

| Revision | Description                   | Date         |

|----------|-------------------------------|--------------|

| 1.0      | First Release: Errata E1-E16. | October 2019 |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

|          |                               |              |

# E1 CXL.AL and Flex Bus.AL Typo

*In general, Flex Bus.AL should be substituted with Flex Bus.CXL throughout the specification document. Additionally, in section 11.4, make the following changes:*

#### **11.4 CXL Viral Handling**

• •

When a CXL.AL device goes into Viral, the upstream CXL.io shall perform the following:

- Master Abort Upstream Requests

- Completer Abort Upstream Completions

- Signal Failed Response for Downstream Completions

# E2 Control SKP Ordered Set Frequency

In section 6.7.1, make the following changes:

#### 6.7.1 Control SKP Ordered Frequency and L1/Recovery Entry

In Flex Bus.CXL mode, if sync header bypass is enabled, the following rules apply:

• After the SDS, the physical layer must schedule a control SKP Ordered Set or SKP Ordered Set after every 340 data blocks, unless it is exiting the data stream. Note: The control SKP OSs are alternated with regular SKP OSs <u>at 16 GT/s or higher speeds</u>; <u>at 8 GT/s</u>, <u>only SKP OSs are scheduled</u>.

# CXL Downstream Port Supported PCIe Capabilities

In section 7.2.1.1, Table 60, make the following changes:

Table 60. CXL Downstream Port Supported PCIe Capabilities and Extended Capabilities

| Supported PCIe Capabilities<br>and Extended Capabilities | Exceptions <sup>1</sup>                                                                                                                    | Notes                                            |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| PCI Express Capability                                   | Slot Capabilities, Slot Control, Slot<br>Status, Slot Capabilites 2, Slot<br>Control 2, and Slot Status 2<br>registers are not applicable. | None                                             |

| PCI Power Management Capability                          | None                                                                                                                                       | None                                             |

| MSI Capability                                           | None                                                                                                                                       | None                                             |

| Advanced Error Reporting<br>Extended Capability          | None                                                                                                                                       | Required for CXL despite being optional for PCIe |

| ACS Extended Capability                                  | None                                                                                                                                       | None                                             |

| Multicast Extended Capability                            | None                                                                                                                                       | None                                             |

| Downstream Port Containment<br>Extended Capability        | None | None                                                                             |  |  |  |  |

|-----------------------------------------------------------|------|----------------------------------------------------------------------------------|--|--|--|--|

| Designated Vendor-Specific<br>Extended Capability (DVSEC) | None | Please refer to section Figure<br>7.2.1.3 for Flex Bus Port DVSEC<br>definition. |  |  |  |  |

| Secondary PCI Express<br>Extended Capability              | None | None                                                                             |  |  |  |  |

| <u>Data Link Feature Extended</u><br><u>Capability</u>    | None | None                                                                             |  |  |  |  |

| Physical Layer 16.0 GT/s<br>Extended Capability           | None | None                                                                             |  |  |  |  |

| Physical Layer 32.0 GT/s<br>Extended Capability           | None | None                                                                             |  |  |  |  |

| Lane Margining at the Receiver<br>Extended Capability     | None | None                                                                             |  |  |  |  |

| Alternate Protocol Extended<br>Capability                 | None | None                                                                             |  |  |  |  |

# **CXL Upstream Port Supported PCIe Capabilities**

In section 7.2.1.2, Table 61, make the following changes:

| Support PCIe Capabilties and                    | Exceptions <sup>1</sup> | Notes                                             |

|-------------------------------------------------|-------------------------|---------------------------------------------------|

| Extended Capabilties                            |                         |                                                   |

| PCI Express Capability                          | None                    | N/A <u>None</u>                                   |

| Advanced Error Reporting<br>Extended Capability | None                    | Required for CXL despite being optional for PCIe. |

| Multicast Extended Capability                   | None                    | N/A                                               |

| Virtual Channel Extended<br>Capability          | None                    | VC0 and VC1                                       |

| Designated Vendor-Specific<br>Extended Capability (DVSEC) | None | Please refer to section Figure<br>7.2.1.3 for Flex Bus Port DVSEC<br>definition. |

|-----------------------------------------------------------|------|----------------------------------------------------------------------------------|

| Secondary PCI Express Extended<br>Capability              | None | None                                                                             |

| <u>Data Link Feature Extended</u><br><u>Capability</u>    | None | <u>None</u>                                                                      |

| Physical Layer 16.0 GT/s Extended<br>Capability           | None | None                                                                             |

| Physical Layer 32.0 GT/s Extended<br>Capability           | None | <u>None</u>                                                                      |

| Lane Margining at the Receiver<br>Extended Capability     | None | None                                                                             |

| <u>Alternate Protocol Extended</u><br><u>Capability</u>   | None | <u>None</u>                                                                      |

# E5 CXL Power Management Messages

In section 3.1.2, Table 3, make the following changes:

| Field         | Description                                                                                                                                                                                                                                                                                                                                                      | Notes                                                                                                                                                                                                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Payload[95:0] | <pre> AGENT_INFO: If Param.Index == 0, 7:0 - REVISION_ID CAPABILITY VECTOR 0 - Always set to indicate support for CXL 1.1 PM messages 7:1 - Reserved 15:8 - PrepType 0x00 =&gt; General Prep All others reserved 0x01 =&gt; Early Prep; 0x02 =&gt; Reset Entry Start (first checkpoint for CXL device blocks during a Reset event/power state transition);</pre> | CXL Agent must<br>treat the<br>TARGET_AGENT_ID<br>field as Reserved<br>when returning<br>credits to Host.<br>Only Index 0 is<br>defined for<br>AGENT_INFO, all<br>other Index values<br>are reserved. |

0x03 => Link Turnoff (typically the last checkpoint during a Reset event/power state transition);

17:16 - Reserved Phase

0x00 => Phase 0

0x01 => Phase 1

0x02 => Phase 2

0x03 => Phase 3

All others reserved

PMREQ:

31:0 - PCIe LTR format

All others reserved

# E6 CXL Configuration Space Registers

In chapter 7, Table 57, make the following changes:

| Attribute | Description                                                             |

|-----------|-------------------------------------------------------------------------|

| RO        | Read Only                                                               |

| RO-V      | Read-Only-Variant                                                       |

| RW        | Read-Write                                                              |

| RWS       | Read-Write-Sticky                                                       |

| RWO       | Read-Write-Onee-To Lock<br>Field becomes RO after<br>writing one to it. |

| RWL       | Read-Write-Lockable                                                     |

| RW1CS     | Read-Write-One-To-Clear-<br>Sticky                                      |

EVALUATI

СОРУ

In section 7.1.1.3, make the following changes:

|   | Bit  | Attributes     | Description                                                                                                                                                           |

|---|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 13:0 | N/A            | Reserved (RSVD).                                                                                                                                                      |

|   | 14   | RW <u>1C</u> S | Viral_Status: When set, indicates that the CXL device has entered Viral self-<br>isolation mode. See Section 11.4, "CXL Viral Handling" on page 198 for more details. |

| ) |      |                | Note: Viral condition is cleared by warm reset or cold reset, but Viral Status bit survives warm reset.                                                               |

|   | 15   | N/A            | Reserved (RSVD).                                                                                                                                                      |

## E7 CXLCM Flit Packing Rules

In Section 4.2.5, add following Flit Packing Rules that clarify Bit Ordering requirements.

#### 4.2.5 Flit Packing Rules

- For a given slot, lower bit positions are defined as bit positions that appear starting from lower order Byte #. That is, bits are ordered starting from (Byte# 0, Bit# 0) through (Byte #15, Bit# 7).

- For multi-bit message fields like Address[MSB:LSB], lesser significant bits will appear in lower order bit positions.

- Message ordering within a flit is based on flit bit numbering, i.e. the earliest messages are placed at the lowest flit bit positions and progressively later messages are placed at progressively higher bit positions. Examples: An M2S Req 0 packed in Slot 0 precedes an M2S Req 1 packed in Slot 1. Similarly, a Snoop packed in Slot 1 follows a GO packed in Slot 0, and this ordering must be maintained. Finally, for Header Slot Format H1, an H2D Response packed starting from Byte# 7 precedes an H2D Response packed starting from Byte# 11.

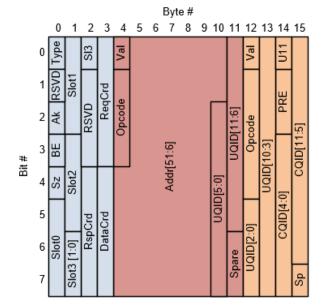

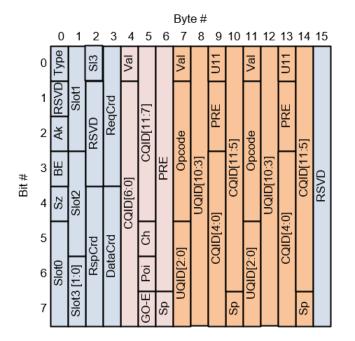

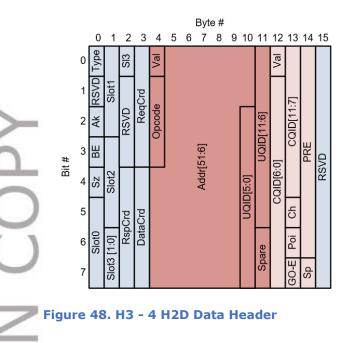

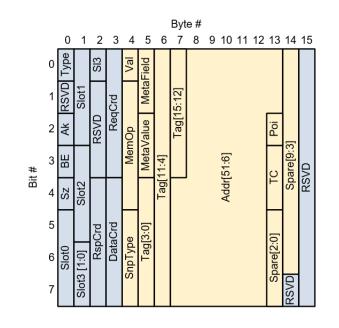

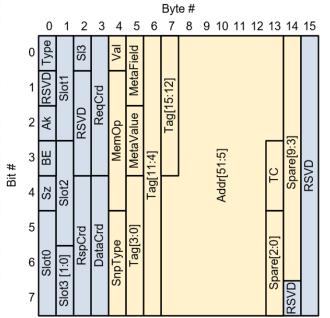

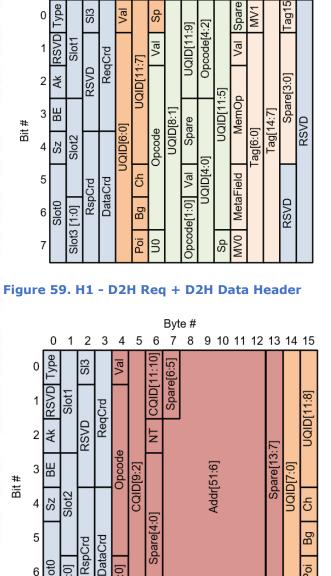

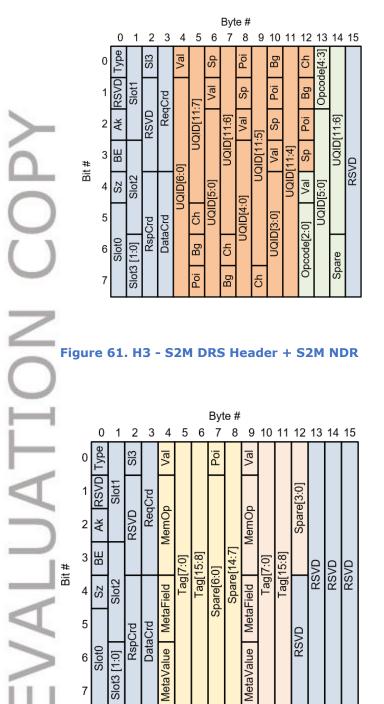

# 3 CXLCM Slot Format Diagram Updates

In Section 4.2.3, following diagrams for Header Slot Formats need to be updated to show Slot 3 bit encodings in correct bit positions. Also fixed Figure 50, which showed Addr[51:6] in CXL1.1, but should have show Addr[51:5] to match address bits required for M2S Req.

#### 4.2.3.2 H2D and M2S Formats

. . .

#### Figure 45. H0 - H2D Req + H2D Resp

#### Figure 46. H1 - H2D Data Header + H2D Resp + H2D Resp

#### Figure 47. H2 - H2D Req + H2D Data Header

|   |   |       |             |        |         |            |            |     | Byt       | te #       |     |           |            |     |           |            |     |  |

|---|---|-------|-------------|--------|---------|------------|------------|-----|-----------|------------|-----|-----------|------------|-----|-----------|------------|-----|--|

|   |   | 0     | 1           | 2      | 3       | 4          | 5          | 6   | 7         | 8          | 9   | 10        | 11         | 12  | 13        | 14         | 15  |  |

|   | 0 | Type  |             | SI3    |         | Val        |            |     | Val       |            |     | Val       |            |     | Val       |            |     |  |

|   | 1 | RSVD  | Slot1       |        | Crd     |            | 7]         |     |           | 7]         |     |           | 7]         |     |           | 7]         |     |  |

|   | 2 | Ak    |             | RSVD   | ReqCrd  |            | CQID[11:7] |     |           | CQID[11:7] |     |           | calb[11:7] |     |           | CQID[11:7] |     |  |

| - | 3 | BE    |             |        |         | <u>[</u> [ | ö          | PRE | 5         | ö          | PRE | 5         | ö          | PRE | 5         | S          | PRE |  |

| j | 4 | Sz    | Slot2       |        |         | CQID[6:0]  |            |     | CQID[6:0] |            |     | CQID[6:0] |            |     | CQID[6:0] |            |     |  |

|   | 5 |       |             | Crd    | aCrd    | Ö          | Ch         |     | 0         | Ch         |     | 0         | Ch         |     | 0         | Ch         |     |  |

|   | 6 | Slot0 | Slot3 [1:0] | RspCrd | DataCrd |            | Poi        |     |           | Poi        |     |           | Poi        |     |           | Poi        |     |  |

|   | 7 |       | Slot3       |        |         |            | GO-E       | Sp  |           | G0-E       | Sp  |           | GO-E       | Sp  |           | GO-E       | Sp  |  |

EVALUATIO

October 2019

#### Figure 49. H4 - M2S RwD Header

#### Figure 50. H5 - M2S Req

#### 4.2.3.3 D2H and S2M Formats

B

0 1 2

0

SI3

Figure 58. H0 - D2H Data Header + 2 D2H Resp + S2M NDR

3 4 5 6 7 8 9 10 11 12 13 14 15

Byte #

S

TION COF EVALUA

Slot0

6

7

[ [ 0

Slot3

0

CQIDI

Poi

Sp

Val

#### Figure 60. H2 - 4 D2H Data Header + D2H Resp

#### Figure 61. H3 - S2M DRS Header + S2M NDR

|       |   |       |             |        |         |           |          |           | Byt        | e #         |           |          |           |            |      |      |      |  |

|-------|---|-------|-------------|--------|---------|-----------|----------|-----------|------------|-------------|-----------|----------|-----------|------------|------|------|------|--|

|       |   | 0     | 1           | 2      | 3       | 4         | 5        | 6         | 7          | 8           | 9         | 10       | 11        | 12         | 13   | 14   | 15   |  |

|       | 0 | Type  |             | SI3    |         | Val       |          |           | Poi        |             | Val       |          |           |            |      |      |      |  |

|       | 1 | RSVD  | Slot1       | 0      | ReqCrd  | þ         |          |           |            |             | d         |          |           | Spare[3:0] |      |      |      |  |

|       | 2 | Ak    |             | RSVD   | Re      | MemOp     |          |           |            |             | MemOp     |          |           | Spar       |      |      |      |  |

| Bit # | 3 | BE    |             |        |         |           | Tag[7:0] | Tag[15:8] | [0         | Spare[14:7] |           | Tag[7:0] | Tag[15:8] |            | ΛD   | RSVD | ΛD   |  |

| Bi    | 4 | Sz    | Slot2       |        |         | Field     | Tag      | Tag[      | Spare[6:0] | Spare       | Field     | Tag      | Tag[      |            | RSVD | RS   | RSVD |  |

|       | 5 |       |             | Crd    | Crd     | MetaField |          |           | S          |             | MetaField |          |           | ΛD         |      |      |      |  |

|       | 6 | Slot0 | Slot3 [1:0] | RspCrd | DataCrd | MetaValue |          |           |            |             | MetaValue |          |           | RSVD       |      |      |      |  |

|       | 7 |       | Slot3       |        |         | Meta/     |          |           |            |             | Meta      |          |           |            |      |      |      |  |

#### Figure 62. H4 - 2 S2M NDR

|   |        |        | 0     | 1           | 2      | 3       | 4         | 5        | 6         | Byt<br>7   | e #<br>8        | 9         | 10               | 11   | 12   | 13    | 14        | 15   |       |  |  |  |  |  |

|---|--------|--------|-------|-------------|--------|---------|-----------|----------|-----------|------------|-----------------|-----------|------------------|------|------|-------|-----------|------|-------|--|--|--|--|--|

|   |        | 0      | Type  |             | SI3    |         | Val       |          |           |            | Field           |           |                  |      |      |       |           |      |       |  |  |  |  |  |

|   |        | 1 RSVD | RSVD  |             |        | Crd     |           |          |           | Spare[3:0] | MetaField       | ag[15:12] |                  |      |      |       |           |      |       |  |  |  |  |  |

|   |        | 2      | Ak    |             |        |         |           |          |           |            | RSVD            | ReqCrd    | MemOp            |      |      | Spare | MetaValue |      | Tag[1 |  |  |  |  |  |

|   | Bit #  | 3      | BE    |             |        |         |           | Tag[7:0] | Tag[15:8] |            | Meta            | Tag[1     |                  | RSVD | RSVD | RSVD  | RSVD      | RSVD |       |  |  |  |  |  |

|   | Bit    | 4      | Sz    |             |        |         | MetaField |          |           | Val        |                 |           | Spare[3:0]<br>RS | RS   |      |       |           |      |       |  |  |  |  |  |

| ) |        | 5      |       |             | RspCrd | DataCrd | Meta      |          |           |            | nOp<br>Tag[3:0] |           |                  |      |      |       |           |      |       |  |  |  |  |  |

| ) | 6<br>7 | 6      | Slot0 | Slot3 [1:0] | Rs     | Dat     | MetaValue |          |           | MemOp      | Tag             |           | Spar             |      |      |       |           |      |       |  |  |  |  |  |

|   |        | 7      |       | Slot        |        |         | Meta      |          |           |            |                 |           |                  |      |      |       |           |      |       |  |  |  |  |  |

| $\geq$         | Bit # | 1<br>2<br>3           | BE AK RSVD         | Slot1       | RSVD     | ReqCrd  | MemOp               | Tag[7:0]  | Tag[15:8] | Spare[3:0] | MetaValue Meta | Tag[11:4]    | Tag[15:12]    | RSVD | RSVD | RSVD     | RSVD          | RSVD    |         |

|----------------|-------|-----------------------|--------------------|-------------|----------|---------|---------------------|-----------|-----------|------------|----------------|--------------|---------------|------|------|----------|---------------|---------|---------|

|                | Bi    | 4                     | Sz                 | Slot2       |          |         | Field               | Tag       | Tag       | Val        |                | Tag          |               | RS   | RS   | RS       | RS            | RS      |         |

| $\bigcirc$     |       | 5                     |                    |             | RspCrd   | DataCrd | MetaField           |           |           | 0          | Tag[3:0]       |              | Spare[3:0]    |      |      |          |               |         |         |

| ()             |       | 6                     | Slot0              | Slot3 [1:0] | Rsp      | Data    | MetaValue           |           |           | MemOp      | Tag            |              | Spar          |      |      |          |               |         |         |

| $\cup$         |       | 7                     |                    | Slot3       |          |         | Meta                |           |           | 2          |                |              |               |      |      |          |               |         |         |

| 0              | Figu  | ire                   | e 6                | 3.          | HS       | 5 -     | 2                   | <b>52</b> | Μ         | DF         | S              |              |               |      |      |          |               |         |         |

| H              |       |                       | 0                  | 1           | 2        | 3       | 4                   | 5         | 6         |            | yte<br>7       | #<br>8       | 9 <i>^</i>    | 10   | 11   | 12       | 13            | 14      | 15      |

| F              |       | 0                     |                    | 1           | 2<br>SI3 | 3       | A la                | 5         | 6         |            | 7              | 8            | ۲al<br>ر      | 10   | 11   | 12<br>IO | 13            | 14      | 15      |

| UATI           |       | 1<br>2                | Ak RSVD Type       | Slot1 L     | <b>—</b> | RegCrd  | Val                 |           |           | Doi        | 7              | 8            | INIEITIOP Val |      |      |          |               |         |         |

| -UATI          | Bit # | 1<br>2<br>3           | BE Ak RSVD Type    | Slot1       | SI3      |         | MemOp Val           |           |           | Doi        | 7<br>5<br>-    | el 14.7]     |               |      | :8]  | Poi      |               |         |         |

| ALUATI         | Bit # | 1<br>2<br>3<br>4      | Ak RSVD Type       |             | RSVD SI3 | ReaCrd  | MemOp Val           |           |           | Doi        | 7<br>5<br>-    | el 14.7]     |               |      | :8]  |          | Spare[14:7] 5 | 14 DASA | 15 DASA |

| ALUATI         | Bit # | 1<br>2<br>3<br>4<br>5 | Sz BE Ak RSVD Type | Slot2 Slot1 | RSVD SI3 | ReaCrd  | MetaField MemOp Val |           |           | Doi        | 7<br>5<br>-    | Spare 14.7 8 |               |      | :8]  | Poi      |               |         |         |

| <b>VALUATI</b> | Bit # | 1<br>2<br>3<br>4      | BE Ak RSVD Type    | Slot1       | SI3      |         | MemOp Val           |           |           | Doi        | 7<br>5<br>-    | Spare 14.7 8 |               |      | :8]  | Poi      |               |         |         |

#### CLFlush Definition and Clarification for Biasing **E9**

In section 3.2.4.1.13, make the following updates:

October 2019

## 3.2.4.1.13 ClFlush

This is a request to the Host to invalidate the cache-line specified in the address field. The typical response is GO-I that will be sent from the Host upon completion in memory.

However, the Host may keep tracking the cache line in Shared state if the Core has issued a Monitor to an address belonging in the cache line. Thus, the Device must not rely on CLFlush/GO-I as an only and sufficient condition to flip a cache line from Host to Device bias mode. Instead, the Device must initiate RdOwnNoData and receive an H2D Response of GO-E before it updates its Bias Table and may subsequently access the cache-line without notifying the Host.

Under error conditions, a CIFlush request may receive the line in the Error (GO-Err) state. The device is responsible for handling the error appropriately.

# E10 Buried Cache State Rules and Multiple Access Over CXL.cache

Add a Section 3.2.5.14 for Buried Cache State Rules. Update text in sections 3.2.5.6, 3.2.5.7, and 3.2.5.8

### 3.2.5.14 Buried Cache State Rules

Whenever the Device initiates a new request on CXL.Cache protocol, Buried Cache state refers to the state of the cache line registered in the Device's Coherency engine (DCOH) for which a particular request is being sent.

Buried Cache State Rules:

- <u>The Device must not issue a Read for a cache line if it is buried in Modified, Exclusive, or</u> <u>Shared state.</u>

- <u>The Device must not issue RdOwnNoData if the cache line is buried in Modified or Exclusive</u> <u>state.</u> The Device may request for ownership in Exclusive state as an upgrade request from Shared state.

- The Device must not issue a Read0-Write if the cache line is buried in Modified, Exclusive, or Shared state. The Host typically responds with GO-I (downgraded state) for such requests.

- All \*Evict opcodes must adhere to apropos use case. For example, the Device is allowed to issue DirtyEvict for a cache line only when it is buried in Modified state. For performance benefits, it is recommended that the Device should not silently drop a cache line in Exclusive or Shared state and instead use CleanEvict\* opcodes towards the Host.

- <u>The CacheFlushed Opcode is not specific to a cache line, it is an indication to the Host that all</u> of the Device's caches are flushed. Thus, the Device must not issue CacheFlushed if there is any cache line buried in Modified, Exclusive, or Shared state.

Table 20E describes which Opcodes in D2H requests are allowed for a given Buried Cache State:

#### Table 20E: Allowed Opcodes Per Buried Cache State

| D2H Requests   |                 | Buried Cache State |                  |               |                |  |  |  |  |  |

|----------------|-----------------|--------------------|------------------|---------------|----------------|--|--|--|--|--|

| <u>Opcodes</u> | <u>Semantic</u> | <u>Modified</u>    | <u>Exclusive</u> | <u>Shared</u> | <u>Invalid</u> |  |  |  |  |  |

| RdCurr         | Read            |                    |                  |               | $\checkmark$   |  |  |  |  |  |

| <u>RdOwn</u>   | Read            |                    |                  |               | $\checkmark$   |  |  |  |  |  |

| $\succ$        |                                     |

|----------------|-------------------------------------|

| 6              |                                     |

| 0              |                                     |

| $\bigcirc$     |                                     |

| $\geq$         |                                     |

| $\overline{O}$ |                                     |

| Ē              |                                     |

| 5              | 3.2                                 |

|                | Mult<br>follo<br>proc               |

| _              | whe<br>the                          |

| 7              | cach<br>requ<br>men                 |

| 5              | amb                                 |

|                | 3.2                                 |

| ш              | <del>Mult</del><br><del>issud</del> |

| <u>RdShared</u>         | Read         |              |              |              | $\checkmark$ |

|-------------------------|--------------|--------------|--------------|--------------|--------------|

| RdAny                   | Read         |              |              |              | $\checkmark$ |

| <u>RdOwnNoData</u>      | Read0        |              |              | $\checkmark$ | $\checkmark$ |

| <u>ItoMWr</u>           | Read0-Write  |              |              |              | $\checkmark$ |

| MemWr                   | Read0-Write  |              |              |              | $\checkmark$ |

| <u>CLFlush</u>          | Read0        |              |              |              | $\checkmark$ |

| <u>CleanEvict</u>       | <u>Write</u> |              | $\checkmark$ |              |              |

| DirtyEvict              | <u>Write</u> | $\checkmark$ |              |              |              |

| <u>CleanEvictNoData</u> | <u>Write</u> |              | $\checkmark$ | $\checkmark$ |              |

| WOWrInv                 | <u>Write</u> |              |              |              | $\checkmark$ |

| WOWrInvF                | <u>Write</u> |              |              |              | $\checkmark$ |

| WrInv                   | <u>Write</u> |              |              |              | $\checkmark$ |

| CacheFlushed            | Read0        |              |              |              | $\checkmark$ |

## 3.2.5.6 Multiple Reads to the same cache line

Multiple read requests (cacheable or uncacheable) to the same cache line are allowed <u>only in the</u> following specific cases where host tracking state is consistent regardless of the order requests are processed. The Host can freely reorder requests, so the device is responsible for ordering requests when required. For host memory, multiple RdCurr and/or CLFlush are allowed. For these commands the device ends in I-state, so there is no inconsistent state possible for host tracking of a device cache. With Type 2 devices, in addition to RdCurr and/or CLFlush, multiple RdOwnNoData (bias flip request) is allowed for device attached memory. This case is allowed because with device attached memory the host does not track the device's cache so re-ordering in the host will not create ambiguous state between device and host.

### 3.2.5.7 Multiple Evicts to the same cache line

Multiple Evicts to the same cache line are not allowed. The second Evict may only be issued after the first receives both the CXL.cache GO-I response and the WritePull.

Since Evict guarantees that the evicted cache line is otherwise in the initiating device, it is impossible to send another Evict without an intervening cacheable Read/Read0 request to that address.

<u>Multiple Evicts to the same cache line are not allowed. All Evict messages from the Device provide a guarantee to the Host that the evicted cache line will no longer be present in the Device's caches.</u> Thus, it is impossible to send another Evict for the same cache line without an intervening cacheable <u>Read/Read0 request to that address.</u>

#### 3.2.5.8 Multiple Write Requests to the same cache line

Multiple WrInv/WOWrInv/ItoMWr/MemWr to the same cache line are allowed to be outstanding on CXL.cache. The Host can freely reorder requests, so the device is responsible for ordering requests when required.

Multiple WrInv/WOWrInv/ItoMWr/MemWr to the same cache line are allowed to be outstanding on CXL.cache. The Host can freely reorder requests, and the Device may receive corresponding H2D Responses in reordered fashion. However, it is generally recommended that the Device should issue no more than one outstanding Write request for a given cache line, and order multiple write requests to the same cache line one after another whenever stringent ordering is warranted.

# E11 ARB/MUX Virtual LSM Resolution Table Clarifications

In Section 5.1, modifications are applied to Table 47 and the Note below it, as follows:

Table 47. ARB/MUX Multiple Virtual LSM Resolution Table

| NO                         | Resolved Request from ARB/MUX<br>to Flex Bus Physical Layer<br>(Row = current vLSM[0] state;<br>Column = current vLSM[1] state) | Reset                   | Active | L1.1   | L1.2                | L1.3                       | L1.4                       | SLEEP_L2                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|--------|---------------------|----------------------------|----------------------------|-------------------------|

| F                          | Reset                                                                                                                           | RESET                   | Active | L1.1   | L1.2<br>or<br>lower | L1.3<br><u>or</u><br>lower | L1.4<br><u>or</u><br>lower | SLEEP_L2                |

| $\overline{\triangleleft}$ | Active                                                                                                                          | Active                  | Active | Active | Active              | Active                     | Active                     | Active                  |

| $\square$                  | L1.1                                                                                                                            | L1.1                    | Active | L1.1   | L1.1                | L1.1                       | L1.1                       | L1.1                    |

|                            | L1.2                                                                                                                            | L1.2 <u>or</u><br>lower | Active | L1.1   | L1.2<br>or<br>lower | L1.2<br>or<br>lower        | L1.2<br>or<br>lower        | L1.2 <u>or</u><br>lower |

| Z                          | L1.3                                                                                                                            | L1.3 <u>or</u><br>lower | Active | L1.1   | L1.2<br>or<br>lower | L1.3<br>or<br>lower        | L1.3<br>or<br>lower        | L1.3 <u>or</u><br>lower |

| Ш                          | L1.4                                                                                                                            | L1.4 <u>or</u><br>lower | Active | L1.1   | L1.2<br>or<br>lower | L1.3<br>or<br>lower        | L1.4<br>or<br>lower        | L1.4 <u>or</u><br>lower |

|                            | SLEEP_L2                                                                                                                        | SLEEP_L2                | Active | L1.1   | L1.2<br>or<br>lower | L1.3<br>or<br>lower        | L1.4<br><u>or</u><br>lower | SLEEP_L2                |

Note: Table 47 is presented as a suggestion, not a requirement.

October 2019

# E12 Text Updates in CXLCM Link Layer Chapter

In sections 4.2.8.1 and 4.2.7, make the following updates:

WrPtr: This indexes the entry of the LLRB that will record the next new flit. When an entity sends a flit, it copies that flit into the LLRB entry indicated by the WrPtr and then increments the WrPtr by one (modulo the size of the LLRB). This is implemented using a wrap-around counter that wraps around to 0 after reaching the depth of the LLRB. Certain LLCTRL flits do not affect the WrPtr. WrPtr stops incrementing after receiving an error indication at the remote entity (RETRY.Req message), until normal operation resumes again (all flits from the LLRB have been retransmitted). WrPtr is initialized to 0 and is incremented only when a flit is put

Implementation Note: WrPtr may continue to increment after receiving Retry.Req message if there are pre-scheduled All Data Flits that are not yet sent over the link. This implementation will ensure that All Data Flits not interleaved with other flits are correctly logged into the Link

<section-header><section-header><section-header><text><text><text><text> NumFreeBuf: This indicates the number of free LLRB entries at the entity. NumFreeBuf is decremented by 1 whenever an LLRB entry is used to store a transmitted flit. NumFreeBuf is incremented by the value encoded in the Ack/ Full\_Ack field of a received flit. NumFreeBuf is initialized at reset time to the size of the LLRB. The maximum number of retry queues at any entity is limited to 255 (8 bit counter). Also, note that the retry buffer at any entity is never filled to its capacity, therefore NumFreeBuf is never '0. If there is only 1 retry buffer entry available, then the sender cannot send an ACK bearing flit which may either be a protocol flit or an LLCRD Control flit. This restriction is required to avoid ambiguity between a full or an empty retry buffer during a retry sequence that may result into incorrect operation. This implies if there are only 2 retry buffer entries left (NumFreeBuf = 2), then the sender can send an Ack bearing flit only if the outgoing flit encodes a value of at least 1 (which may be a Protocol flit with Ak bit set), else a LLCRD control flit is sent with Full Ack value of at least 1. This is required to avoid deadlock at the link layer due to retry buffer becoming full at both entities on a link and their inability to send ACK through header flits.

The Tx portion of the Link Layer must wait until the Rx portion of the Link Layer has received at least one valid flit that is CRC clean before sending the LLCTRLINIT.Param flit. Before this condition is met, the Link Layer must transmit only LLCTRL-Retry flits, i.e.,

# E13 Fixed Typos in Figure depicting Write from Host

Update Figure 39, Red arrows from Device Memory Controller to Device Memory should be MemWr\* and Cmp

#### Figure 39. Write from Host

Updates to S2M/D2H G5 format from 3 NDR to 2 NDR messages. The global flit rules in section 4.2.5 restrict total S2M NDR to 2 total per flit which take precedence, so it is impossible to make use of 3rd NDR message in the S2M/D2H G5 format. Changing the G5 format to only include 2 NDR is done to ensure consistency and avoid confusion.

*First change is to Table 40. Second change is to change G5 format in Figure 70 to include only the first 2 NDR messages converting the 3rd to RSVD bits.*

#### Table 40. D2H/S2M Slot Formats

| Format to Req Type Mapping | D2H/S2M                                                   |      |

|----------------------------|-----------------------------------------------------------|------|

|                            | Туре                                                      | Size |

| НО                         | CXL.cache Data Header + 2 CXL.cache Resp +<br>CXL.mem NDR | 85   |

| H1                         | CXL.cache Req + CXL.cache Data Header                     | 96   |

| H2                         | 4 CXL.cache Data Header + CXL.cache Resp                  | 88   |

| НЗ                         | CXL.mem DRS Header + CXL.mem NDR                          | 68   |

| H4                         | 2 CXL.mem NDR                                             | 56   |

| Н5 | 2 CXL.mem DRS Header                                      | 80                        |

|----|-----------------------------------------------------------|---------------------------|

| G0 | CXL.cache/ CXL.mem Data Chunk                             | 128                       |

| G1 | CXL.cache Req + 2 CXL.cache Resp                          | 119                       |

| G2 | CXL.cache Req + CXL.cache Data Header +<br>CXL.cache Resp | 116                       |

| G3 | 4 CXL.cache Data Header                                   | 68                        |

| G4 | CXL.mem DRS Header + 2 CXL.mem NDR                        | 96                        |

| G5 | <mark>3-</mark> 2 CXL.mem NDR                             | <mark>84<u>-</u>56</mark> |

| G6 | 3 CXL.mem DRS Header                                      | 120                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | G          | J         |           |            |      |      |      |      |      |      |      |      | C      | X        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-----------|-----------|------------|------|------|------|------|------|------|------|------|--------|----------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | G          | 1         |           |            |      |      |      |      |      |      |      |      | С      | x        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | Gź         | 2         |           |            |      |      |      |      |      |      |      |      | C<br>C | X        |

| $\succ$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | G          | 3         |           |            |      |      |      |      |      |      |      |      | 4      | C        |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | G4         | 4         |           |            |      |      |      |      |      |      |      |      | С      | x        |

| $\cap$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | G!         | 5         |           |            |      |      |      |      |      |      |      |      | ŝ      | <u> </u> |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | G          | 5         |           |            |      |      |      |      |      |      |      |      | 3      | C        |

| Figure 70.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | G5        |            | <u>2</u>  | S2        | 2M         | NI   | DR   |      |      |      |      |      |      |        |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |            |           |           |            | yte  |      |      |      |      |      |      |      |        |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 2       | 3          | 4         | 5         | 6          | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15     |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |            | MetaField |           | ~          |      |      |      |      |      |      |      |      |        |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | Spare[3:0] |           |           | Tag[15:12] |      |      |      |      |      |      |      |      |        |          |

| 2 Kemob                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | Sp         | MetaValue |           | Ta         |      |      |      |      |      |      |      |      |        |          |

| 3 3 3 4 Bit #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Tag[15:8] |            | Met       | Tag[11:4] |            | RSVD   |          |

| Perfect of the second s | Tag       | Val        |           | Taç       |            | Ř    | Ř    | Ř    | Ä    | Ř    | ΙΨ.  | æ    | ГЙ.  | Ϋ́     |          |