# Errata for the Compute Express Link<sup>™</sup> (CXL<sup>™</sup>) Specification Revision 1.1

February 2020

### LEGAL NOTICE FOR THIS PUBLICLY-AVAILABLE SPECIFICATION FROM COMPUTE EXPRESS LINK CONSORTIUM, INC.

### © 2019-2020 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED.

This CXL **Specification Revision 1.1** (this "<u>CXL Specification</u>" or this "<u>document</u>") is owned by and is proprietary to Compute Express Link Consortium, Inc., a Delaware nonprofit corporation (sometimes referred to as "<u>CXL</u>" or the "<u>CXL Consortium</u>" or the "<u>Company</u>") and/or its successors and assigns.

### NOTICE TO USERS WHO ARE MEMBERS OF THE CXL CONSORTIUM:

If you are a Member of the CXL Consortium (sometimes referred to as a "<u>CXL Member</u>"), and even if you have received this publicly-available version of this CXL Specification after agreeing to CXL Consortium's Evaluation Copy Agreement (a copy of which is available <u>https://www.computeexpresslink.org/download-the-specification</u>, each such CXL Member must also be in compliance with all of the following CXL Consortium documents, policies and/or procedures (collectively, the "<u>CXL Governing Documents</u>") in order for such CXL Member's use and/or implementation of this CXL Specification to receive and enjoy all of the rights, benefits, privileges and protections of CXL Consortium membership: (i) CXL Consortium's Bylaws; (iii) any and all other CXL Consortium policies and procedures; and (iv) the CXL Member's Participation Agreement.

### NOTICE TO NON-MEMBERS OF THE CXL CONSORTIUM:

If you are <u>not</u> a CXL Member and have received this publicly-available version of this CXL Specification, your use of this document is subject to your compliance with, and is limited by, all of the terms and conditions of the CXL Consortium's Evaluation Copy Agreement (a copy of which is available at <u>https://www.computeexpresslink.org/download-the-specification</u>).

In addition to the restrictions set forth in the CXL Consortium's Evaluation Copy Agreement, any references or citations to this document must acknowledge the Compute Express Link Consortium, Inc.'s sole and exclusive copyright ownership of this CXL Specification. The proper copyright citation or reference is as follows: "© 2019-2020 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED." When making any such citation or reference to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of the Compute Express Link Consortium, Inc.

Except for the limited rights explicitly given to a non-CXL Member pursuant to the explicit provisions of the CXL Consortium's Evaluation Copy Agreement which governs the publicly-available version of this CXL Specification, nothing contained in this CXL Specification shall be deemed as granting (either expressly or impliedly) to any party that is <u>not</u> a CXL Member: (ii) any kind of license to implement or use this CXL Specification or any portion or content described or contained therein, or any kind of license in or to any other intellectual property owned or controlled by the CXL Consortium, including without limitation any trademarks of the CXL Consortium.; or (ii) any benefits and/or rights as a CXL Member under any CXL Governing Documents.

### LEGAL DISCLAIMERS FOR ALL PARTIES:

THIS DOCUMENT AND ALL SPECIFICATIONS AND/OR OTHER CONTENT PROVIDED HEREIN IS PROVIDED ON AN "**AS IS**" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, COMPUTE EXPRESS LINK CONSORTIUM, INC. (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NON-INFRINGEMENT. In the event this CXL Specification makes any references (including without limitation any incorporation by reference) to another standard's setting organization's or any other party's ("<u>Third Party</u>") content or work, including without limitation any specifications or standards of any such Third Party ("<u>Third Party Specification</u>"), you are hereby notified that your use or implementation of any Third Party Specification: (i) is not governed by any of the CXL Governing Documents; (ii) may require your use of a Third Party's patents, copyrights or other intellectual property rights, which in turn may require you to independently obtain a license or other consent from that Third Party in order to have full rights to implement or use that Third Party Specification; and/or (iii) may be governed by the intellectual property policy or other policies or procedures of the Third Party which owns the Third Party Specification. Any trademarks or service marks of any Third Party which may be referenced in this CXL Specification is owned by the respective owner of such marks.

### NOTICE TO ALL PARTIES REGARDING THE PCI-SIG UNIQUE VALUE PROVIDED IN THIS CXL SPECIFICATION:

NOTICE TO USERS: THE UNIQUE VALUE THAT IS PROVIDED IN THIS CXL SPECIFICATION IS FOR USE IN VENDOR DEFINED MESSAGE FIELDS, DESIGNATED VENDOR SPECIFIC EXTENDED CAPABILITIES, AND ALTERNATE PROTOCOL NEGOTIATION ONLY AND MAY NOT BE USED IN ANY OTHER MANNER, AND A USER OF THE UNIQUE VALUE MAY NOT USE THE UNIQUE VALUE IN A MANNER THAT (A) ALTERS, MODIFIES, HARMS OR DAMAGES THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF, OR (B) COULD OR WOULD REASONABLY BE DETERMINED TO ALTER, MODIFY, HARM OR DAMAGE THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF (FOR PURPOSES OF THIS NOTICE, "<u>PCI-SIG ECOSYSTEM</u>" MEANS THE PCI-SIG SPECIFICATIONS, MEMBERS OF PCI-SIG AND THEIR ASSOCIATED PRODUCTS AND SERVICES THAT INCORPORATE ALL OR A PORTION OF A PCI-SIG SPECIFICATION AND EXTENDS TO THOSE PRODUCTS AND SERVICES INTERFACING WITH PCI-SIG MEMBER PRODUCTS AND SERVICES). Errata for the Compute Express Link Specification Rev 1.1

The copyright in this Specification is owned by the CXL Consortium. Use of this Specification and any related intellectual property (collectively, the "Specification"), is governed by the terms of the Promoter, Contributor or Adopter Agreement (collectively, "Agreement") as available by request from admin@computeexpresslink.org. This specification may only be used by (a) a party to the Agreement, and in compliance with its terms, or (b) non-parties to the Agreement who have accepted an approved disclaimer of liability and acknowledgement of IP protections.

Any use or implementation of this specification is expressly subject to the terms and conditions described in the CXL Promoter, Contributor, and/or Adopter Agreement, as appropriate for your status. The implementation or use of industry specifications made available by any other standards body, such as PCIe, if referenced in a CXL Final Specification (as such term is defined in those agreements) is not governed by CXL policies and procedures, and may be subject to patent, copyright, and other intellectual property right protection (collectively "IPR"). Licensing of such IPR in a referenced industry specification.

This document is provided 'as is' with no warranties, express or implied, including any warranty of merchantability, fitness for a particular purpose, noninfringement of any third-party intellectual property rights, or any warranty otherwise arising out of any proposal, specification or sample. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

CXL is a trademark of the CXL Consortium

All other product names are trademarks, registered trademarks, or servicemarks of their respective owners.

©2020 CXL

### Contents

| E1  | CXL.AL and Flex Bus.AL Typo 5                                 |

|-----|---------------------------------------------------------------|

| E2  | Control SKP Ordered Set Frequency 5                           |

| E3  | CXL Downstream Port Supported PCIe Capabilities               |

| E4  | CXL Upstream Port Supported PCIe Capabilities                 |

| E5  | CXL Power Management Messages 7                               |

| E6  | CXL Configuration Space Registers 8                           |

| E7  | CXLCM Flit Packing Rules                                      |

| E8  | CXLCM Slot Format Diagram Updates                             |

| E9  | CLFlush Definition and Clarification for Biasing15            |

| E10 | Buried Cache State Rules and Multiple Access Over CXL.cache16 |

| E11 | ARB/MUX Virtual LSM Resolution Table Clarifications18         |

| E12 | Text Updates in CXLCM Link Layer Chapter19                    |

| E13 | Fixed Typos in Figure depicting Write from Host19             |

| E14 | S2M/D2H G5 Format Update20                                    |

| E15 | PM timeout value21                                            |

| E16 | Figure 65 Title                                               |

| E17 | Implied EDS and Variable Length NULL Flits                    |

| E18 | CRC bit location                                              |

| E19 | Text Updates in CXLCM Link Layer Chapter (part 2)25           |

| E20 | Appendix A.2 fix for Bias Flip26                              |

| E21 | Description of RSP_PRE26                                      |

| E22 | CXL Downstream Port Supported PCIe Capabilities (part 2)27    |

| E23 | CXL Upstream Port Supported PCIe Capabilities (part 2)28      |

| E24 | Clarify Logging of Errors Detected by Upstream Port29         |

| E25 | Clarification to Force LLCRD definition                       |

| E26 | CRC bit location - Version 2                                  |

| E27 | CXL Vendor ID                                                 |

# **Revision History**

| Revision | Description                                                                                                                  | Date          |

|----------|------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.0      | First Release: Errata E1-E16.                                                                                                | October 2019  |

| 2.0      | Second Release: Added E17 and E18.                                                                                           | December 2019 |

| 3.0      | Third Release: Added E19-E24.                                                                                                | January 2020  |

| 4.0      | Fourth Release: Added E25-E27. Note E26 replaces E18 due to errors in E18 that incorrectly changed the CRC data mask values. | February 2020 |

# E1 CXL.AL and Flex Bus.AL Typo

*In general, Flex Bus.AL should be substituted with Flex Bus.CXL throughout the specification document. Additionally, in section 11.4, make the following changes:*

### **11.4 CXL Viral Handling**

### . . .

When a CXL<del>.AL</del> device goes into Viral, the upstream CXL.io shall perform the following:

- Master Abort Upstream Requests

- Completer Abort Upstream Completions

- Signal Failed Response for Downstream Completions

# E2 Control SKP Ordered Set Frequency

In section 6.7.1, make the following changes:

### 6.7.1 Control SKP Ordered Frequency and L1/Recovery Entry

In Flex Bus.CXL mode, if sync header bypass is enabled, the following rules apply:

• After the SDS, the physical layer must schedule a control SKP Ordered Set or SKP Ordered Set after every 340 data blocks, unless it is exiting the data stream. Note: The control SKP OSs are alternated with regular SKP OSs <u>at 16 GT/s or higher speeds</u>; <u>at 8 GT/s</u>, <u>only SKP OSs are scheduled</u>.

# E3 CXL Downstream Port Supported PCIe Capabilities

In section 7.2.1.1, Table 60, make the following changes:

Table 60. CXL Downstream Port Supported PCIe Capabilities and Extended Capabilities

| Supported PCIe Capabilities<br>and Extended Capabilities | Exceptions <sup>1</sup>                                                                                                                    | Notes                                            |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| PCI Express Capability                                   | Slot Capabilities, Slot Control, Slot<br>Status, Slot Capabilites 2, Slot<br>Control 2, and Slot Status 2<br>registers are not applicable. | None                                             |

| PCI Power Management Capability                          | None                                                                                                                                       | None                                             |

| MSI Capability                                           | None                                                                                                                                       | None                                             |

| Advanced Error Reporting<br>Extended Capability          | None                                                                                                                                       | Required for CXL despite being optional for PCIe |

| ACS Extended Capability                                  | None                                                                                                                                       | None                                             |

| Multicast Extended Capability                            | None                                                                                                                                       | None                                             |

| Downstream Port Containment<br>Extended Capability        | None | None                                                                             |

|-----------------------------------------------------------|------|----------------------------------------------------------------------------------|

| Designated Vendor-Specific<br>Extended Capability (DVSEC) | None | Please refer to section Figure<br>7.2.1.3 for Flex Bus Port DVSEC<br>definition. |

| Secondary PCI Express<br>Extended Capability              | None | None                                                                             |

| Data Link Feature Extended<br>Capability                  | None | None                                                                             |

| Physical Layer 16.0 GT/s<br>Extended Capability           | None | None                                                                             |

| Physical Layer 32.0 GT/s<br>Extended Capability           | None | None                                                                             |

| Lane Margining at the Receiver<br>Extended Capability     | None | None                                                                             |

| Alternate Protocol Extended<br>Capability                 | None | None                                                                             |

# E4 CXL Upstream Port Supported PCIe Capabilities

In section 7.2.1.2, Table 61, make the following changes:

### Table 61. CXL Upstream Port Supported PCIe Capabilities and Extended Capabilities

| Support PCIe Capabilties and<br>Extended Capabilties | Exceptions <sup>1</sup> | Notes                                             |

|------------------------------------------------------|-------------------------|---------------------------------------------------|

| PCI Express Capability                               | None                    | N/ANone                                           |

| Advanced Error Reporting<br>Extended Capability      | None                    | Required for CXL despite being optional for PCIe. |

| Multicast Extended Capability                        | None                    | N/A                                               |

| Virtual Channel Extended<br>Capability               | None                    | VC0 and VC1                                       |

| Designated Vendor-Specific<br>Extended Capability (DVSEC) | None | Please refer to section Figure<br>7.2.1.3 for Flex Bus Port DVSEC<br>definition. |

|-----------------------------------------------------------|------|----------------------------------------------------------------------------------|

| Secondary PCI Express Extended<br>Capability              | None | None                                                                             |

| <u>Data Link Feature Extended</u><br><u>Capability</u>    | None | None                                                                             |

| Physical Layer 16.0 GT/s Extended<br>Capability           | None | None                                                                             |

| Physical Layer 32.0 GT/s Extended<br>Capability           | None | None                                                                             |

| Lane Margining at the Receiver<br>Extended Capability     | None | None                                                                             |

| Alternate Protocol Extended<br>Capability                 | None | None                                                                             |

# E5 CXL Power Management Messages

In section 3.1.2, Table 3, make the following changes:

| Field         | Description                                                                                                                                                                                                                                                                                                                                                      | Notes                                                                                                                                                                                                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Payload[95:0] | <pre> AGENT_INFO: If Param.Index == 0, 7:0 - REVISION_ID CAPABILITY_VECTOR 0 - Always set to indicate support for CXL 1.1 PM messages 7:1 - Reserved 15:8 - PrepType 0x00 =&gt; General Prep All others reserved 0x01 =&gt; Early Prep; 0x02 =&gt; Reset Entry Start (first checkpoint for CXL device blocks during a Reset event/power state transition);</pre> | CXL Agent must<br>treat the<br>TARGET_AGENT_ID<br>field as Reserved<br>when returning<br>credits to Host.<br>Only Index 0 is<br>defined for<br>AGENT_INFO, all<br>other Index values<br>are reserved. |

| 0x03 => Link Turnoff (typically the last<br>checkpoint during a Reset event/power state<br>transition); |  |

|---------------------------------------------------------------------------------------------------------|--|

| 17:16 - <u>Reserved Phase</u>                                                                           |  |

| <del>0x00 =&gt; Phase 0</del>                                                                           |  |

| <del>0x01 =&gt; Phase 1</del>                                                                           |  |

| <del>0x02 =&gt; Phase 2</del>                                                                           |  |

| <del>0x03 =&gt; Phase 3</del>                                                                           |  |

| All others reserved                                                                                     |  |

|                                                                                                         |  |

| PMREQ:                                                                                                  |  |

| 31:0 - PCIe LTR format                                                                                  |  |

| All others reserved                                                                                     |  |

# E6 CXL Configuration Space Registers

In chapter 7, Table 57, make the following changes:

| Attribute | Description                                                             |

|-----------|-------------------------------------------------------------------------|

| RO        | Read Only                                                               |

| RO-V      | Read-Only-Variant                                                       |

| RW        | Read-Write                                                              |

| RWS       | Read-Write-Sticky                                                       |

| RWO       | Read-Write-Onee-To_Lock<br>Field becomes RO after<br>writing one to it. |

| RWL       | Read-Write-Lockable                                                     |

| RW1CS     | Read-Write-One-To-Clear-<br>Sticky                                      |

In section 7.1.1.3, make the following changes:

| Bit  | Attributes     | Description                                                                                                                                                                                                                                                                                          |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:0 | N/A            | Reserved (RSVD).                                                                                                                                                                                                                                                                                     |

| 14   | RW <u>1C</u> S | Viral_Status: When set, indicates that the CXL device has entered Viral self-<br>isolation mode. See Section 11.4, "CXL Viral Handling" on page 198 for more<br>details.<br><u>Note: Viral condition is cleared by warm reset or cold reset, but Viral Status bit survives</u><br><u>warm reset.</u> |

| 15   | N/A            | Reserved (RSVD).                                                                                                                                                                                                                                                                                     |

# E7 CXLCM Flit Packing Rules

In Section 4.2.5, add following Flit Packing Rules that clarify Bit Ordering requirements.

### 4.2.5 Flit Packing Rules

. . .

- For a given slot, lower bit positions are defined as bit positions that appear starting from lower order Byte #. That is, bits are ordered starting from (Byte# 0, Bit# 0) through (Byte #15, Bit# 7).

- For multi-bit message fields like Address[MSB:LSB], lesser significant bits will appear in lower order bit positions.

- Message ordering within a flit is based on flit bit numbering, i.e. the earliest messages are placed at the lowest flit bit positions and progressively later messages are placed at progressively higher bit positions. Examples: An M2S Req 0 packed in Slot 0 precedes an M2S Req 1 packed in Slot 1. Similarly, a Snoop packed in Slot 1 follows a GO packed in Slot 0, and this ordering must be maintained. Finally, for Header Slot Format H1, an H2D Response packed starting from Byte# 7 precedes an H2D Response packed starting from Byte# 11.

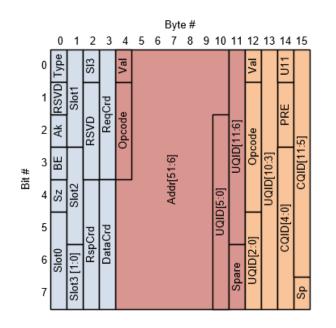

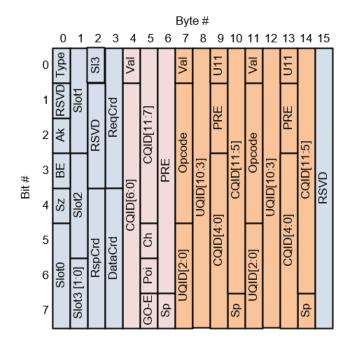

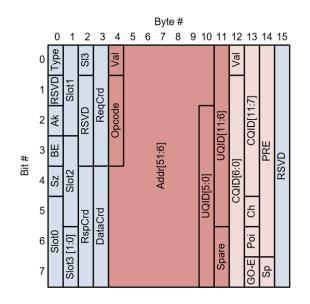

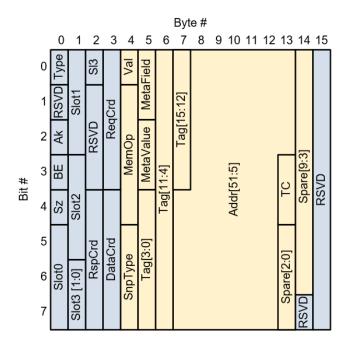

# E8 CXLCM Slot Format Diagram Updates

In Section 4.2.3, following diagrams for Header Slot Formats need to be updated to show Slot 3 bit encodings in correct bit positions. Also fixed Figure 50, which showed Addr[51:6] in CXL1.1, but should have show Addr[51:5] to match address bits required for M2S Req.

### 4.2.3.2 H2D and M2S Formats

### Figure 45. H0 - H2D Req + H2D Resp

### Figure 46. H1 - H2D Data Header + H2D Resp + H2D Resp

### Figure 47. H2 - H2D Req + H2D Data Header

### Figure 48. H3 - 4 H2D Data Header

### Byte # 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 VDe SI3 Val Val /al 0 a) 1 RSVD Slot ReqCrd CQID[11:7] CQID[11:7] CQID[11:7 CQID[11:7 RSVD 2 ¥ PRE PRE PRE PRE 3 出 CQID[6:0] CQID[6:0] CQID[6:0] CQID[6:0 Slot2 4 S 5 Ч Ч RspCrd ප ප DataCrd Slot0 Poi Poi Poi Poi [1:0] Slot3 GO-E GO-E GO-E GO-E Sp Sp Sp Sp 7

Bit #

### Figure 49. H4 - M2S RwD Header

### Figure 50. H5 - M2S Req

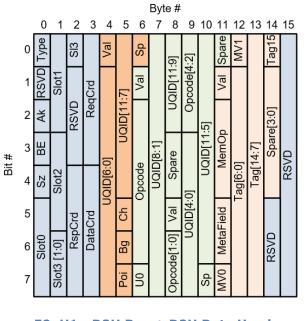

### 4.2.3.3 D2H and S2M Formats

Figure 58. H0 - D2H Data Header + 2 D2H Resp + S2M NDR

### Figure 59. H1 - D2H Req + D2H Data Header

### Figure 60. H2 - 4 D2H Data Header + D2H Resp

### Figure 61. H3 - S2M DRS Header + S2M NDR

|       |   |       |             |        |         |           |                 |                       | Byt        | te #                    |           |           |           |            |      |      |      |

|-------|---|-------|-------------|--------|---------|-----------|-----------------|-----------------------|------------|-------------------------|-----------|-----------|-----------|------------|------|------|------|

|       |   | 0     | 1           | 2      | 3       | 4         | 5               | 6                     | 7          | 8                       | 9         | 10        | 11        | 12         | 13   | 14   | 15   |

|       | 0 | Type  |             | SI3    |         | Val       |                 |                       | Poi        |                         | Val       |           |           |            |      |      |      |

|       | 1 | RSVD  | Slot1       |        | ReqCrd  | d         |                 |                       |            |                         | d         |           |           | Spare[3:0] |      |      |      |

|       | 2 | Ak    |             | RSVD   | Re      | MemOp     | [7:0]<br>15:8]  | Tag[7:0]<br>Tag[15:8] |            |                         | MemOp     |           |           | Spar       | RSVD |      |      |

| Bit # | 3 | BE    |             |        |         |           |                 |                       | Spare[6:0] | are[0:0]<br>Spare[14:7] |           | Tag[7:0]  | Tag[15:8] |            |      | RSVD | RSVD |

| ä     | 4 | Sz    | Slot2       | Crd    |         | MetaField | Tag             |                       |            | Spare                   | Field     | Tag       | Tag[      |            | RS   | RS   | RS   |

|       | 5 |       |             |        | DataCrd |           | MetaValue Metal |                       |            | S                       |           | MetaField |           |            | ٧D   |      |      |

|       | 6 | Slot0 | Slot3 [1:0] | RspCrd | Data    | /alue     |                 |                       |            |                         | MetaValue |           |           | RSVD       |      |      |      |

|       | 7 |       | Slot3       |        |         | Meta∖     |                 |                       |            |                         | Meta      |           |           |            |      |      |      |

# Evaluation Copy

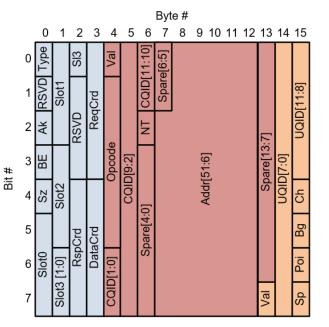

### Figure 62. H4 - 2 S2M NDR

|       |   |       |             |        |         |                |          |             | Byt          | e #        |           |            |            |      |       |           |      |       |  |

|-------|---|-------|-------------|--------|---------|----------------|----------|-------------|--------------|------------|-----------|------------|------------|------|-------|-----------|------|-------|--|

|       |   | 0     | 1           | 2      | 3       | 4              | 5        | 6           | 7            | 8          | 9         | 10         | 11         | 12   | 13    | 14        | 15   |       |  |

|       | 0 | Type  |             | SI3    |         | Val            |          |             |              | Field      |           |            |            |      |       |           |      |       |  |

|       | 1 | RSVD  | Slot1       |        | Crd     | MemOp<br>[7:0] |          |             |              | Spare[3:0] | MetaField |            | Fag[15:12] |      |       |           |      |       |  |

|       | 2 | Ak    |             | RSVD   | ReqCrd  |                |          |             |              |            |           |            |            |      | Spare | MetaValue |      | Tag[1 |  |

| Bit # | 3 | BE    |             |        |         |                | Tag[7:0] | Tag[15:8]   |              | Meta       | [ag[11:4] |            | RSVD       | RSVD | RSVD  | RSVD      | RSVD |       |  |

| Bi    | 4 | Sz    | Slot2       |        |         | Field          | MetaFie  | Tag <br>Tag | Tag <br>Tag[ | Val        | Tag['     | Tag        |            | RS   | RS    | RS        | RS   | RS    |  |

|       | 5 |       |             | Crd    | aCrd    | Meta           |          |             |              | Tag[3:0]   |           | ə[3:0]     |            |      |       |           |      |       |  |

|       | 6 | Slot0 | Slot3 [1:0] | RspCrd | DataCrd | MetaValue      |          |             | MemOp        | Tag        |           | Spare[3:0] |            |      |       |           |      |       |  |

|       | 7 |       | Slot3       |        |         | Meta           |          |             | 2            |            |           |            |            |      |       |           |      |       |  |

### Figure 63. H5 - 2 S2M DRS

|       |   | Byte # |             |        |         |           |          |           |            |             |           |                       |        |                         |                     |      |      |  |

|-------|---|--------|-------------|--------|---------|-----------|----------|-----------|------------|-------------|-----------|-----------------------|--------|-------------------------|---------------------|------|------|--|

|       |   | 0      | 1           | 2      | 3       | 4         | 5        | 6         | 7          | 8           | 9         | 10                    | 11     | 12                      | 13                  | 14   | 15   |  |

|       | 0 | Type   |             | SI3    |         | Val       |          | Poi       |            | Val         |           |                       | Poi    |                         |                     |      |      |  |

|       | 1 | RSVD   | Slot1       |        | Crd     | MemOp     |          |           |            |             |           |                       |        |                         |                     |      |      |  |

|       | 2 | Ak     |             | RSVD   | ReqCrd  |           |          |           | Spare[6:0] | Spare[14:7] | MemOp     | Tag[7:0]<br>Tag[15:8] |        |                         |                     |      |      |  |

| Bit # | 3 | BE     |             |        |         |           | Tag[7:0] | Tag[15:8] |            |             |           |                       | [15:8] | Tag[15:8]<br>Spare[6:0] | Spare[14:7]<br>RSVD | RSVD | RSVD |  |

| Bi    | 4 | Sz     | Slot2       |        | DataCrd | MetaField | Tag      |           |            |             | Field     |                       | Tag    |                         |                     |      |      |  |

|       | 5 |        |             | RspCrd |         | Meta      |          |           |            |             | Meta      |                       |        |                         |                     |      |      |  |

|       | 6 | Slot0  | Slot3 [1:0] | Rsp    |         | MetaValue |          |           |            |             | MetaValue |                       |        |                         |                     |      |      |  |

|       | 7 |        | Slot3       |        |         | Meta      |          |           |            |             | Meta      |                       |        |                         |                     |      |      |  |

# E9 CLFlush Definition and Clarification for Biasing

In section 3.2.4.1.13, make the following updates:

### 3.2.4.1.13 ClFlush

This is a request to the Host to invalidate the cache-line specified in the address field. The typical response is GO-I that will be sent from the Host upon completion in memory.

However, the Host may keep tracking the cache line in Shared state if the Core has issued a Monitor to an address belonging in the cache line. Thus, the Device must not rely on CLFlush/GO-I as an only and sufficient condition to flip a cache line from Host to Device bias mode. Instead, the Device must initiate RdOwnNoData and receive an H2D Response of GO-E before it updates its Bias Table and may subsequently access the cache-line without notifying the Host.

Under error conditions, a CIFlush request may receive the line in the Error (GO-Err) state. The device is responsible for handling the error appropriately.

# E10 Buried Cache State Rules and Multiple Access Over CXL.cache

*Add a Section 3.2.5.14 for Buried Cache State Rules. Update text in sections 3.2.5.6, 3.2.5.7, and 3.2.5.8*

### 3.2.5.14 Buried Cache State Rules

Whenever the Device initiates a new request on CXL.Cache protocol, Buried Cache state refers to the state of the cache line registered in the Device's Coherency engine (DCOH) for which a particular request is being sent.

Buried Cache State Rules:

- <u>The Device must not issue a Read for a cache line if it is buried in Modified, Exclusive, or</u> <u>Shared state.</u>

- <u>The Device must not issue RdOwnNoData if the cache line is buried in Modified or Exclusive</u> <u>state.</u> The Device may request for ownership in Exclusive state as an upgrade request from <u>Shared state.</u>

- The Device must not issue a Read0-Write if the cache line is buried in Modified, Exclusive, or Shared state. The Host typically responds with GO-I (downgraded state) for such requests.

- <u>All \*Evict opcodes must adhere to apropos use case.</u> For example, the Device is allowed to issue DirtyEvict for a cache line only when it is buried in Modified state. For performance benefits, it is recommended that the Device should not silently drop a cache line in Exclusive or Shared state and instead use CleanEvict\* opcodes towards the Host.

- <u>The CacheFlushed Opcode is not specific to a cache line, it is an indication to the Host that all of the Device's caches are flushed. Thus, the Device must not issue CacheFlushed if there is any cache line buried in Modified, Exclusive, or Shared state.</u>

Table 20E describes which Opcodes in D2H requests are allowed for a given Buried Cache State:

### Table 20E: Allowed Opcodes Per Buried Cache State

| D2H Requests   |                 | Buried Cache State |                  |               |                |  |  |  |  |

|----------------|-----------------|--------------------|------------------|---------------|----------------|--|--|--|--|

| <u>Opcodes</u> | <u>Semantic</u> | <u>Modified</u>    | <u>Exclusive</u> | <u>Shared</u> | <u>Invalid</u> |  |  |  |  |

| RdCurr         | Read            |                    |                  |               | $\checkmark$   |  |  |  |  |

| <u>RdOwn</u>   | Read            |                    |                  |               | <u>√</u>       |  |  |  |  |

| RdShared                | Read         |              |              |              | ⊻            |

|-------------------------|--------------|--------------|--------------|--------------|--------------|

| <u>RdAny</u>            | Read         |              |              |              | $\checkmark$ |

| RdOwnNoData             | Read0        |              |              | $\checkmark$ | $\checkmark$ |

| <u>ItoMWr</u>           | Read0-Write  |              |              |              | $\checkmark$ |

| <u>MemWr</u>            | Read0-Write  |              |              |              | $\checkmark$ |

| <u>CLFlush</u>          | Read0        |              |              |              | $\checkmark$ |

| <u>CleanEvict</u>       | <u>Write</u> |              | $\checkmark$ |              |              |

| <u>DirtyEvict</u>       | <u>Write</u> | $\checkmark$ |              |              |              |

| <u>CleanEvictNoData</u> | <u>Write</u> |              | $\checkmark$ | $\checkmark$ |              |

| <u>WOWrInv</u>          | <u>Write</u> |              |              |              | $\checkmark$ |

| <u>WOWrInvF</u>         | <u>Write</u> |              |              |              | $\checkmark$ |

| <u>WrInv</u>            | <u>Write</u> |              |              |              | <u>√</u>     |

| <b>CacheFlushed</b>     | Read0        |              |              |              | <u>√</u>     |

### 3.2.5.6 Multiple Reads to the same cache line

Multiple read requests (cacheable or uncacheable) to the same cache line are allowed <u>only in the</u> following specific cases where host tracking state is consistent regardless of the order requests are processed. The Host can freely reorder requests, so the device is responsible for ordering requests when required. For host memory, multiple RdCurr and/or CLFlush are allowed. For these commands the device ends in I-state, so there is no inconsistent state possible for host tracking of a device cache. With Type 2 devices, in addition to RdCurr and/or CLFlush, multiple RdOwnNoData (bias flip request) is allowed for device attached memory. This case is allowed because with device attached memory the host does not track the device's cache so re-ordering in the host will not create ambiguous state between device and host.

### 3.2.5.7 Multiple Evicts to the same cache line

Multiple Evicts to the same cache line are not allowed. The second Evict may only be issued after the first receives both the CXL.cache GO-I response and the WritePull.

Since Evict guarantees that the evicted cache line is otherwise in the initiating device, it is impossible to send another Evict without an intervening cacheable Read/Read0 request to that address.

<u>Multiple Evicts to the same cache line are not allowed. All Evict messages from the Device provide a guarantee to the Host that the evicted cache line will no longer be present in the Device's caches.</u> Thus, it is impossible to send another Evict for the same cache line without an intervening cacheable Read/Read0 request to that address.

### 3.2.5.8 Multiple Write Requests to the same cache line

Multiple WrInv/WOWrInv/ItoMWr/MemWr to the same cache line are allowed to be outstanding on CXL.cache. The Host can freely reorder requests, so the device is responsible for ordering requests when required.

Multiple WrInv/WOWrInv/ItoMWr/MemWr to the same cache line are allowed to be outstanding on CXL.cache. The Host can freely reorder requests, and the Device may receive corresponding H2D Responses in reordered fashion. However, it is generally recommended that the Device should issue no more than one outstanding Write request for a given cache line, and order multiple write requests to the same cache line one after another whenever stringent ordering is warranted.

# E11 ARB/MUX Virtual LSM Resolution Table Clarifications

In Section 5.1, modifications are applied to Table 47 and the Note below it, as follows:

### Table 47. ARB/MUX Multiple Virtual LSM Resolution Table

| Resolved Request from ARB/MUX<br>to Flex Bus Physical Layer<br>(Row = current vLSM[0] state;<br>Column = current vLSM[1] state) | Reset                   | Active | L1.1   | L1.2                              | L1.3                              | L1.4                              | SLEEP_L2                |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|--------|-----------------------------------|-----------------------------------|-----------------------------------|-------------------------|

| Reset                                                                                                                           | RESET                   | Active | L1.1   | L1.2<br>or<br>lower               | L1.3<br><u>or</u><br><u>lower</u> | L1.4<br><u>or</u><br><u>lower</u> | SLEEP_L2                |

| Active                                                                                                                          | Active                  | Active | Active | Active                            | Active                            | Active                            | Active                  |

| L1.1                                                                                                                            | L1.1                    | Active | L1.1   | L1.1                              | L1.1                              | L1.1                              | L1.1                    |

| L1.2                                                                                                                            | L1.2 <u>or</u><br>lower | Active | L1.1   | L1.2<br><u>or</u><br>lower        | L1.2<br><u>or</u><br>lower        | L1.2<br><u>or</u><br><u>lower</u> | L1.2 <u>or</u><br>lower |

| L1.3                                                                                                                            | L1.3 <u>or</u><br>lower | Active | L1.1   | L1.2<br><u>or</u><br><u>lower</u> | L1.3<br><u>or</u><br><u>lower</u> | L1.3<br><u>or</u><br><u>lower</u> | L1.3 <u>or</u><br>lower |

| L1.4                                                                                                                            | L1.4 <u>or</u><br>lower | Active | L1.1   | L1.2<br><u>or</u><br><u>lower</u> | L1.3<br><u>or</u><br><u>lower</u> | L1.4<br><u>or</u><br><u>lower</u> | L1.4 <u>or</u><br>lower |

| SLEEP_L2                                                                                                                        | SLEEP_L2                | Active | L1.1   | L1.2<br><u>or</u><br><u>lower</u> | L1.3<br><u>or</u><br><u>lower</u> | L1.4<br><u>or</u><br><u>lower</u> | SLEEP_L2                |

Note: Table 47 is presented as a suggestion, not a requirement.

# E12 Text Updates in CXLCM Link Layer Chapter

In sections 4.2.8.1 and 4.2.7, make the following updates:

### 4.2.8.1 LLR Variables

• WrPtr: This indexes the entry of the LLRB that will record the next new flit. When an entity sends a flit, it copies that flit into the LLRB entry indicated by the WrPtr and then increments the WrPtr by one (modulo the size of the LLRB). This is implemented using a wrap-around counter that wraps around to 0 after reaching the depth of the LLRB. Certain LLCTRL flits do not affect the WrPtr. WrPtr stops incrementing after receiving an error indication at the remote entity (RETRY.Req message), until normal operation resumes again (all flits from the LLRB have been retransmitted). WrPtr is initialized to 0 and is incremented only when a flit is put into the LLRB.

Implementation Note: WrPtr may continue to increment after receiving Retry.Req message if there are pre-scheduled All Data Flits that are not yet sent over the link. This implementation will ensure that All Data Flits not interleaved with other flits are correctly logged into the Link Layer Retry Buffer.

NumFreeBuf: This indicates the number of free LLRB entries at the entity. NumFreeBuf is decremented by 1 whenever an LLRB entry is used to store a transmitted flit. NumFreeBuf is incremented by the value encoded in the Ack/ Full\_Ack field of a received flit. NumFreeBuf is initialized at reset time to the size of the LLRB. The maximum number of retry queues at any entity is limited to 255 (8 bit counter). Also, note that the retry buffer at any entity is never filled to its capacity, therefore NumFreeBuf is never '0. If there is only 1 retry buffer entry available, then the sender cannot send an ACK bearing flit which may either be a protocol flit or an empty retry buffer during a retry sequence that may result into incorrect operation. This implies if there are only 2 retry buffer entries left (NumFreeBuf = 2), then the sender can send an Ack bearing flit with Ak bit set), else a LLCRD control flit is sent with Full\_Ack value of at least 1. This is required to avoid deadlock at the link layer due to retry buffer becoming full at both entities on a link and their inability to send ACK through header flits.

### 4.2.7 Link Layer Initialization

• The Tx portion of the Link Layer must wait until the Rx portion of the Link Layer has received at least one valid flit that is CRC clean before sending the LLCTRLINIT.Param flit. Before this condition is met, the Link Layer must transmit only LLCTRL-Retry flits, i.e., Retry.Frame/Reg/Ack/Idle flits.

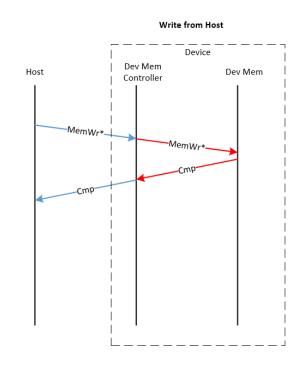

# E13 Fixed Typos in Figure depicting Write from Host

*Update Figure 39, Red arrows from Device Memory Controller to Device Memory should be MemWr\* and Cmp*

### Figure 39. Write from Host

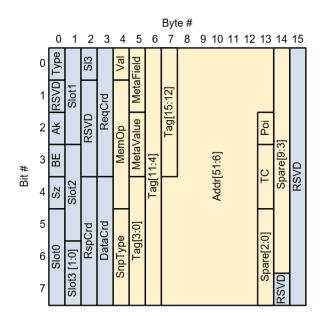

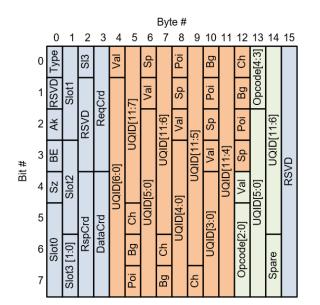

# E14 S2M/D2H G5 Format Update

Updates to S2M/D2H G5 format from 3 NDR to 2 NDR messages. The global flit rules in section 4.2.5 restrict total S2M NDR to 2 total per flit which take precedence, so it is impossible to make use of 3rd NDR message in the S2M/D2H G5 format. Changing the G5 format to only include 2 NDR is done to ensure consistency and avoid confusion.

*First change is to Table 40. Second change is to change G5 format in Figure 70 to include only the first 2 NDR messages converting the 3rd to RSVD bits.*

### Table 40. D2H/S2M Slot Formats

| Format to Req Type Mapping | D2H/S2M                                                   |      |

|----------------------------|-----------------------------------------------------------|------|

|                            | Туре                                                      | Size |

| но                         | CXL.cache Data Header + 2 CXL.cache Resp +<br>CXL.mem NDR | 85   |

| H1                         | CXL.cache Req + CXL.cache Data Header                     | 96   |

| H2                         | 4 CXL.cache Data Header + CXL.cache Resp                  | 88   |

| НЗ                         | CXL.mem DRS Header + CXL.mem NDR                          | 68   |

| H4                         | 2 CXL.mem NDR                                             | 56   |

| Н5 | 2 CXL.mem DRS Header                                      | 80                      |

|----|-----------------------------------------------------------|-------------------------|

| G0 | CXL.cache/ CXL.mem Data Chunk                             | 128                     |

| G1 | CXL.cache Req + 2 CXL.cache Resp                          | 119                     |

| G2 | CXL.cache Req + CXL.cache Data Header +<br>CXL.cache Resp | 116                     |

| G3 | 4 CXL.cache Data Header                                   | 68                      |

| G4 | CXL.mem DRS Header + 2 CXL.mem NDR                        | 96                      |

| G5 | -2 CXL.mem NDR                                            | <del>84<u>-</u>56</del> |

| G6 | 3 CXL.mem DRS Header                                      | 120                     |

### Figure 70. G5 - <del>3</del> <u>2</u> S2M NDR

|                       |   | 0                    | 1             | 2                     | 3          | 4         | 5         | В<br>6     | yte<br>7 | #<br>8 | 9    | 10   | 11 | 12           | 13 | 14   | 15   |

|-----------------------|---|----------------------|---------------|-----------------------|------------|-----------|-----------|------------|----------|--------|------|------|----|--------------|----|------|------|

|                       | 0 | Val                  |               |                       |            | Field     |           | Tag[15:12] |          |        |      |      |    |              |    |      |      |

|                       | 1 | 7:0]                 |               |                       | [3:0]      | MetaField |           |            |          |        |      |      |    |              |    |      |      |

|                       | 2 |                      |               |                       | Spare[3:0] | MetaValue | -         |            |          |        |      |      |    |              |    |      |      |

| #                     | 3 |                      | 5:8]          |                       | Meta/      | 1:4]      |           | RSVD       | RSVD     | ٧D     | ۷D   | RSVD | ٩  | RSVD         | ۷D | ٧D   |      |

| Bit #                 | 4 | -ield                | ield Tag[7:0] | Tag[7:0]<br>Tag[15:8] | Val        | Tad1      | Tag[11:4] | Tag[1      | RS       | RS     | RSVD | RSVD | RS | RSVD<br>RSVD | RS | RSVD | RSVD |

|                       | 5 | alue MetaField<br>Ta |               |                       | 3:0]       |           | [3:0]     |            |          |        |      |      |    |              |    |      |      |

|                       | 6 |                      |               | emOp                  | MemOp      | Tag[3:0]  |           | Spare[3:0] |          |        |      |      |    |              |    |      |      |

|                       | 7 | MetaValue            |               |                       | N          |           |           |            |          |        |      |      |    |              |    |      |      |

| E15 PM timeout value. |   |                      |               |                       |            |           |           |            |          |        |      |      |    |              |    |      |      |

CXL1.1 had a "TBD" value in the PM handling in section 9.4.2. We are updating this value to be 1ms with pause in timer for recovery states.

### 9.4.2 Compute Express Link PM Entry Phase 2

. . .

6. The Downstream Component ARB&MUX port must wait for <TBD> amount of time at least 1mS (not including time spent in recovery states) for a response from the Upstream Component. If no response is received from the Upstream component then the Downstream Component is permitted to abort the PM entry or retry entry into PM again.

# E16 Figure 65 Title

*Figure 65, which is the format for byte enable slot, incorrectly includes "S2M" in the title. CXL.mem S2M messages cannot carry byte enables as defined in table 36. Update to the title removes S2M. Note that M2S message can carry Byte Enables and is captured in Figure 52.*

Figure 65. G0 - D2H<del>/S2M</del> Byte Enable

# E17 Implied EDS and Variable Length NULL Flits

In section 6.2.2, make the below changes. Additionally, at the end of section 6.7.1, add text and Figures 94a and 94b that show examples of NULL with EDS usage. Note, the figure numbering will be updated when this errata is integrated into the specification.

### 6.2.2 Protocol ID[15:0]

The 16-bit protocol ID field specifies whether the transmitted flit is CXL.io, CXL.cache/CXL.mem, or some other payload. The table below provides a list of valid 16-bit protocol ID encodings. Encodings that include an implied EDS token signify that the next block <u>after the block in which the current flit</u> <u>ends</u> is an ordered set block. Implied EDS tokens can only occur with the last flit transmitted in a data block; flits that cross the data block boundary cannot be associated with an implied EDS token.

NULL flits are inserted into the data stream by the physical layer when there are no valid flits available from the link layer. A NULL flit transferred with an implied EDS token ends precisely at the data block boundary preceding the Ordered Set block; these are variable length flits, up to 528 bits, intended to facilitate transition to ordered set blocks as quickly as possible. When 128/130b encoding is used, the variable length NULL flit ends on the first block boundary encountered after the 16-bit protocol ID has been transmitted, and the Ordered Set is transmitted in the next block. Because Ordered Set blocks are inserted at fixed block intervals that align to the flit boundary when sync headers are disabled (as described in section 6.7.1), variable length NULL flits will always contain a fixed 528 bit payload when sync headers are disabled. Please see section 6.7.1 for examples of NULL flit with implied EDS usage scenarios. A NULL flit is comprised of all zeros payload.

### Table 51. Flex Bus.CXL Protocol IDs

| Protocol ID[15:0]   | Description                                                                                                                                                                                     |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000_0000_0000_0000 | Reserved                                                                                                                                                                                        |

| 1111_1111_1111_1111 | CXL.io                                                                                                                                                                                          |

| 1101_0010_1101_0010 | CXL.io with implied EDS token                                                                                                                                                                   |

| 0101_0101_0101_0101 | CXL.cache/CXL.mem                                                                                                                                                                               |

| 1000_0111_1000_0111 | CXL.cache/CXL.mem with implied EDS token                                                                                                                                                        |

| 1001_1001_1001_1001 | NULL flit (generated by Physical Layer)                                                                                                                                                         |

| 0100_1011_0100_1011 | NULL flit with implied EDS token: Variable length flit containing NULLs that ends precisely at the data block boundary <u>preceding the Ordered Set block</u> (generated by the Physical Layer) |

. . .

| 1100_1100_1100_1100 | CXL ARB/MUX Link Management Packets (ALMPs)                        |

|---------------------|--------------------------------------------------------------------|

| 0001_1110_0001_1110 | CXL ARB/MUX Link Management Packets (ALMPs) with implied EDS token |

| All Others          | Reserved                                                           |

### 6.7.1 Control SKP Ordered Set Frequency and L1/Recovery Entry

Figure 94a illustrates a scenario where a NULL flit with implied EDS token is sent as the last flit before exiting the data stream in the case where sync hdr bypass is enabled. In this example, near the end of the 339th block, the link layer has no flits to send, so the physical layer inserts a NULL flit. Since there is exactly one flit's worth of time before the next Ordered Set must be sent, a NULL flit with implied EDS token is used. In this case, the variable length NULL flit with EDS token crosses a block boundary and contains a 528 bit payload of zeros.

Figure 94b illustrates a scenario where a NULL flit with implied EDS token is sent as the last flit before exiting the data stream in the case where 128/130b encoding is used. In this example, the NULL flit contains only a 16 bit payload of zeros.

. . .

|           | Lane 0    | Lane 1    | Lane 2 | Lane 3 | _         |

|-----------|-----------|-----------|--------|--------|-----------|

|           | ProtID=NU | ILL w/EDS | D      | D      | Symbol 15 |

|           |           |           |        |        |           |

|           | D         | D         | D      | D      | Symbol 0  |

|           | D         | D         | D      | D      | Symbol 1  |

|           | D         | D         | D      | D      | Symbol 2  |

|           | D         | D         | D      | D      | Symbol 3  |

|           | D         | D         | D      | D      | Symbol 4  |

|           | D         | D         | D      | D      | Symbol 5  |

|           | D         | D         | D      | D      | Symbol 6  |

|           | D         | D         | D      | D      | Symbol 7  |

| $\square$ | D         | D         | D      | D      | Symbol 8  |

|           | D         | D         | D      | D      | Symbol 9  |

|           | D         | D         | D      | D      | Symbol 10 |

|           | D         | D         | D      | D      | Symbol 11 |

|           | D         | D         | D      | D      | Symbol 12 |

|           | D         | D         | D      | D      | Symbol 13 |

|           | D         | D         | D      | D      | Symbol 14 |

|           | D         | D         | CI     | RC     | Symbol 15 |

|           |           |           |        |        |           |

| ĺ         | OS        | OS        | OS     | OS     | Symbol 0  |

|           | OS        | OS        | OS     | OS     | Symbol 1  |

|           | OS        | OS        | OS     | OS     | Symbol 2  |

|           | OS        | OS        | OS     | OS     | Symbol 3  |

|           | OS        | OS        | OS     | OS     | Symbol 4  |

|           | OS        | OS        | OS     | OS     | Symbol 5  |

|           | OS        | OS        | OS     | OS     | Symbol 6  |

|           | OS        | OS        | OS     | OS     | Symbol 7  |

|           | OS        | OS        | OS     | OS     | Symbol 8  |

|           | OS        | OS        | OS     | OS     | Symbol 9  |

|           | OS        | OS        | OS     | OS     | Symbol 10 |

|           | OS        | OS        | OS     | OS     | Symbol 11 |

|           | OS        | OS        | OS     | OS     | Symbol 12 |

|           | OS        | OS        | OS     | OS     | Symbol 13 |

|           | OS        | OS        | OS     | OS     | Symbol 14 |

|           | <br>OS    | OS        | OS     | OS     | Symbol 15 |

### Figure 94a. NULL Flit w/EDS and Sync Hdr Bypass Optimization

340th Data Block

Ordered Set Block

| Lane 0    | Lane 1    | Lane 2 | Lane 3 | _           |

|-----------|-----------|--------|--------|-------------|

| ProtID=NU | ILL w/EDS | D      | D      | Symbol 15   |

| 01b       | 01b       | 01b    | 01b    | Sync Header |

| OS        | OS        | OS     | OS     | Symbol 0    |

| OS        | OS        | OS     | OS     | Symbol 1    |

| OS        | OS        | OS     | OS     | Symbol 2    |

| OS        | OS        | OS     | OS     | Symbol 3    |

| OS        | OS        | OS     | OS     | Symbol 4    |

| OS        | OS        | OS     | OS     | Symbol 5    |

| OS        | OS        | OS     | OS     | Symbol 6    |

| OS        | OS        | OS     | OS     | Symbol 7    |

| OS        | OS        | OS     | OS     | Symbol 8    |

| OS        | OS        | OS     | OS     | Symbol 9    |

| OS        | OS        | OS     | OS     | Symbol 10   |

| OS        | OS        | OS     | OS     | Symbol 11   |

| OS        | OS        | OS     | OS     | Symbol 12   |

| OS        | OS        | OS     | OS     | Symbol 13   |

| OS        | OS        | OS     | OS     | Symbol 14   |

| <br>OS    | OS        | OS     | OS     | Symbol 15   |

### Figure 94b. NULL Flit w/EDS with 128/130b Encoding

# E18 CRC bit location

Ordered Set Block

*Errors were found in the CRC data mask in the E18 released prior to errata version 4, so this errata item has been removed and replaced with E26.*

# E19 Text Updates in CXLCM Link Layer Chapter (part 2)

Additional updates to Retry flow text that is inclusive of changes discussed in E12. The additional changes are updates to description of NumFreeBuff=2 case below.

### 4.2.8.1 LLR Variables

• WrPtr: This indexes the entry of the LLRB that will record the next new flit. When an entity sends a flit, it copies that flit into the LLRB entry indicated by the WrPtr and then increments the WrPtr by one (modulo the size of the LLRB). This is implemented using a wrap-around counter that wraps around to 0 after reaching the depth of the LLRB. Certain LLCTRL flits do not affect the WrPtr. WrPtr stops incrementing after receiving an error indication at the remote entity (RETRY.Req message), until normal operation resumes again (all flits from the LLRB have been retransmitted). WrPtr is initialized to 0 and is incremented only when a flit is put into the LLRB. Implementation Note: WrPtr may continue to increment after receiving Retry.Req message if there are pre-scheduled All Data Flits that are not yet sent over the link. This implementation will ensure that All Data Flits not interleaved with other flits are correctly logged into the Link Layer Retry Buffer.

NumFreeBuf: This indicates the number of free LLRB entries at the entity. NumFreeBuf is decremented by 1 whenever an LLRB entry is used to store a transmitted flit. NumFreeBuf is incremented by the value encoded in the Ack/Full\_Ack (Ack is the protocol flit bit AK, Full Ack defined as part of LLCRD message) field of a received flit. NumFreeBuf is initialized at reset time to the size of the LLRB. The maximum number of retry queues at any entity is limited to 255 (8 bit counter). Also, note that the retry buffer at any entity is never filled to its capacity, therefore NumFreeBuf is never '0. If there is only 1 retry buffer entry available, then the sender cannot send an ACK bearing flit\_Retryable flit. This restriction is required to avoid ambiguity between a full or an empty retry buffer during a retry sequence that may result into incorrect operation. This implies if there are only 2 retry buffer entries left (NumFreeBuf = 2), then the sender can send an Ack bearing flit only if the outgoing flit encodes a value of at least 1 (which may be a Protocol flit AK bit set), else a LLCRD control flit is sent with Full Ack value of at least 1. This is required to avoid deadlock at the link layer due to retry buffer becoming full at both entities on a link and their inability to send ACK through header flits. This rule also creates an implicit expectation that you cannot start a sequence of "All Data Flits" that cannot be completed before NumFreeBuf=2 because you must be able to inject the Ack bearing flit when NumFreeBuf=2 is reached.

### 4.2.7 Link Layer Initialization

• The Tx portion of the Link Layer must wait until the Rx portion of the Link Layer has received at least one valid flit that is CRC clean before sending the LLCTRLINIT.Param flit. Before this condition is met, the Link Layer must transmit only LLCTRL-Retry flits, i.e., Retry.Frame/Req/Ack/Idle flits.

# E20 Appendix A.2 fix for Bias Flip

The Appendix section A.2 was inconsistent with the rest of the spec that mandates Bias Flip to use RdOwnNoData not CLFLUSH.

• Cache flush executed using CLFLUSH RdOwnNoData on CXL CXL.cache protocol.

# E21 Description of RSP\_PRE

Fix wording on RSP\_PRE which has stale wording In Table 11.

### Table 11. CXL.cache - H2D Response Fields

| H2D<br>Response | Width | Description                                                                                                                                                                                                           |

|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Valid           | 1     | The Valid field indicates that this is a valid response to the device.                                                                                                                                                |

| Opcode          | 4     | The Opcode field indicates the type of the response being sent. Details in Table 20                                                                                                                                   |

| RspData         | 12    | The response Opcode determines how the RspData field is interpreted<br>as shown in Table 20. Thus, depending on Opcode, it can either contain<br>the UQID or the MESI information in bits [3:0] as shown in Table 13. |

| RSP_PRE | 2  | RSP_PRE carries performance monitoring information-for requests that do not receive data. Details in Table 12                                |

|---------|----|----------------------------------------------------------------------------------------------------------------------------------------------|

| CQID    | 12 | Command Queue ID: This is a reflection of the CQID sent with the D2H Request and indicates which device entry is the target of the response. |

| RSVD    | 1  |                                                                                                                                              |

| Total   | 32 |                                                                                                                                              |

# E22 CXL Downstream Port Supported PCIe Capabilities (part 2)

Additional updates to Table 60 that is inclusive of changes discussed in E3.

### Table 60. CXL Downstream Port Supported PCIe Capabilities and Extended Capabilities

| Supported PCIe Capabilities<br>and Extended Capabilities | Exceptions <sup>1</sup>                                                                                                                    | Notes                                                                                                                                        |  |  |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PCI Express Capability                                   | Slot Capabilities, Slot Control, Slot<br>Status, Slot Capabilites 2, Slot<br>Control 2, and Slot Status 2<br>registers are not applicable. | None                                                                                                                                         |  |  |  |  |

| PCI Power Management Capability                          | None Not Applicable. Software should ignore.                                                                                               | None                                                                                                                                         |  |  |  |  |

| MSI Capability                                           | None Not Applicable. Software should ignore.                                                                                               | None                                                                                                                                         |  |  |  |  |

| Advanced Error Reporting<br>Extended Capability          | None <u>Not Applicable. Software</u><br>should ignore.                                                                                     | Required for CXL <u>devices</u> despite<br>being optional for PCIe.<br><u>Downstream Port is required to</u><br><u>forward ERR messages.</u> |  |  |  |  |

| ACS Extended Capability                                   | None                                                                                                                         | None                                                                             |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Multicast Extended Capability                             | None Not Applicable. Software should ignore.                                                                                 | None                                                                             |

| Downstream Port Containment<br>Extended Capability        | None_Use with care. DPC trigger<br>will bring down physical link, reset<br>device state, disrupt .cache and<br>.mem traffic. | None                                                                             |

| Designated Vendor-Specific<br>Extended Capability (DVSEC) | None                                                                                                                         | Please refer to section Figure<br>7.2.1.3 for Flex Bus Port DVSEC<br>definition. |

| Secondary PCI Express<br>Extended Capability              | None                                                                                                                         | None                                                                             |

| Data Link Feature Extended<br>Capability                  | None                                                                                                                         | None                                                                             |

| Physical Layer 16.0 GT/s<br>Extended Capability           | None                                                                                                                         | None                                                                             |

| Physical Layer 32.0 GT/s<br>Extended Capability           | None                                                                                                                         | None                                                                             |

| Lane Margining at the Receiver<br>Extended Capability     | None                                                                                                                         | None                                                                             |

| Alternate Protocol Extended<br>Capability                 | None                                                                                                                         | None                                                                             |

# E23 CXL Upstream Port Supported PCIe Capabilities (part 2)

Additional updates to Table 61 that is inclusive of changes discussed in E4.

### Table 61. CXL Upstream Port Supported PCIe Capabilities and Extended Capabilities

| Support PCIe Capabilities and<br>Extended Capabilities | Exceptions <sup>1</sup>                      | Notes                                                                                                                                                                           |

|--------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express Capability                                 | None                                         | N/ANone                                                                                                                                                                         |

| Advanced Error Reporting<br>Extended Capability        | None Not Applicable. Software should ignore. | Required for CXL <u>devices</u> despite<br>being optional for PCIe.<br><u>Link/Protocol errors detected by</u><br><u>Upstream Port are logged/reported</u><br><u>via RCiEP.</u> |

| Multicast Extended Capability                             | None | N/A                                                                              |  |  |  |  |

|-----------------------------------------------------------|------|----------------------------------------------------------------------------------|--|--|--|--|

| Virtual Channel Extended<br>Capability                    | None | VC0 and VC1                                                                      |  |  |  |  |

| Designated Vendor-Specific<br>Extended Capability (DVSEC) | None | Please refer to section Figure<br>7.2.1.3 for Flex Bus Port DVSEC<br>definition. |  |  |  |  |

| Secondary PCI Express Extended<br>Capability              | None | None                                                                             |  |  |  |  |

| Data Link Feature Extended<br>Capability                  | None | None                                                                             |  |  |  |  |

| Physical Layer 16.0 GT/s Extended<br>Capability           | None | None                                                                             |  |  |  |  |

| Physical Layer 32.0 GT/s Extended<br>Capability           | None | None                                                                             |  |  |  |  |

| Lane Margining at the Receiver<br>Extended Capability     | None | None                                                                             |  |  |  |  |

| Alternate Protocol Extended<br>Capability                 | None | None                                                                             |  |  |  |  |

# E24 Clarify Logging of Errors Detected by Upstream Port

Section 11.2.2.2 CXL Device Error Handling Flow incorrectly implied that Upstream Port is required to implement AER capability structure and log link errors there.

Errors that are not related to any specific Function within the device (Non-Function errors) are reported to the Host via PCIe error messages where they can be escalated to the platform. Non-Function errors are logged in the Upstream Port RCRB in the PCIe AER Registers. In addition, t The UP reports non-function errors to all RCiEPs where they are logged. Each RCiEP reports the non-function specific errors to the host via error messages. Software should be aware that even though an RCiEP does not have a software-visible link, it may still log link-related errors. At most one error message of a given severity is generated for a multifunction device. The error message must include the Requester ID of a function that is enabled to send the error message. Error messages with the same Requester ID may be merged for different errors with the same severity. No error message is sent if no function is enabled to do so. If different functions are enabled to send error messages of different severity, at most one error of each severity level is sent. If a Root Complex Error Collector is implemented, errors may optionally be sent to the corresponding RCEC. This error will be sent to the corresponding RCEC. Each RCiEP must be associated with no more than one RCEC.

# E25 Clarification to Force LLCRD definition

Section 4.2.8.2 ACK Forcing requires expanding to also cover Crd value forcing to avoid starvation risk. Also including general clarification on how LLCRD forcing should be implemented.

Section 7.2.2.1.21 defines the control register used in section 4.2.8.2. Updating the register description to describe CRD requirements and including recommended default and minimum values.

*In Section 1.2, adding "Link Layer Clock" definition to Table 1 in the Introduction because it is used by this section but not defined.*

### 4.2.8.2 ACKLLCRD Forcing

Recall that the LLR protocol requires space available in the LLRB to transmit a new flit, and that the sender must receive explicit acknowledgment from the receiver before freeing space in the LLRB. In scenarios where the traffic flow is very asymmetric, this requirement could result in traffic throttling and possibly even starvation.

Suppose that the  $A \rightarrow B$  direction has very heavy traffic, but there is no traffic at all in the  $B \rightarrow A$  direction. In this case A could exhaust its LLRB size, while B never has any return traffic in which to embed Acks. In CXL we want to minimize injected traffic to reserve bandwidth for the other traffic stream(s) sharing the link.