Compute Express Link<sup>TM</sup> (CXL<sup>TM</sup>) Errata for the Compute Express Link Specification Revision 2.0 May 2021 >

Compute

Express ∖ Link™

#### LEGAL NOTICE FOR THIS PUBLICLY-AVAILABLE SPECIFICATION FROM COMPUTE EXPRESS LINK CONSORTIUM, INC.

### © 2019-2021 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED.

This CXL **Specification** (this "<u>CXL Specification</u>" or this "**document**") is owned by and is proprietary to Compute Express Link Consortium, Inc., a Delaware nonprofit corporation (sometimes referred to as "<u>CXL</u>" or the "<u>CXL Consortium</u>" or the "**Company**") and/or its successors and assigns.

### NOTICE TO USERS WHO ARE MEMBERS OF THE CXL CONSORTIUM:

If you are a Member of the CXL Consortium (sometimes referred to as a "<u>CXL Member</u>"), and even if you have received this publicly-available version of this CXL Specification after agreeing to CXL Consortium's Evaluation Copy Agreement (a copy of which is available <u>https://www.computeexpresslink.org/download-the-specification</u>, each such CXL Member must also be in compliance with all of the following CXL Consortium documents, policies and/or procedures (collectively, the "<u>CXL Governing Documents</u>") in order for such CXL Member's use and/or implementation of this CXL Specification to receive and enjoy all of the rights, benefits, privileges and protections of CXL Consortium membership: (i) CXL Consortium's Intellectual Property Policy; (ii) CXL Consortium's Bylaws; (iii) any and all other CXL Consortium policies and procedures; and (iv) the CXL Member's Participation Agreement.

### NOTICE TO NON-MEMBERS OF THE CXL CONSORTIUM:

If you are **not** a CXL Member and have received this publicly-available version of this CXL Specification, your use of this document is subject to your compliance with, and is limited by, all of the terms and conditions of the CXL Consortium's Evaluation Copy Agreement (a copy of which is available at <a href="https://www.computeexpresslink.org/download-the-specification">https://www.computeexpresslink.org/download-the-specification</a>).

In addition to the restrictions set forth in the CXL Consortium's Evaluation Copy Agreement, any references or citations to this document must acknowledge the Compute Express Link Consortium, Inc.'s sole and exclusive copyright ownership of this CXL Specification. The proper copyright citation or reference is as follows: "© 2019-2021 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED." When making any such citation or reference to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of the Compute Express Link Consortium, Inc.

Except for the limited rights explicitly given to a non-CXL Member pursuant to the explicit provisions of the CXL Consortium's Evaluation Copy Agreement which governs the publicly-available version of this CXL Specification, nothing contained in this CXL Specification shall be deemed as granting (either expressly or impliedly) to any party that is <u>not</u> a CXL Member: (ii) any kind of license to implement or use this CXL Specification or any portion or content described or contained therein, or any kind of license in or to any other intellectual property owned or controlled by the CXL Consortium, including without limitation any trademarks of the CXL Consortium.; or (ii) any benefits and/or rights as a CXL Member under any CXL Governing Documents.

### LEGAL DISCLAIMERS FOR ALL PARTIES:

THIS DOCUMENT AND ALL SPECIFICATIONS AND/OR OTHER CONTENT PROVIDED HEREIN IS PROVIDED ON AN "AS IS" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, COMPUTE EXPRESS LINK CONSORTIUM, INC. (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NON-INFRINGEMENT. In the august this CYL Specification makes any references (including without limitation any incomparation by reference) to constant and dedited without limitation any incomparation by reference) to constant and dedited without limitation any incomparation by reference).

In the event this CXL Specification makes any references (including without limitation any incorporation by reference) to another standard's setting organization's or any other party's ("<u>Third Party</u>") content or work, including without limitation any specifications or standards of any such Third Party ("<u>Third Party Specification</u>"), you are hereby notified that your use or implementation of any Third Party Specification: (i) is not governed by any of the CXL Governing Documents; (ii) may require your use of a Third Party's patents, copyrights or other intellectual property rights, which in turn may require you to independently obtain a license or other consent from that Third Party in order to have full rights to implement or use that Third Party Specification; and/or (iii) may be governed by the intellectual property policy or other policies or procedures of the Third Party which owns the Third Party Specification. Any trademarks or service marks of any Third Party which may be referenced in this CXL Specification is owned by the respective owner of such marks.

### NOTICE TO ALL PARTIES REGARDING THE PCI-SIG UNIQUE VALUE PROVIDED IN THIS CXL SPECIFICATION:

NOTICE TO USERS: THE UNIQUE VALUE THAT IS PROVIDED IN THIS CXL SPECIFICATION IS FOR USE IN VENDOR DEFINED MESSAGE FIELDS, DESIGNATED VENDOR SPECIFIC EXTENDED CAPABILITIES, AND ALTERNATE PROTOCOL NEGOTIATION ONLY AND MAY NOT BE USED IN ANY OTHER MANNER, AND A USER OF THE UNIQUE VALUE MAY NOT USE THE UNIQUE VALUE IN A MANNER THAT (A) ALTERS, MODIFIES, HARMS OR DAMAGES THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF, OR (B) COULD OR WOULD REASONABLY BE DETERMINED TO ALTER, MODIFY, HARM OR DAMAGE THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF (FOR PURPOSES OF THIS NOTICE, "<u>PCI-SIG ECOSYSTEM</u>" MEANS THE PCI-SIG SPECIFICATIONS, MEMBERS OF PCI-SIG AND THEIR ASSOCIATED PRODUCTS AND SERVICES THAT INCORPORATE ALL OR A PORTION OF A PCI-SIG SPECIFICATION AND EXTENDS TO THOSE PRODUCTS AND SERVICES INTERFACING WITH PCI-SIG MEMBER PRODUCTS AND SERVICES).

## Contents

| F1  | ARB/MUX State Transition Table 6                             |

|-----|--------------------------------------------------------------|

| F2  | PCIe Capable/Enable Description in Table 687                 |

| F3  | Making Hot-plug support optional for Downstream Ports        |

| F4  | Chapter 8 Miscellaneous errata 8                             |

| F5  | Chapter 9 Miscellaneous errata28                             |

| F6  | Secure MEM tests                                             |

| F7  | Compliance DVSEC length incorrect                            |

| F8  | Flag Bit in Algorithm 2 not documented34                     |

| F9  | Completion Timeout Injection missing pass criteria           |

| F10 | Removal of text in 14.11.535                                 |

| F11 | Compliance DOE referencing incorrect table                   |

| F12 | Compliance Algorithm Security                                |

| F13 | Update to 14.8.5 to remove secondary verify statement        |

| F14 | Removal of Reference to CXL_ERROR_DOE_MAILBOX                |

| F15 | Incorrect CXL Capability Version                             |

| F16 | Updates to Memory Mapped Register Test40                     |

| F17 | Update to DVSEC CXL Lock test pass criteria40                |

| F18 | Incorrect Pass criteria in 14.15.1 Sticky Register Tests     |

| F19 | Compliance Capability Return Value41                         |

| F20 | LinkError clarification41                                    |

| F21 | PM Retry and Abort clarifications42                          |

| F22 | PM Entry Phase 3 clarification44                             |

| F23 | Modifications to the CRC Error Injection within compliance44 |

| F24 | Querying Critical Component Information and Status45         |

| F25 | Support for Components with Limited Buffering Capability50   |

| F26 | Incorrect Table Links                                        |

| F27 | FM API Event Notifications56                                 |

| F28 | CEDT CFMWS & QTG DSM ECN Errata62                            |

| F29 | Appendix B, Type-2 Memory Request Table62                    |

| F30 | Incorrect passing criteria in CXL Capability Header test63   |

| F31 | Update Reference to CDAT Specification63                     |

| F32 | Eliminate the term "Host Space"64                            |

| F33 | Chapter 11, Figure 177 and Figure 17966                      |

Errata for the Compute Express Link Specification Rev 2.0

Copy C ati E S U

# Revision History

| Revision    | Description                  | Date        |

|-------------|------------------------------|-------------|

| 1.0         | First Release: Errata F1-F33 | May 5, 2021 |

| 0           |                              |             |

| CO          |                              |             |

| nati        |                              |             |

| T<br>Z<br>J |                              |             |

|             |                              |             |

\_\_\_\_\_

# F1 ARB/MUX State Transition Table

*In section 5.1, Table 60, make the following changes to delete the Active->Reset transition and add the Retrain to Reset transition:*

## Table 60. ARB/MUX State Transition Table

| Current vLSM State | Next State | Upstream Port Trigger<br>Condition                                                                                                                                            | Downstream Port<br>Trigger Condition                                                                                                                                                            |

|--------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active             | L1.x       | Upon receiving a Request<br>to enter L1.x from Link<br>Layer, the ARB/MUX<br>must initiate a Request<br>ALMP{L1.x} and receive<br>a Status ALMP{L1.x}<br>from the remote vLSM | Upon receiving a Request<br>to enter L1.x from Link<br>Layer and receiving a<br>Request ALMP{L1.x}<br>from the Remote vLSM,<br>the ARB/MUX must send<br>Status ALMP{L1.x} to the<br>remote vLSM |

|                    | L2         | Upon receiving a Request<br>to enter L2 from Link<br>Layer the ARB/MUX must<br>initiate a Request<br>ALMP{L2} and receive a<br>Status ALMP{L2} from<br>the remote vLSM        | Upon receiving a Request<br>to enter L2 from Link<br>Layer and receiving a<br>Request ALMP{L2} from<br>the Remote vLSM the<br>ARB/MUX must send<br>Status ALMP{L2} to the<br>remote vLSM        |

|                    | Reset      | Physical Layer transitions<br>from Recovery to L0 and<br>State Status ALMP<br>synchronization for<br>Recovery exit resolves to<br>Reset. (see Section<br>5.1.2.3)             | N/A                                                                                                                                                                                             |

| L1                 | Retrain    | Upon receiving an ALMP<br>Active request from<br>remote ARB/MUX                                                                                                               | Upon receiving an ALMP<br>Active request from<br>remote ARB/MUX                                                                                                                                 |

| Active             | Retrain    | Any of the following<br>conditions are met:<br>1) Physical Layer LTSSM<br>enters Recovery.                                                                                    | Physical Layer LTSSM<br>enters Recovery.                                                                                                                                                        |

|         |              | 2) Physical Layer<br>transitions from Recovery<br>to L0 and State Status<br>ALMP synchronization for<br>Recovery exit resolves to<br>Retrain. (see Section<br>5.1.2.3)                                                                   |                                                                                                                                                                                                                                          |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Retrain | Active       | Link Layer is requesting<br>Active and any of the<br>following conditions are<br>met:                                                                                                                                                    | Link Layer is requesting<br>Active and any of the<br>following conditions are<br>met:                                                                                                                                                    |

| Ö       |              | 1) Physical Layer<br>transitions from Recovery<br>to L0 and State Status<br>ALMP synchronization for<br>Recovery exit resolves to<br>Active.                                                                                             | 1) Physical Layer<br>transitions from Recovery<br>to L0 and State Status<br>ALMP synchronization for<br>Recovery exit resolves to<br>Active.                                                                                             |

|         |              | 2) Physical Layer<br>transitions from Recovery<br>to L0 and State Status<br>ALMP synchronization for<br>Recovery exit does not<br>resolve to Active. Entry<br>to Active ALMP exchange<br>protocol is complete.<br>(See Section 5.1.2.2.) | 2) Physical Layer<br>transitions from Recovery<br>to L0 and State Status<br>ALMP synchronization for<br>Recovery exit does not<br>resolve to Active. Entry<br>to Active ALMP exchange<br>protocol is complete.<br>(See Section 5.1.2.2.) |

| ţi      |              | 3) Physical Layer has<br>been in L0. Entry to<br>Active ALMP exchange<br>protocol is complete.<br>(See Section 5.1.2.2.)                                                                                                                 | 3) Physical Layer has<br>been in L0. Entry to<br>Active ALMP exchange<br>protocol is complete.<br>(See Section 5.1.2.2)                                                                                                                  |

| Retrain | <u>Reset</u> | Physical Layer transitions<br>to L0 and State Status<br>ALMP synchronization for<br>Recovery exit resolves to<br>Reset. (see Section<br>5.1.2.3)                                                                                         | <u>N/A</u>                                                                                                                                                                                                                               |

# PCIe Capable/Enable Description in Table 68

In section 6.3.1.1, Table 68, make the following changes:

$\mathbf{O}$

F2

### Table 68. Additional Information on Symbols 12-14 of Modified TS1/TS2 Ordered Sets

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | Bit Field in S                                  | Symbols 12-14                                           | Description                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | )<br>Ie capable                         | e/enable                                        |                                                         | The Downstream Port and Upstream Port advertise<br>their capability in Phase 1-as set in the Flex Bus Port<br>Control register in Section 8.2.1.3.2. The Downstream<br>Port communicates the results of the negotiation in<br>Phase 2. <sup>1</sup> |

| F3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ма                                      | king Ho                                         | t-plug support o                                        | ptional for Downstream Ports                                                                                                                                                                                                                        |

| In s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ection 9.                               | 9, make the                                     | following changes:                                      |                                                                                                                                                                                                                                                     |

| Ren<br>Ren                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <del>10ve.<u> CXI</u><br/>-Remove</del> | <u>2.0 Root Po</u><br>All CXL 2.0<br>2.0 Device | orts and CXL Downstream S<br>Ports shall be designed to | tes shall support Hot-Add and managed Hot-<br>Switch Ports may support Hot-Add and managed<br>avoid electrical damage upon surprise Hot-<br>bable of being Hot-plugged, subject to the Form                                                         |

| <b>C</b> F4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ch                                      | apter 8                                         | Miscellaneous er                                        | rata                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ection 8.<br>ignment:                   | 1.2, make tł                                    | ne following addition to the                            | footnote below Table 125. CXL DOE Type                                                                                                                                                                                                              |

| Typ<br>(See                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | e is not in<br>ction 14.                | mplemented<br>16.1). <u>PCIe l</u>              | by a device, it shall impler                            | ommended for CXL 2.0 devices. If Compliance DOE<br>nent PCIe DVSEC for Test Capability<br>s not required for CXL 2.0 devices running in CXL                                                                                                         |

| <b>The second seco</b> | ection 8.                               | 1.3.3, make                                     | the following change:                                   |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit                                     | Attributes                                      | Description                                             |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13:0                                    | Revds.                                          | Reserved.                                               |                                                                                                                                                                                                                                                     |

| ш                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14                                      | RW1CS                                           |                                                         | ndicates that the CXL device <del>has</del> had<br>cion <mark>entered Viral</mark> . <del>Viral.</del> This bit does not                                                                                                                            |

|              |              |               | indicate that the device is currently in Viral condition. See Section 12.4, "CXL Viral Handling" for more details.                                                                                                                                                   |

|--------------|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 15           | RsvdZ         | Reserved.                                                                                                                                                                                                                                                            |

| $\mathbf{O}$ | )            |               |                                                                                                                                                                                                                                                                      |

| 0            | In section 8 | 3.1.4.1, make | e the following change:                                                                                                                                                                                                                                              |

| $\bigcirc$   | Bit          | Attributes    | Description                                                                                                                                                                                                                                                          |

|              |              |               | Non CXL Function: Each bit represents a non-virtual function number implemented by the device on the same bus as the function that carries PCIe DVSEC for CXL Device.                                                                                                |

|              | 21.0         | HwInit        | When a bit is set, the corresponding Device/Function number or Function<br>number (ARI device) is not capable of participating in CXL.Cache or<br>CXL.Mem protocol. Bits corresponding to Non-existent Device/Function or<br>Function numbers shall always return 0. |

|              | 31:0         |               | If the device does not support ARI, bit $x$ in this register maps to Device $x$ , Function 0.                                                                                                                                                                        |

|              |              |               | If the device supports ARI, bit $x$ in this register maps to Function $x$ .                                                                                                                                                                                          |

| <u>H</u>     |              |               | Bit 0 of this register shall always be set to $0.1$ since PCIe DVSEC for CXL Device declares whether Device 0, Function 0 participates in CXL.Cache and CXL.Mem protocol.                                                                                            |

|              |              |               |                                                                                                                                                                                                                                                                      |

|              | In section a | 3.1.9, remove | e blue formatting from this sentence:                                                                                                                                                                                                                                |

|              |              |               | ontains one or more Register Block entries. Figure 131 illustrates a DVSEC er Block Entries.                                                                                                                                                                         |

|              | 1            |               |                                                                                                                                                                                                                                                                      |

|              | In section & | 8.1.9.1, make | e the following changes:                                                                                                                                                                                                                                             |

|              | Bit          | Attributes    | Description                                                                                                                                                                                                                                                          |

|              |              |               |                                                                                                                                                                                                                                                                      |

|              |              |               |                                                                                                                                                                                                                                                                      |

|   | 2:0   | HWInit | <br>The Registers block must be wholly contained within the specified BAR.<br>For a 64-bit Base Address Register, the Register BIR indicates the lower<br>DWORD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7:3   | RsvdP  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 15:8  | HwInit | <ul> <li>Register Block Identifier - Identifies the type of CXL registers.</li> <li>Defined encodings are: <ul> <li>00h Indicates the register block entry is empty and the Register BIR, Register Block Offset Low and Register Block Offset High fields are invalid.</li> <li>01h Component Registers. The format of the Component Register block is defined in Section 8.2.4.</li> <li>02h BAR Virtualization ACL Registers. The format of the BAR Virtualization ACL Register Block Component Register block is defined in Section 8.2.7.</li> <li>03h CXL Memory Device Registers. The format of the CXL Memory Device Register block is defined in Section 8.2.8.</li> </ul> </li> <li>All other Reserved.</li> </ul> |

| 0 | 31:16 | HwInit | Register Block Offset Low - A[31:16] of byte offset from the starting<br>address of the Function's BAR associated with the Register BIR field<br>address contained by one of the Function's Base Address Registers to<br>point to the base of the Register Block. Register Block Offset is 64K<br>aligned. Hence A[15:0] is zero.                                                                                                                                                                                                                                                                                                                                                                                           |

| л |       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

In section 8.1.9.2, make the following changes:

| Ins          | section & | з.1.9. <i>2, таке</i> | the following changes:                                                                                                                                                                                                                                            |

|--------------|-----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{D}$ | Bit       | Attributes            | Description                                                                                                                                                                                                                                                       |

|              | 31:0      | HwInit                | Register Block Offset High - A[63:32] of byte offset from the starting<br>address of the Function's BAR associated with the Register BIR<br>fieldaddress contained by one of the Function's Base Address Registers to<br>point to the base of the Register Block. |

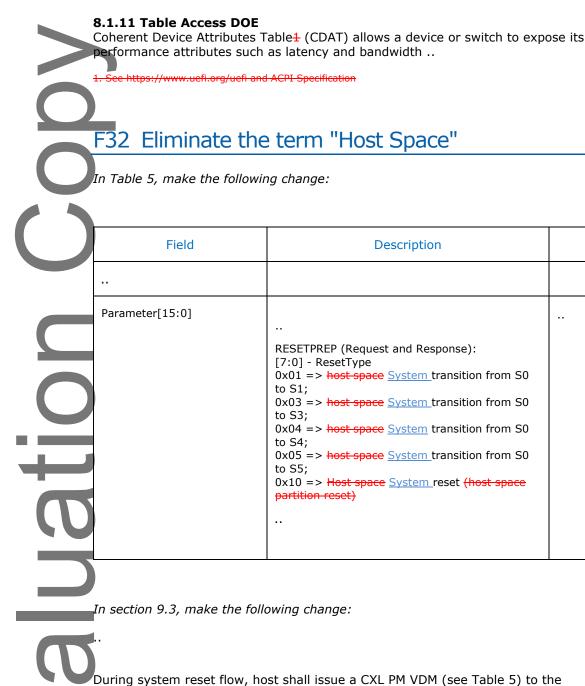

| Ins          | section & | 3.1.11.1, mak         | e the following change:                                                                                                                                                                                                                                           |

|   | Data Object<br>Byte Location | Length | Description                                                                                                                                                                                                                                                                                                         |

|---|------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                              |        |                                                                                                                                                                                                                                                                                                                     |

| 0 | 0Ah                          | 2      | EntryHandle - Handle value associated with the entry being requested. EntryHandle=0 represents the very first entry in the table. For Table Type = 0, EntryHandle = 0 specifies that the request is for the CDAT table header and EntryHandle=1-N indicates the request is for the CDAT Structure[EntryHandle - 1]. |

In section 8.2.5, make the following change:

Table 142 CXL\_Capability\_ID Assignment

|   | Capability                                                | ID | Highest<br>version | Mandatory <sup>1</sup> | Not<br>Permitted | Optional |

|---|-----------------------------------------------------------|----|--------------------|------------------------|------------------|----------|

| Ο |                                                           |    |                    |                        |                  |          |

|   | CXL Extended Security<br>Capability (Section<br>8.2.5.13) | 6  | 1                  | R                      | All others       |          |

| σ |                                                           |    |                    |                        |                  |          |

1 P- PCI Express device, D1 - CXL 1.1 Device, D2 - CXL 2.0 Device, LD - Logical Device, FMLD - Fabric Manager owned LD 0xFFFF, UP1 - CXL 1.1 Upstream Port RCRB, DP1 - CXL 1.1 Downstream Port RCRB, R - CXL 2.0 Root Port (includes CXL Host Bridge registers), USP - CXL Switch Upstream Port, DSP - CXL Switch Downstream Port

May 5, 2021

Е А Ш

|   | Bit Location | Attributes | Description                                                                                                                                                                          |

|---|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 |              |            |                                                                                                                                                                                      |

|   | 19:16        | RO         | CXL_Capability_Version: This defines the version number of the CXL_Capability structure present. For this <u>and</u> the prior version of the specification, this field must be 0x1. |

|   |              |            |                                                                                                                                                                                      |

In section 8.2.5.9.6, make the following change:

<u>Header Log Registers are accessed as series of 32 bit wide individual registers even though it is</u> represented as a single 512 bit long entity for convenience. In accordance with the section 8.2.2, each individual register shall be accessed as an aligned 4 Byte quantity.

|     | Bit Location | Attributes | Description                                                                                                                                                                                                                                                                                                                                            |

|-----|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tio | 511:0        | RO         | Header Log: The information logged here depends on the type<br>of Uncorrectable Error Status bit recorded as described in<br>Section 8.2.5.9.1. If multiple errors are logged in Uncorrectable<br>Error Status register, First_Error_Pointer field in Error<br>Capabilities and Control Register identifies the error that this log<br>corresponds to. |

In section 8.2.5.12, make the following change:

CXL HDM Decoder Capability Structure enables interleaving of HDM across CXL.mem-capable devices.

A CXL Host Bridge is identified as an ACPI device with <u>HardwareHost Interface</u> ID (HID) of "ACPI0016" and is associated with one or more CXL Root ports. Any CXL 2.0 Host Bridge that is associated with more than one CXL Root Port must contain one instance of this capability structure in the CHBCR. This capability structure resolves the target CXL Root Ports for a given memory address.

In sections 8.2.5.12.7 and 8.2.5.12.15, make the following change:

Bit Location Attributes Description

| VOD        | 12 | RWL <u>/ RO</u> | <ul> <li>This bit is RWL for CXL Hosts and Upstream Switch Ports. This bit is RO for a CXL.mem device and it may return the value of 0 or 1.</li> <li>Target Device Type</li> <li>0: Target is a CXL Type 2 Device</li> <li>1: Target is a CXL Type 3 Device</li> <li>The locking behavior is described in Section 8.2.5.12.21.</li> <li>Default value of this field is 0.</li> </ul> |

|------------|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\bigcirc$ |    |                 |                                                                                                                                                                                                                                                                                                                                                                                       |

Update section 8.2.5.14.3 as follows

|   | Bit Location | Attributes | Description                  |  |

|---|--------------|------------|------------------------------|--|

|   | 3:0          | RW1CS      | Rx IDE Status:               |  |

|   |              |            | 0: Reserved                  |  |

|   |              |            | 1: Active Containment Mode   |  |

|   |              |            | 2: Active Skid Mode          |  |

|   |              |            | 4: Fail-Insecure State Error |  |

|   |              |            | All other reserved           |  |

|   | 7:4          |            | Tx IDE Status:               |  |

|   |              |            | 0: Reserved                  |  |

|   |              |            | 1: Active Containment Mode   |  |

|   |              |            | 2: Active Skid Mode          |  |

|   |              |            | 4: Fail-Insecure State Error |  |

|   |              |            | All other reserved           |  |

| V |              |            |                              |  |

|   |              |            |                              |  |

|   | <i>Update section 8.2.5.14.4 as follows</i> |            |                  |  |  |  |  |  |

|---|---------------------------------------------|------------|------------------|--|--|--|--|--|

| ш | Bit Location                                | Attributes | Description      |  |  |  |  |  |

|   | 3:0                                         |            | Rx Error Status: |  |  |  |  |  |

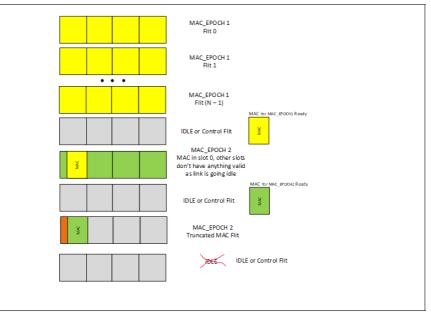

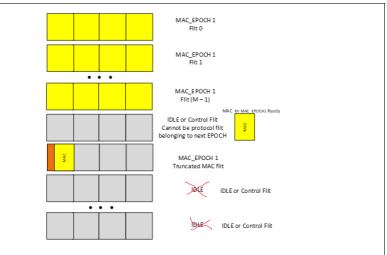

|  | Describes the error condition that transitioned the link to-Fail<br>Insecure Mode-State<br><br>0b0010: MAC Header or Truncated MAC received when the link is<br>not in secure mode (when integrity is not enabled and the receiver<br>detects                                                                                                                                                                                                 |

|--|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | 0b0011: MAC header received when not expected (No MAC<br><u>EPCOHEPOCH</u> running but the receiver detects a MAC header)<br>0b0100: MAC Header not received when expected (MAC header<br>not received within 6 flit after MAC <u>EPCOHEPOCH</u> has terminated)<br>0b0101: Truncated MAC flit received when not expected (if the<br>receiver gets truncated MAC flit corresponding to a completed<br>MAC <u>EPCOHEPOCH</u> ) MAC header)<br> |

|  |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

In section 8.2.8, make the following changes:

CXL device registers are mapped in memory space allocated via a standard PCIe BAR. <u>The entry in the</u> Register Locator DVSEC structure (Section 8.1.9) <u>with Register Identifier = 03h (CXL Device Registers</u> <u>Section 8.2.8)</u> describes the BAR number and the offset within the BAR where these registers are mapped. The PCIe BAR shall be marked as prefetchable in the PCI header. At the beginning of the CXL device register block is a CXL Device Capabilities Array Register which defines the size of the CXL Device Capabilities Array followed by a list of CXL Device Capability headers. Each header contains an offset to the capability specific register structure from the start of the CXL device register block.

No registers defined in 8.2.8 are larger than 64-bits wide so that is the maximum access size allowed for these registers. If this rule is not followed, the behavior is undefined. To illustrate how the fields fit together, the layouts in section 8.2.8.1, section 8.2.8.2, and Figure 139. Mailbox Registers are shown as greater than 128-bit register. Implementations are expected to use any size accesses for this information up to 64-bits without loss of functionality – the information is designed to be accessed in chunks, each no greater than 64-bits.

Figure 138. CXL Memory Device Registers

| IN | section | 8.2.8.1, | таке | the | rollowing | cnanges: |  |

|----|---------|----------|------|-----|-----------|----------|--|

|    |         |          |      |     |           |          |  |

| Bits         | Attributes | Description                                                                                            |

|--------------|------------|--------------------------------------------------------------------------------------------------------|

|              |            |                                                                                                        |

| <u>27:24</u> | <u>RO</u>  | <u>Type: Identifies the type-specific capabilities in the CXL Device</u><br><u>Capabilities Array.</u> |

| > |                 |           | <ul> <li>Oh = No type-specific capabilities or type is inferred from the PCI class code.</li> <li>1h = Memory Device Capabilities (Section 8.2.8.5).</li> <li>Other values reserved.</li> </ul> |

|---|-----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 31:2 <u>8</u> 4 | RO        | Reserved                                                                                                                                                                                        |

|   |                 |           |                                                                                                                                                                                                 |

| 0 | <u>127:48</u>   | <u>RO</u> | Reserved                                                                                                                                                                                        |

*In section 8.2.8.2.1, make the following change:*

CXL device capability register structures are identified by a 2-byte identifier as specified in the table below.

- Capability identifiers 0000h-3FFFh describe generic CXL device capabilities as specified in the table below.

- Capability identifiers 4000h-7FFFh describe <u>type</u>-specific capabilities associated with the <u>type</u> specified in the CXL Device Capabilities Array Register (Section 8.2.8.1)-Class Code register in the PCI Header (Offset 09h).

- Capability identifiers 8000h-FFFFh describe vendor specific capabilities.

Capability identifiers 0000h-3FFFh that are not specified in this table are reserved.

|   | Capability ID | Description | Required* | Version |

|---|---------------|-------------|-----------|---------|

| U |               |             |           |         |

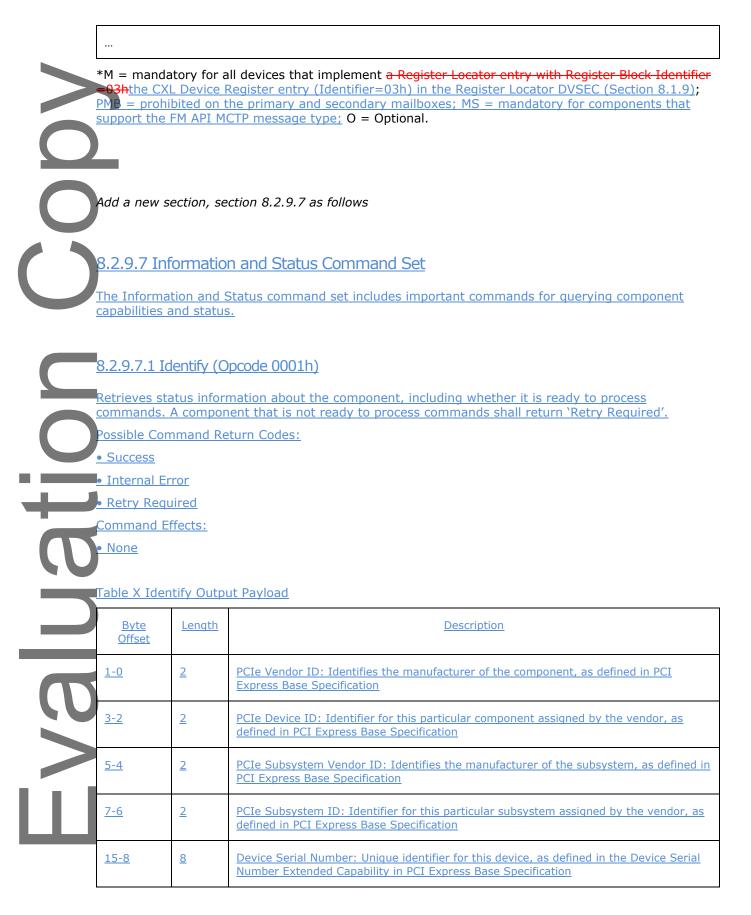

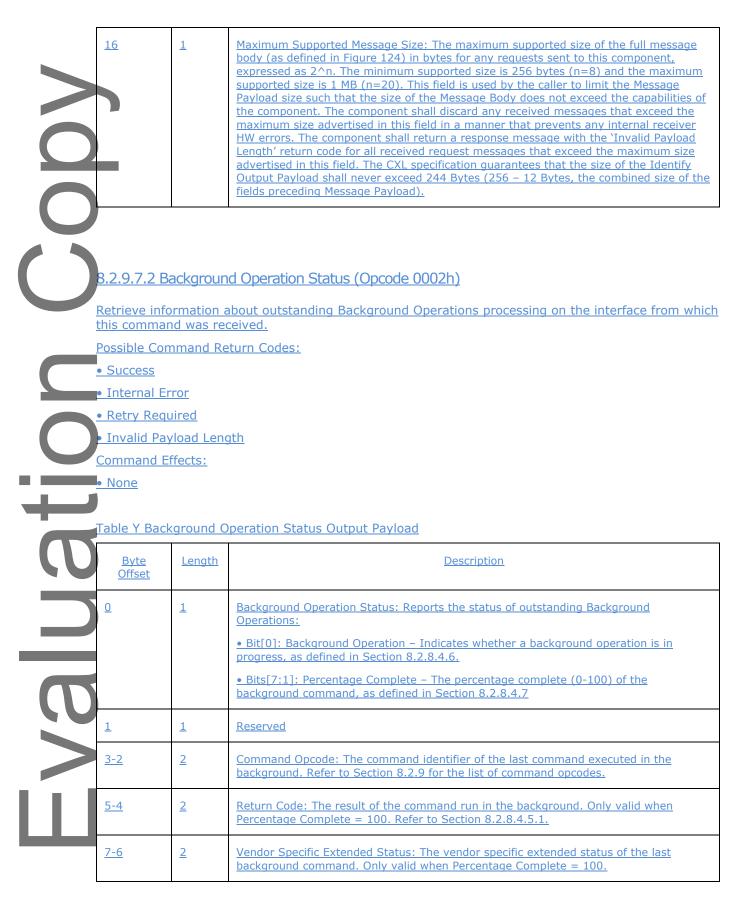

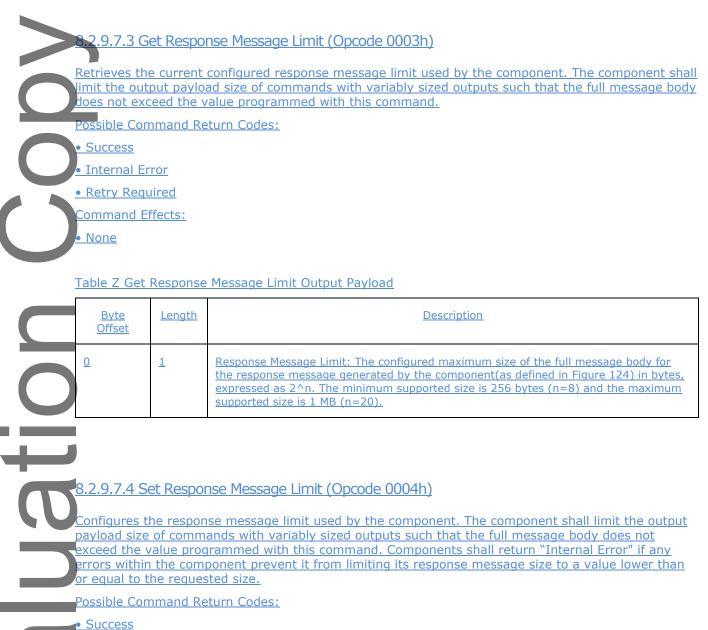

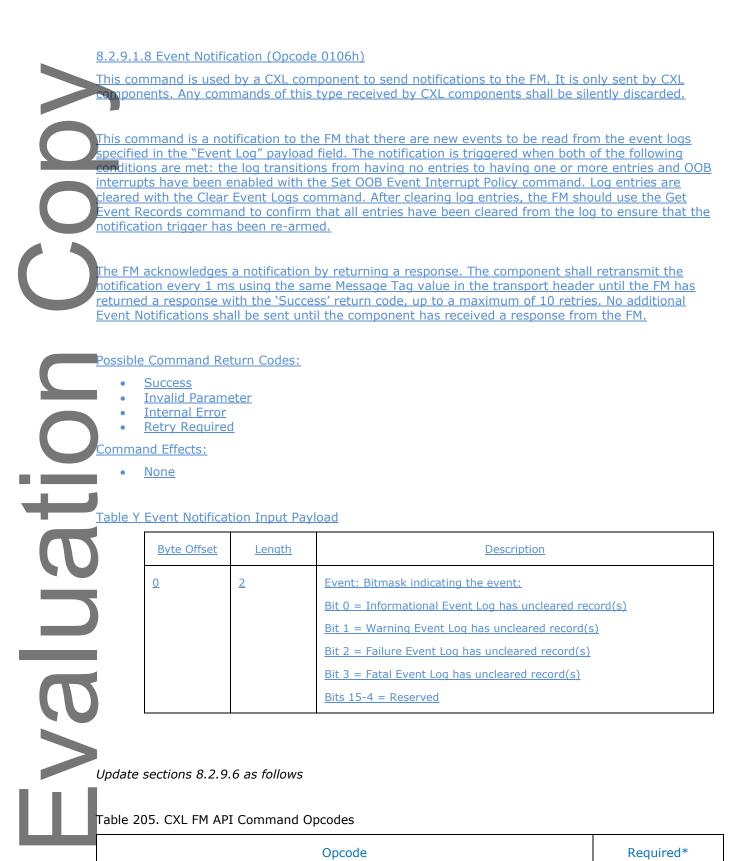

\*M = mandatory for all devices that  $\frac{\text{advertises}}{\text{advertises}}$  implement the CXL Device Register entry (Register Block Identifier=03h) in the Register Locator DVSEC (Section 8.1.9); O = Optional.

In section 8.2.8.4, make the following changes:

In case of a timeout, the caller may attempt to recover the device by either issuing CXL <u>or</u> <u>Conventional</u> reset<del>, hot reset, warm reset or a cold reset</del> to the device.

When a command is successfully started as a background operation, the device shall return the Background Command Started return code defined in Section 8.2.8.4.5.1. While the command is executing in the background, the device should update the percentage complete in the Background Command Status Register at least once per second. Once the command completes in the background, the device shall update the Background Command Status Register with the appropriate return code as defined in Section 8.2.8.4.5.1. The caller may then retrieve the results of the background operation by issuing a new command from the Background Command Status Register.

The mailbox registers are described below.

...

| Bits                                | Attributes     | Description                              | I                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-------------------------------------|----------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                     |                |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| <u>18:11</u>                        | <u>RsvdP</u>   | <u>Reserved</u>                          |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 22:19                               | <u>RO</u>      | • <u>0h</u><br><u>coc</u><br>• <u>1h</u> | <ul> <li>Type: Identifies the type-specific commands supported by the mailbox.</li> <li>Oh = No type-specific commands or type is inferred from the PCI class code.</li> <li><u>1h = Memory Device Commands (Section 8.2.9.5).</u></li> <li>Other values reserved.</li> </ul>                                                                                                                                                       |  |  |  |  |

| 31: <u>23</u> 11                    | RsvdP          | Reserved                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| In section<br><br>Bits              | n 8.2.8.4.5, r | make the foll<br>Attributes              | owing change:<br>Description                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                                     | n 8.2.8.4.5, r |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

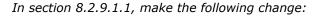

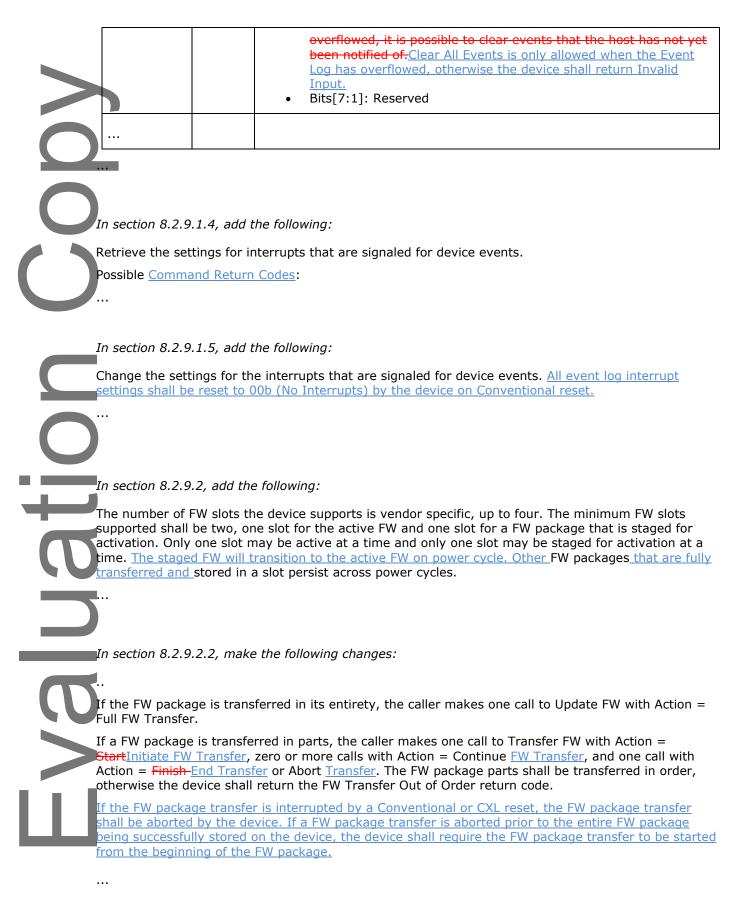

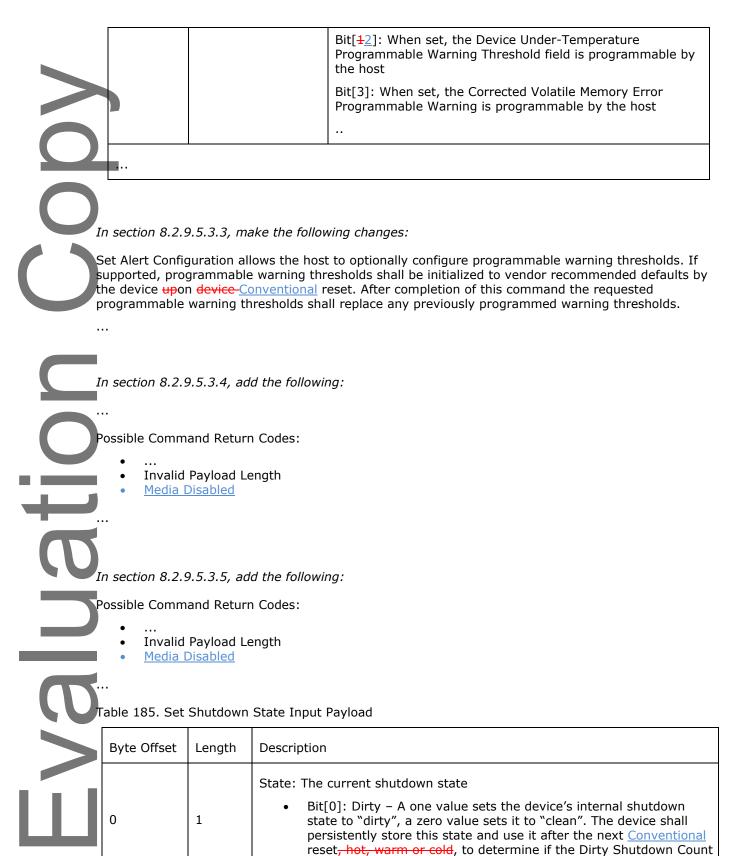

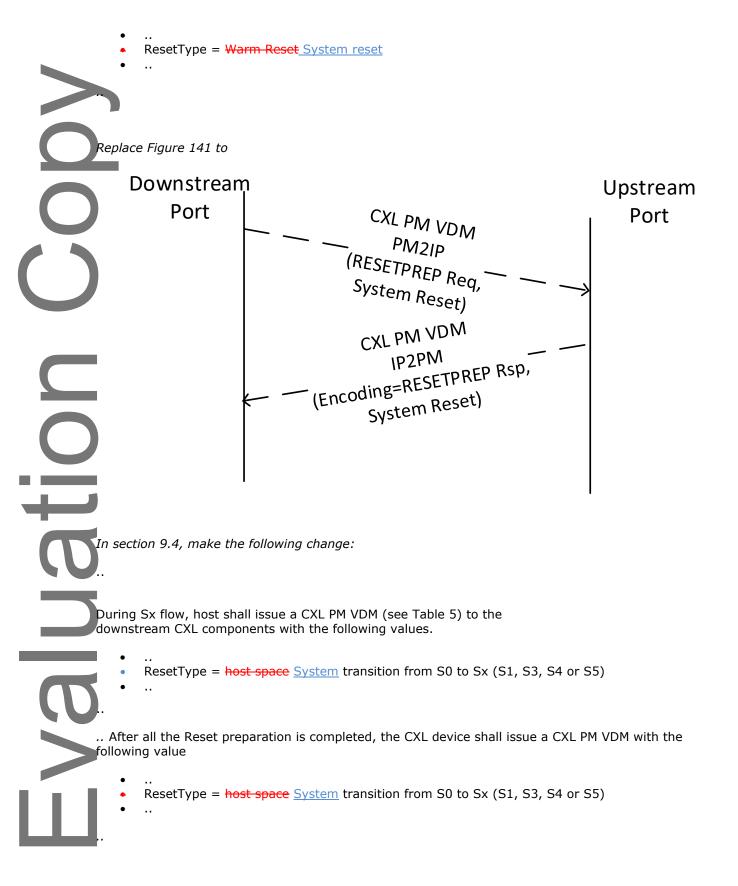

| <br>Bits                            | n 8.2.8.4.5, r |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |