### Compute Express Link<sup>TM</sup> (CXL<sup>TM</sup>)

August 2022

**Errata for the Compute Express Link Specification Revision 3.0**

### LEGAL NOTICE FOR THIS PUBLICLY-AVAILABLE SPECIFICATION FROM COMPUTE EXPRESS LINK CONSORTIUM, INC.

### © 2019-2022 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED.

This CXL Specification (this "<u>CXL Specification</u>" or this "document") is owned by and is proprietary to Compute Express Link Consortium, Inc., a Delaware nonprofit corporation (sometimes referred to as "<u>CXL</u>" or the "<u>CXL Consortium</u>" or the "<u>Company</u>") and/or its successors and assigns.

### NOTICE TO USERS WHO ARE MEMBERS OF THE CXL CONSORTIUM:

If you are a Member of the CXL Consortium (sometimes referred to as a "<u>CXL Member</u>"), and even if you have received this publicly-available version of this CXL Specification after agreeing to CXL Consortium's Evaluation Copy Agreement (a copy of which is available <a href="https://www.computeexpresslink.org/download-the-specification">https://www.computeexpresslink.org/download-the-specification</a>, each such CXL Member must also be in compliance with all of the following CXL Consortium documents, policies and/or procedures (collectively, the "<u>CXL Governing Documents</u>") in order for such CXL Member's use and/or implementation of this CXL Specification to receive and enjoy all of the rights, benefits, privileges and protections of CXL Consortium membership: (i) CXL Consortium's Intellectual Property Policy; (ii) CXL Consortium's Bylaws; (iii) any and all other CXL Consortium policies and procedures; and (iv) the CXL Member's Participation Agreement.

### NOTICE TO NON-MEMBERS OF THE CXL CONSORTIUM:

If you are **not** a CXL Member and have received this publicly-available version of this CXL Specification, your use of this document is subject to your compliance with, and is limited by, all of the terms and conditions of the CXL Consortium's Evaluation Copy Agreement (a copy of which is available at <a href="https://www.computeexpresslink.org/download-the-specification">https://www.computeexpresslink.org/download-the-specification</a>).

In addition to the restrictions set forth in the CXL Consortium's Evaluation Copy Agreement, any references or citations to this document must acknowledge the Compute Express Link Consortium, Inc.'s sole and exclusive copyright ownership of this CXL Specification. The proper copyright citation or reference is as follows: "© 2019-2022 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED." When making any such citation or reference to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of the Compute Express Link Consortium, Inc.

Except for the limited rights explicitly given to a non-CXL Member pursuant to the explicit provisions of the CXL Consortium's Evaluation Copy Agreement which governs the publicly-available version of this CXL Specification, nothing contained in this CXL Specification shall be deemed as granting (either expressly or impliedly) to any party that is <u>not</u> a CXL Member: (ii) any kind of license to implement or use this CXL Specification or any portion or content described or contained therein, or any kind of license in or to any other intellectual property owned or controlled by the CXL Consortium, including without limitation any trademarks of the CXL Consortium.; or (ii) any benefits and/or rights as a CXL Member under any CXL Governing Documents.

### LEGAL DISCLAIMERS FOR ALL PARTIES:

THIS DOCUMENT AND ALL SPECIFICATIONS AND/OR OTHER CONTENT PROVIDED HEREIN IS PROVIDED ON AN "AS IS" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, COMPUTE EXPRESS LINK CONSORTIUM, INC. (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NON-INFRINGEMENT.

In the event this CXL Specification makes any references (including without limitation any incorporation by reference) to another standard's setting organization's or any other party's ("Third Party") content or work, including without limitation any specifications or standards of any such Third Party ("Third Party Specification"), you are hereby notified that your use or implementation of any Third Party Specification: (i) is not governed by any of the CXL Governing Documents; (ii) may require your use of a Third Party's patents, copyrights or other intellectual property rights, which in turn may require you to independently obtain a license or other consent from that Third Party in order to have full rights to implement or use that Third Party Specification; and/or (iii) may be governed by the intellectual property policy or other policies or procedures of the Third Party which owns the Third Party Specification. Any trademarks or service marks of any Third Party which may be referenced in this CXL Specification is owned by the respective owner of such marks.

### NOTICE TO ALL PARTIES REGARDING THE PCI-SIG UNIQUE VALUE PROVIDED IN THIS CXL SPECIFICATION:

NOTICE TO USERS: THE UNIQUE VALUE THAT IS PROVIDED IN THIS CXL SPECIFICATION IS FOR USE IN VENDOR DEFINED MESSAGE FIELDS, DESIGNATED VENDOR SPECIFIC EXTENDED CAPABILITIES, AND ALTERNATE PROTOCOL NEGOTIATION ONLY AND MAY NOT BE USED IN ANY OTHER MANNER, AND A USER OF THE UNIQUE VALUE MAY NOT USE THE UNIQUE VALUE IN A MANNER THAT (A) ALTERS, MODIFIES, HARMS OR DAMAGES THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCISIG ECOSYSTEM OR ANY PORTION THEREOF, OR (B) COULD OR WOULD REASONABLY BE DETERMINED TO ALTER, MODIFY, HARM OR DAMAGE THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF (FOR PURPOSES OF THIS NOTICE, "PCI-SIG ECOSYSTEM" MEANS THE PCI-SIG SPECIFICATIONS, MEMBERS OF PCI-SIG AND THEIR ASSOCIATED PRODUCTS AND SERVICES THAT INCORPORATE ALL OR A PORTION OF A PCI-SIG SPECIFICATION AND EXTENDS TO THOSE PRODUCTS AND SERVICES INTERFACING WITH PCI-SIG MEMBER PRODUCTS AND SERVICES).

LEGAL NOTICE FOR THIS SPECIFICATION FROM COMPUTE EXPRESS LINK CONSORTIUM, INC.

© 2022 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED.

This CXL Errata for the Compute Express Link Specification (this "CXL Specification" or this "document") is owned by and is proprietary to Compute Express Link Consortium, Inc., a Delaware nonprofit corporation (sometimes referred to as "CXL" or the "CXL Consortium" or the "Company") and/or its successors and assigns.

### NOTICE TO USERS WHO ARE MEMBERS OF THE CXL CONSORTIUM:

Members of the CXL Consortium (sometimes referred to as a "CXL Member") must be and remain in compliance with all of the following CXL Consortium documents, policies and/or procedures (collectively, the "CXL Governing Documents") in order for such CXL Member's use and/or implementation of this CXL Specification to receive and enjoy all of the rights, benefits, privileges and protections of CXL Consortium membership: (i) CXL Consortium's Intellectual Property Policy; (ii) CXL Consortium's Bylaws; (iii) any and all other CXL Consortium policies and procedures; and (iv) the CXL Member's Participation Agreement.

### NOTICE TO NON-MEMBERS OF THE CXL CONSORTIUM, INC.:

If you are not a CXL Member and you have obtained a copy of this CXL Specification, you only have a right to review this document or make reference to or cite this document. Any references or citations to this document must acknowledge the Compute Express Link Consortium, Inc's sole and exclusive copyright ownership of this CXL Specification. The proper copyright citation or reference is as follows:

"© 2022 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED." When making any such citation or reference to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of the Compute Express Link Consortium, Inc.

Nothing contained in this CXL Specification shall be deemed as granting (either expressly or impliedly) to any party that is not a CXL Member: (ii) any kind of license to implement or use this CXL Specification or any portion or content described or contained therein, or any kind of license in or to any other intellectual property owned or controlled by the CXL Consortium, including without limitation any trademarks of the CXL Consortium; or (ii) any of the rights, benefits, privileges or protections given to a CXL Member under any CXL Governing Documents. For clarity, and without limiting the foregoing notice in any way, if you are not a CXL Member but still elect to implement this CXL Specification or any portion described herein, you are hereby given notice that your election to do so does not give you any of the rights, benefits, and/or protections of the CXL Members, including without limitation any of the rights, benefits, privileges or protections given to a CXL Member under the CXL Consortium's Intellectual Property Policy.

### LEGAL DISCLAIMERS FOR, AND ADDITIONAL NOTICE TO, ALL PARTIES:

THIS DOCUMENT AND ALL SPECIFICATIONS AND/OR OTHER CONTENT PROVIDED HEREIN ARE PROVIDED ON AN "AS IS" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. COMPUTE EXPRESS LINK CONSORTIUM, INC (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NON-INFRINGEMENT. In the event this CXL Specification makes any references (including without limitation any incorporation by reference) to another standard's setting organization's or any other party's ("Third Party") content or work, including without limitation any specifications or standards of any such Third Party ("Third Party Specification"), you are hereby notified that your use or implementation of any Third Party Specification: (i) is not governed by any of the CXL Governing Documents; (ii) may require your use of a Third Party's patents, copyrights or other intellectual property rights, which in turn may require you to independently obtain a license or other consent from that Third Party in order to have full rights to implement or use that Third Party Specification; and/or (iii) may be governed by the intellectual property policy or other policies or procedures of the Third Party which owns the Third Party Specification. Any trademarks or service marks of any Third Party which may be referenced in this CXL Specification is owned by the respective owner of such marks. The COMPUTE EXPRESS LINK®, CXL® and CXL LOGO trademarks (the "CXL

Trademarks") are all owned by the Company and are registered trademarks in the United States and in other jurisdictions. All rights are reserved in all of the CXL Trademarks.

NOTICE TO ALL PARTIES REGARDING THE PCI-SIG UNIQUE VALUE PROVIDED IN THIS SPECIFICATION DOCUMENT:

NOTICE TO USERS: THE UNIQUE VALUE THAT IS PROVIDED IN THIS SPECIFICATION FOR USE IN VENDOR DEFINED MESSAGE FIELDS, DESIGNATED VENDOR SPECIFIC EXTENDED CAPABILITIES, AND ALTERNATE PROTOCOL NEGOTIATION ONLY AND MAY NOT BE USED IN ANY OTHER MANNER, AND A USER OF THE UNIQUE VALUE MAY NOT USE THE UNIQUE VALUE IN A MANNER THAT (A) ALTERS, MODIFIES, HARMS OR DAMAGES THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG\* ECOSYSTEM OR ANY PORTION THEREOF, OR (B) COULD OR WOULD REASONABLY BE DETERMINED TO ALTER, MODIFY, HARM OR DAMAGE THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF (FOR PURPOSES OF THIS NOTICE, "PCI-SIG ECOSYSTEM" MEANS THE PCI-SIG SPECIFICATIONS, MEMBERS OF PCI-SIG AND THEIR ASSOCIATED PRODUCTS AND SERVICES THAT INCORPORATE ALL OR A PORTION OF A PCI-SIG SPECIFICATION AND EXTENDS TO THOSE PRODUCTS AND SERVICES INTERFACING WITH PCI-SIG MEMBER PRODUCTS AND SERVICES).

### Errata for the Compute Express Link Specification Revision 3.0

Aug 30, 2022

# Contents

| Section | 3.3.7   | and   | Section | 4.3,  | BIRsp  | PBR   | message  | requires | SPID | field | <br>6 |

|---------|---------|-------|---------|-------|--------|-------|----------|----------|------|-------|-------|

| Latency | /-Ontir | nized | d Empty | Flits | Alloca | te to | Tx Retry | Buffer   |      |       | <br>8 |

**Revision History**

| Revision | Description          | Date            |

|----------|----------------------|-----------------|

| 1.0      | First Release: G1-G2 | August 30, 2022 |

## al uation

### G1 Section 3.3.7 and Section 4.3, BIRsp PBR message requires SPID field

The specification is missing the SPID in the PBR-format version of the BIRsp message, and this field is required to make FAM device memory isolation secure. For G-FAM, the GFD uses the SPID to associate the BIRsp with its outstanding BISnp. For an LD-FAM MLD connected via a PBR Edge Port, the Edge Port uses the SPID to determine the appropriate LD-ID to use in an HBR-format BIRsp message going to the MLD, which may pass through one or more HBR switches below the PBR switch. The security model will be covered in later specification updates.

### B.3.7 M2S Back-Invalidate Response (BIRsp)

The Back-Invalidate Response (BIRsp) message class contains response messages from the Master to the Subordinate as a result of Back-Invalidate Snoops. This message class is not supported in 68B Flit mode.

Table 3-37 M2S BIRsp Fields

|         | Width (Bits) |          | s)           |                                                                                                                                                                                                                                                  |  |

|---------|--------------|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field   | 68B<br>Flit  |          |              | Description                                                                                                                                                                                                                                      |  |

| Valid   |              | :        | 1            | The valid signal indicates that this is a valid response                                                                                                                                                                                         |  |

| Opcode  |              | 4        | 1            | Response type with encodings in Table 3-38                                                                                                                                                                                                       |  |

| BI-ID   |              | 12       | 0            | BI-ID of the device that is the destination of the message. See Section 9.14 for details on how this field is assigned to devices. Not applicable in PBR messages where DPID infers this field.                                                  |  |

| BITag   |              | 12       |              | Tracking ID from the device                                                                                                                                                                                                                      |  |

| LowAddr |              | 2        | 2            | The lower 2 bits of Cacheline address (Address[7:6]). This is needed to differentiate snoop responses when a Block Snoop is sent and receives snoop response for each cacheline. For block response (opcode names *Blk), this field is Reserved. |  |

| DPID    | N/A          | 0        | 12           | Destination Port ID                                                                                                                                                                                                                              |  |

| SPID    |              | <u>O</u> | <u>12</u>    | Source Port ID                                                                                                                                                                                                                                   |  |

| RSVD    |              | 9        |              |                                                                                                                                                                                                                                                  |  |

| Total   |              | 40       | <u>52</u> 40 |                                                                                                                                                                                                                                                  |  |

### 4.3 CXL.cachemem Link Layer 256B Flit Mode

<Below are various tables and slot formats that need to need to reflect the larger PBR message size>

Table 4-14.256B G-Slot Formats

|   |        |                     |                     | HBR            |          |                                   | PBR          |                                |

|---|--------|---------------------|---------------------|----------------|----------|-----------------------------------|--------------|--------------------------------|

|   | Format | SlotFmt<br>Encoding | Messages            | Downstrea<br>m | Upstream | Length<br>in Bits<br>(Max<br>124) | Messages     | Length<br>in Bits<br>(Max 124) |

|   | G0     | 0000b               | H2D REQ + H2D RSP   | Х              |          | 112                               | H2D Req      | 92                             |

|   | G1     | 0001b               | 3 H2D RSP           | Х              |          | 120                               | 2 H2D RSP    | 96                             |

|   | G2     | 0010b               | D2H Req + 2 D2H RSP |                | Х        | 124                               | D2H REQ      | 96                             |

|   | G3     | 0011b               | 4 D2H RSP           |                | Х        | 96                                | 3 D2H RSP    | 108                            |

|   | G4     | 0100b               | M2S REQ             | Х              |          | 100                               | M2S Req      | 120                            |

|   | G5     | 0101b               | 3 M2S BIRsp         | Х              |          | 120                               | 23 M2S BIRsp | 1 <u>04</u> <del>20</del>      |

|   | G6     | 0110b               | S2M BISnp + S2M NDR |                | х        | 124                               | S2M BISnp    | 96                             |

|   | G7     | 0111b               | 3 S2M NDR           |                | Х        | 120                               | 2 S2M NDR    | 96                             |

|   | G8     | 1000b               |                     |                |          |                                   |              |                                |

|   | G9     | 1001b               | DCI/D               |                |          |                                   | DC//D        |                                |

|   | G10    | 1010b               | RSVD                |                |          |                                   | RSVD         |                                |

|   | G11    | 1011b               |                     |                |          |                                   |              |                                |

|   | G12    | 1100b               | 4 H2D DH            | Х              |          | 112                               | 3 H2D DH     | 108                            |

| 5 | G13    | 1101b               | 4 D2H DH            |                | Х        | 96                                | 3 D2H DH     | 108                            |

|   | G14    | 1110b               | M2S RwD             | Х              |          | 104                               | M2S RwD      | 124                            |

| 5 | G15    | 1111b               | 3 S2M DRS           |                | Х        | 120                               | 2 S2M DRS    | 96                             |

Table 4-15. 256B H-Slot Formats

|        | HBR                 |                     | PBR        | PBR      |                                   |           |                                |

|--------|---------------------|---------------------|------------|----------|-----------------------------------|-----------|--------------------------------|

| Format | SlotFmt<br>Encoding | Messages            | Downstream | Upstream | Length<br>in Bits<br>(Max<br>108) | Messages  | Length<br>in Bits<br>(Max 108) |

| НО     | 0000b               | H2D REQ             | Х          |          | 72                                | H2D Req   | 92                             |

| H1     | 0001b               | 2 H2D RSP           | х          |          | 80                                | 2 H2D RSP | 96                             |

| H2     | 0010b               | D2H Req + 1 D2H RSP |            | X        | 100                               | D2H REQ   | 96                             |

| Н3     | 0011b               | 4 D2H RSP           |            | х        | 96                                | 3 D2H RSP | 108                            |

| H4        | 0100b | M2S REQ     | X |   | 100 | M2S Req<br>(Zero Extended) | 108 (120)         |

|-----------|-------|-------------|---|---|-----|----------------------------|-------------------|

| Н5        | 0101b | 2 M2S BIRsp | х |   | 80  | 2 M2S BIRsp                | <del>80</del> 104 |

| Н6        | 0110b | S2M BISnp   |   | Х | 84  | S2M BISnp                  | 96                |

| H7        | 0111b | 2 S2M NDR   |   | Х | 80  | 2 S2M NDR                  | 96                |

| /<br>  H8 | 1000b | LLCTRL      |   |   |     | LLCTRL                     |                   |

| Н9        | 1001b |             |   |   |     |                            |                   |

| H10       | 1010b | RSVD        |   |   |     | RSVD                       |                   |

| H11       | 1011b |             |   |   |     |                            |                   |

| H12       | 1100b | 3 H2D DH    | х |   | 84  | 3 H2D DH                   | 108               |

| H13       | 1101b | 4 D2H DH    |   | Х | 96  | 3 D2H DH                   | 108               |

| H14       | 1110b | M2S RwD     | Х |   | 104 | M2S RwD<br>(Zero Extended) | 108 (124)         |

| H15       | 1111b | 2 S2M DRS   |   | х | 80  | 2 S2M DRS                  | 96                |

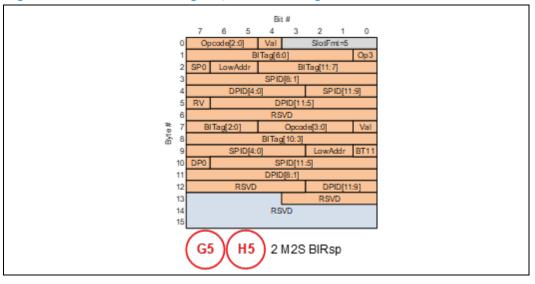

<Figure below replaces the CXL3 figure>

Figure 4-57. 256B Packing: G5/H5 PBR Messages

### G2 Latency-Optimized Empty Flits Allocate to Tx Retry Buffer

Currently, CXL.cachemem Empty flits are not allocated to the Tx Retry Buffer. This errata makes a change to allocate Latency-Optimized Empty Flits to the Tx Retry Buffer. Note, Standard Empty Flits are not impacted by this errata.

August 30, 2022 8

Valuatio

In Section 6.2.3.11, make the following update:

The 2 bytes of Flit Header as defined in Table 6-5 are transmitted as the first two bytes of the flit. The 2-bit Flit Type field indicates whether the flit carries CXL.io traffic, CXL.cachemem traffic, ALMPs, IDLE flits, Empty flits, or NOP flits. Please refer to Setion 6.2.3.1.1.1 for more details. The Prior Flit Type definition is as defined in PCIe Base Specification; it enables the receiver to know that the prior flit was an non-retryable Empty flit, NOP flit, or IDLE flit, and thus does not require replay (i.e., can be discarded) if it has a CRC error. The Type of DLLP Payload definition is as defined in PCIe Base Specification for CXL.io flits; otherwise, this bit is reserved. The Replay Command[1:0] and Flit Sequence Number[9:0] definitions are as defined in PCIe Base Specification.

In Table 6-5, make the following update:

Table 6-5. 256B Flit Header

| Flit Header Field            | Flit Header<br>Bit Location | Description                                                                                                                                                                                                                                    |

|------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flit Type[1:0]               | [7:6]                       | 00b = Physical Layer IDLE flit or Physical Layer NOP flit or CXL.io NOP flit     01b = CXL.io Payload flit     10b = CXL.cachemem Payload flit or CXL.cachemem generated Empty flit     11b = ALMP Please refer to Table 6-6 for more details. |

| Prior Flit Type              | [5]                         | <ul> <li>0 = Prior flit was an non-retryable Empty, NOP, or IDLE flit (not allocated into Replay buffer)</li> <li>1 = Prior flit was a Payload flit or retryable Empty flit (allocated into Replay buffer)</li> </ul>                          |

| Type of DLLP Payload         | [4]                         | <ul> <li>If (Flit Type = (CXL.io Payload or CXL.io NOP): Use as defined in PCIe Base Specification</li> <li>If (Flit Type != (CXL.io Payload or CXL.io NOP)): Reserved</li> </ul>                                                              |

| Replay Command[1:0]          | [3:2]                       | Same as defined in PCIe Base Specification.                                                                                                                                                                                                    |

| Flit Sequence<br>Number[9:0] | {[1:0], [15:8]}             | 10-bit Sequence Number as defined in PCIe<br>Base Specification                                                                                                                                                                                |

*In section 6.2.3.1.1.1, make the following update:*

A Flit Type encoding of 10b indicates either a flit with valid CXL.cachemem Payload flit or a CXL.cachemem Empty flit; this enables CXL.cachemem to minimize idle to valid traffic transitions by arbitrating for use of the ARB/MUX transmit data path even while it does not have valid traffic to send so that it can potentially fill later slots in the flit with late arriving traffic, instead of requiring CXL.cachemem to wait until the next 256-byte flit boundary to begin transmitting valid traffic. CXL.cachemem Empty flits associated with standard 256B flits are non-retryable and must not be allocated into the transmit retry buffer or receive retry buffer. On the other hand, CXL.cachemem Empty flits associated with latency-optimized 256B flits are retryable and must be allocated into the transmit retry buffer.

Table 6-5. Flit Type[1:0]

|          | Facoding | Flit Payload            | Source                         | Description                                                                                                                                                                                                                               | Allocated<br>to Retry<br>Buffer?                                     |

|----------|----------|-------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 0        |          | Physical Layer<br>NOP   | Physical<br>Layer              | Physical Layer generated (and sunk) flit with no valid payload; inserted in the data stream when its Tx retry buffer is full and it is backpressuring the upper layer or when no other flits from upper layers are available to transmit. | No                                                                   |

| 0        | 00Ь      | IDLE                    | ,                              | Physical Layer generated (and consumed) all 0s payload flit used to facilitate LTSSM transitions as described in PCIe Base Specification                                                                                                  | No                                                                   |

|          |          | CXL.io NOP              | CXL.io<br>Link Layer           | Valid CXL.io DLLP payload (no TLP payload); periodically inserted by the CXL.io link layer to satisfy the PCIe Base Specification requirement for a credit update interval if no other CXL.io flits are available to transmit.            | No                                                                   |

|          | 01b      | CXL.io Payload          |                                | Valid CXL.io TLP and valid DLLP payload                                                                                                                                                                                                   | Yes                                                                  |

|          |          | CXL.cachemem<br>Payload |                                | Valid CXL.cachemem slot and/or CXL.cachemem credit payload                                                                                                                                                                                | Yes                                                                  |

| Lati     | 10b      | CXL.cachemem<br>Empty   | CXL.cache<br>mem Link<br>Layer | No valid CXL.cachemem payload; generated when CXL.cachemem link layer speculatively arbitrates to transfer a flit to reduce idle to valid transition time but no valid CXL.cachemem payload arrives in time to use any slots in the flit. | If non-retryable: No  If retryable: Allocate to Tx Retry Buffer only |

|          | 11b      | ALMP                    | ARB/MUX                        | ARB/MUX Link Management Packet                                                                                                                                                                                                            | Yes                                                                  |

| <b>В</b> |          |                         |                                |                                                                                                                                                                                                                                           |                                                                      |