# OpenCAPI 4.0 Transaction Layer

Specification

Version 1.0 16 June 2020

## **Approved**

Approved for Distribution to OpenCAPI Members

Approved for Distribution to Non-Members for Learning Purposes Only

## **OpenCAPI 4.0 Transaction Layer Specification**

OpenCAPI TL Specification Work Group OpenCAPI Consortium

Version 1.0 (16 June 2020)

Copyright © OpenCAPI Consortium 2016-2020.

Printed in the United States of America February 5, 2021 .

Use of this document is controlled by the OpenCAPI Consortium License Agreement, which is available at <a href="https://opencapi.org/license/">https://opencapi.org/license/</a>.

All capitalized terms in the following text have the meanings assigned to them in the OpenCAPI Intellectual Property Rights Policy (the "OpenCAPI IPR Policy"). The full Policy may be found at the OpenCAPI Consortium website.

THE SPECIFICATION IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY, COMPLETENESS AND NONINFRINGEMENT OF THIRD PARTY RIGHTS. IN NO EVENT SHALL LICENSOR, ITS MEMBERS OR ITS CONTRIBUTORS BE LIABLE FOR ANY CLAIM, OR ANY DIRECT, SPECIAL, INDIRECT OR CONSEQUENTIAL DAMAGES, OR ANY DAMAGES WHATSOEVER RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, ARISING OUT OF OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THE SPECIFICATION.

OpenCAPI and the OpenCAPI logo design are trademarks of the OpenCAPI Consortium.

Other company, product, and service names may be trademarks or service marks of others.

## **Abstract**

This document details the OpenCAPI TL specification. It is the work product of the OpenCAPI Consortium TL Specification Work Group.

This document is handled in compliance with the requirements outlined in the OpenCAPI Consortium Work Group (WG) process document. Comments, questions, etc. can be submitted to <a href="mailto:membership@opencapi.org">membership@opencapi.org</a>.

## **Participants**

Brian Allison, IBM, Chair

Michael Siegel, IBM, Technical Editor

Sanjay Goyal, Microchip Curt Wollbrink, IBM Rick Hagen, NVIDIA

Paul Hartke, Xilinx

## **Contents**

| List of figures                                                                                | 7  |

|------------------------------------------------------------------------------------------------|----|

| List of tables                                                                                 | 8  |

| Revision log                                                                                   | 10 |

| About this document                                                                            | 11 |

| Architecture compliance terminology                                                            | 11 |

| Conventions used in this specification                                                         | 11 |

| Bit and byte numbering                                                                         | 11 |

| Representation of numbers                                                                      | 12 |

| RTL notation                                                                                   | 12 |

| Notes                                                                                          |    |

| Engineering notes                                                                              |    |

| Developer notes                                                                                | 13 |

| Command flows and transaction diagrams                                                         |    |

| Command flow diagrams                                                                          |    |

| Transaction diagrams                                                                           | 14 |

| Terms                                                                                          | 17 |

|                                                                                                |    |

| 1. Overview                                                                                    | 26 |

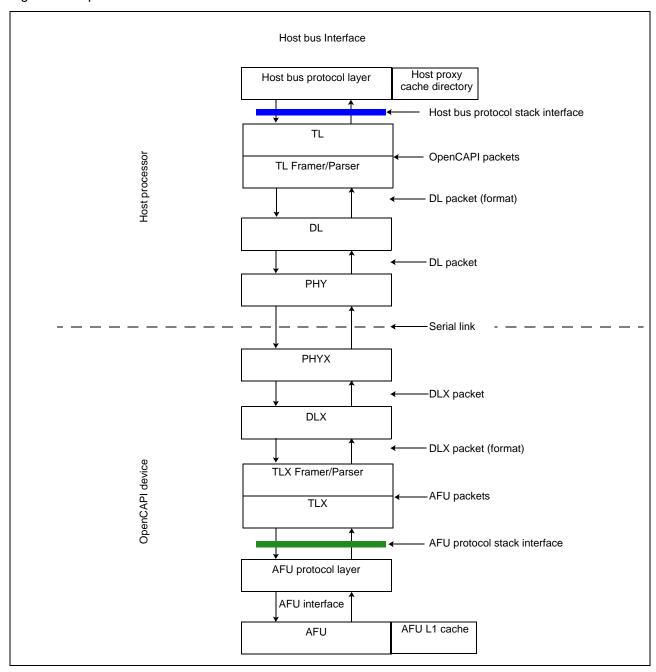

| 1.1 OpenCAPI protocol stack                                                                    | 27 |

| 1.2 Host operation modes                                                                       | 28 |

| 1.2.1 No attached device (C0, M0)                                                              |    |

| 1.2.2 MEM-only mode (C0, M1)                                                                   |    |

| 1.2.3 Checkout mode (C1, M0)                                                                   |    |

| 1.2.4 Checkout with MEM (C1, M1)                                                               |    |

| 1.2.5 Cache-only mode (C2, M0)                                                                 |    |

| 1.2.6 Cache + MEM mode (C2, M1)                                                                |    |

| 1.3 AFU <sub>C2</sub>                                                                          |    |

| 1.3.1 Host proxy cache                                                                         |    |

| 1.3.2 AFU <sub>C2</sub> model                                                                  |    |

| 1.3.2.1 host_tag database                                                                      |    |

| 1.3.2.2 L1 EA cache directory                                                                  |    |

| 1.3.3 AFU cache states                                                                         |    |

| 1.3.4 AFU Cache states                                                                         |    |

| 1.3.5 Design considerations when the AFU <sub>C2</sub> and host cache line sizes are different |    |

| 1.3.5.1 Read commands                                                                          |    |

| 1.3.5.2 Force evict                                                                            |    |

| 1.3.5.3 Upgrade state command                                                                  |    |

| 1.4 Command ordering                                                                           |    |

| 1.5 Host tags                                                                                  |    |

| 1.5.1 host_tag run-length-capability                                                           |    |

| 1.5.2 host_tag update ordering                                                                 |    |

|    | 1.5.2.1 TL and host rules                                    |     |

|----|--------------------------------------------------------------|-----|

|    | 1.5.2.2 TLX and AFU rules                                    |     |

|    | 1.6 Write fragmentation ordering and atomicity               |     |

|    | 1.6.1 Write fragmentation ordering and atomicity at the host |     |

|    | 1.6.1.1 Partial write operations                             |     |

|    | 1.6.1.2 64-,128-, 256-byte write operations                  | 42  |

|    | 1.6.2 Write fragmentation ordering and atomicity at the AFU  |     |

|    | 1.6.2.2 64-, 128-, 256-byte write operations                 |     |

|    | 1.7 OpenCAPI device PA space specification                   |     |

|    | 1.7.1 PA-to-RA mapping rules                                 |     |

|    | 1.8 Address translation                                      |     |

|    | 1.8.1 Effective to real address translation                  |     |

|    | 1.8.2 Translated addresses, AFU ATC, and dot-t commands      |     |

|    | 1.8.2.1 AFU initiated AFU ATC entry invalidation             |     |

|    | 1.8.2.2 Host initiated AFU ATC entry invalidation            |     |

|    | ,                                                            |     |

| 2. | . TL and TLX command and response specifications             | 48  |

|    | 2.1 Handling multiple responses to a single command          |     |

|    | 2.1.1 TLX Read request getting multiple TL responses         |     |

|    | 2.1.2 TLX Write request getting multiple TL responses        |     |

|    | 2.1.3 TL read request getting multiple TLX responses.        |     |

|    | 2.1.4 TL write request getting multiple TLX responses        | 55  |

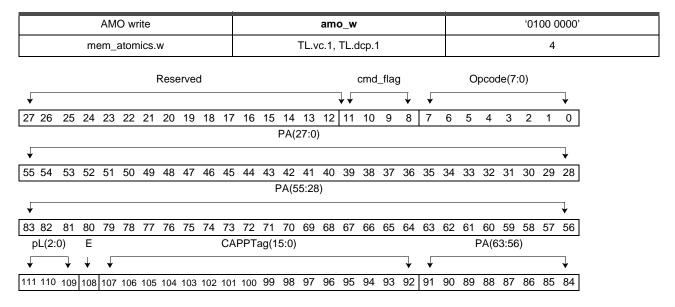

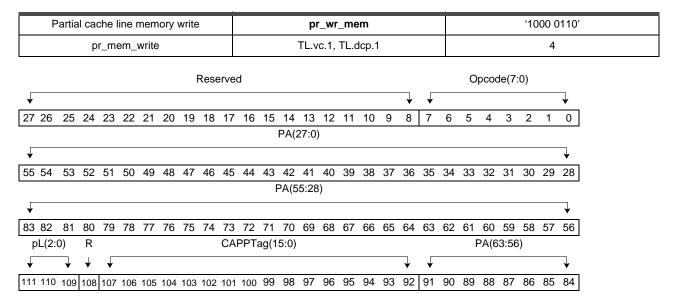

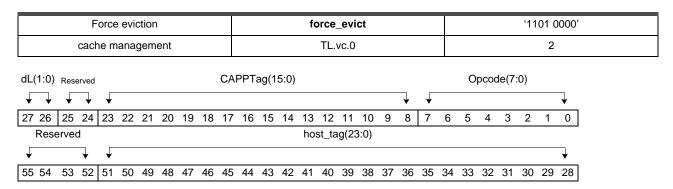

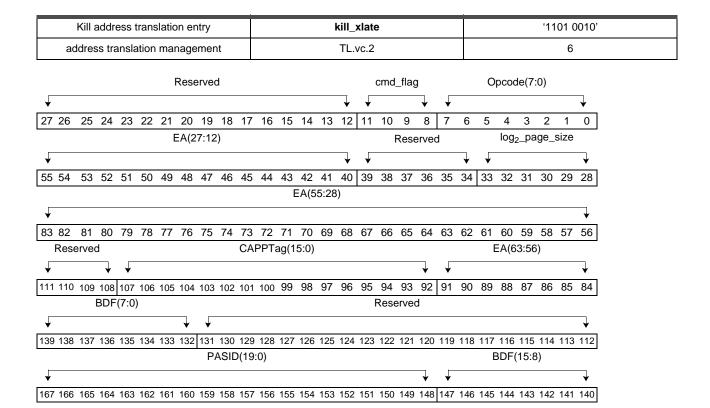

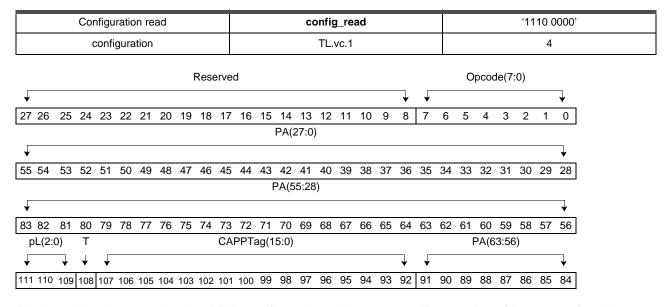

|    | 2.2 TL CAPP command packets                                  | 57  |

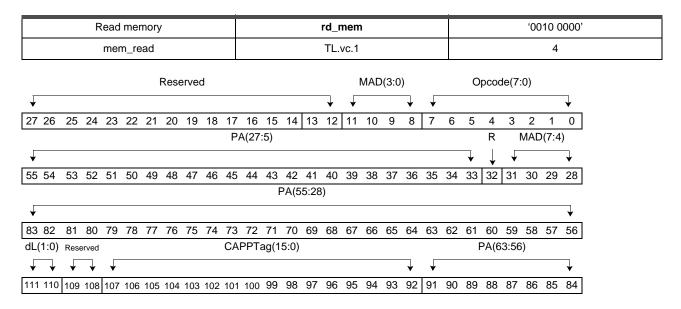

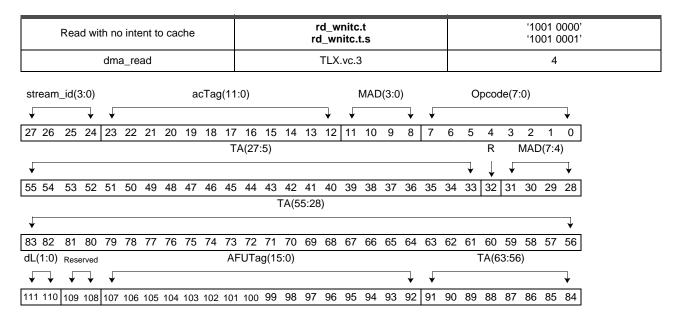

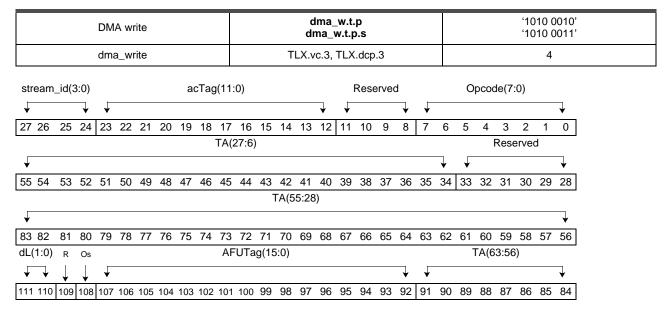

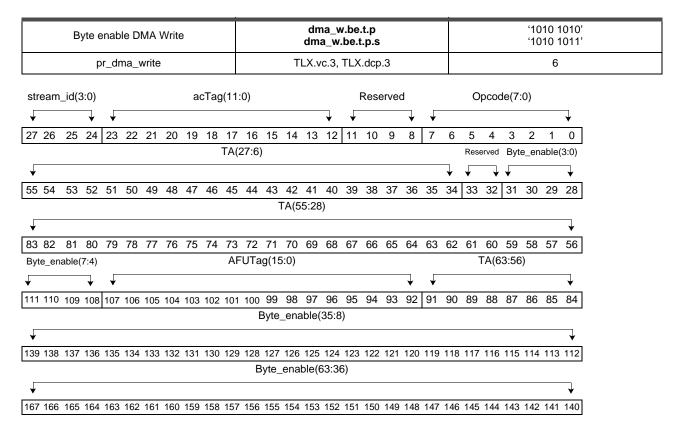

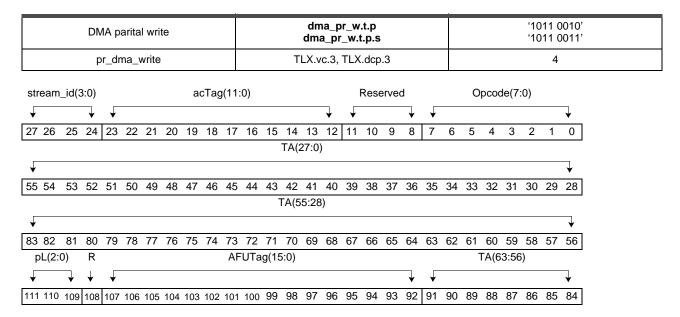

|    | 2.3 TLX AP command packets                                   | 82  |

|    | 2.4 TL CAPP response packets                                 | 122 |

|    | 2.5 TLX AP response packets                                  | 150 |

| 2  | Virtual channel and data gradit need appointed               | 162 |

| ა. | Virtual channel and data credit pool specification           |     |

|    | 3.1 Virtual channel                                          |     |

|    | 3.1.2 TL command and response VC (TL.vc)                     |     |

|    | 3.1.3 VC credit count specification                          |     |

|    | 3.2 Data credit pool                                         |     |

|    | 3.2.1 TLX data DCP (TLX.dcp)                                 |     |

|    | 3.2.2 TL data DCP (TL.dcp)                                   |     |

|    | 3.2.3 DCP credit count specification                         |     |

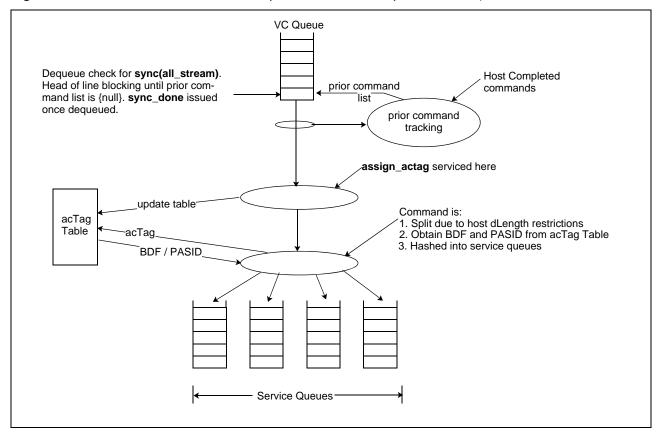

|    | 3.3 TL Virtual channel and service queues                    |     |

|    | 3.3.1 Host TLX command handling                              |     |

|    | 3.3.2 Host TLX response handling                             |     |

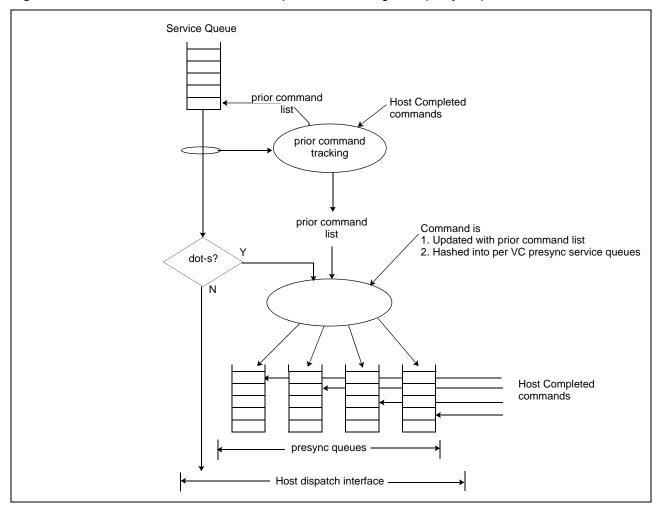

|    | 3.4 TL Presync queues                                        |     |

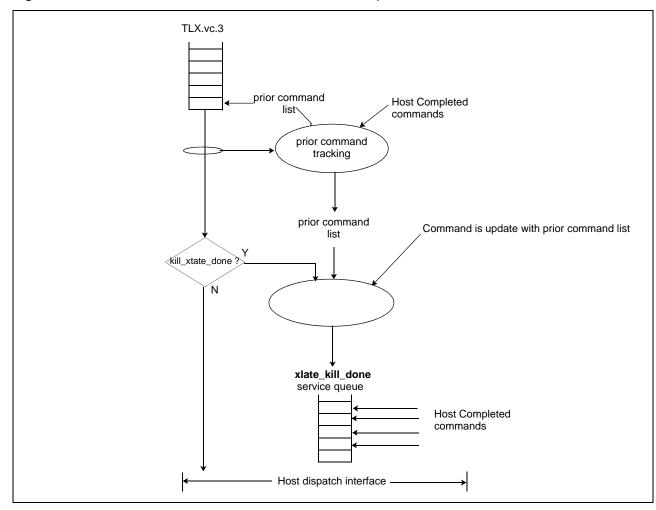

|    | 3.4.1 TL queuing and service of kill_xlate_done              |     |

|    | 3.5 Device TL virtual channel queues                         |     |

|    | 3.6 Virtual channel dependency rules                         |     |

|    | 3.6.1 Dependency loop 1 resolution                           |     |

|    |                                                              |     |

| 4. | . The acTag table                                            | 180 |

|    | 4.1 acTag table contents                                     |     |

|    | <del>-</del>                                                 |     |

| 4.2 acTag table access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 180                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 4.2.1 Error cases when accessing the acTag table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| 4.3 acTag entry management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 180                      |

| 5. DL frame format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 182                      |

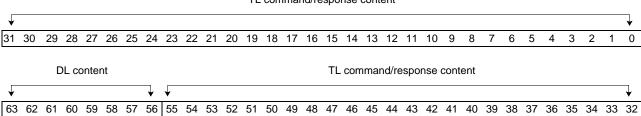

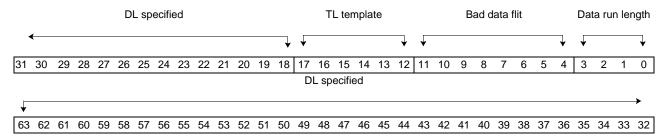

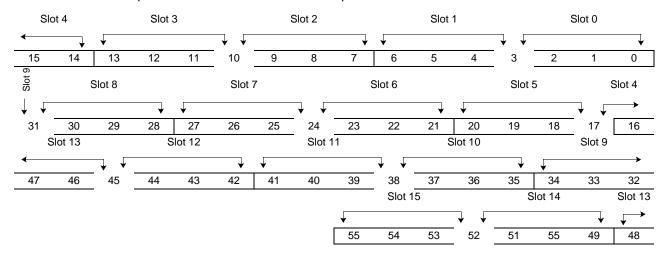

| 5.1 DL frame control flit (64 bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 183                      |

| 5.1.1 DL content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| 5.1.2 TL command/response content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

| 5.1.3 Data transport, order, and alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| 5.1.3.1 Data alignment for commands and responses specifying a host_tag field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 186                      |

| 6. TL and TLX template specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 189                      |

| 6.1 TLX receive and TL transmit template capability specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 191                      |

| 6.2 TL receive and TLX transmit template capability specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 194                      |

| 6.3 Control-flit rate capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 195                      |

| 6.4 Metadata capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 196                      |

| 7. Error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 197                      |

| 7.1 Error events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 198                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 8. OpenCAPI profiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 210                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| Appendix A. AP (TLX) command transaction diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 219                      |

| Appendix A. AP (TLX) command transaction diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b> 219</b><br>219       |

| Appendix A. AP (TLX) command transaction diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>219</b><br>219<br>221 |

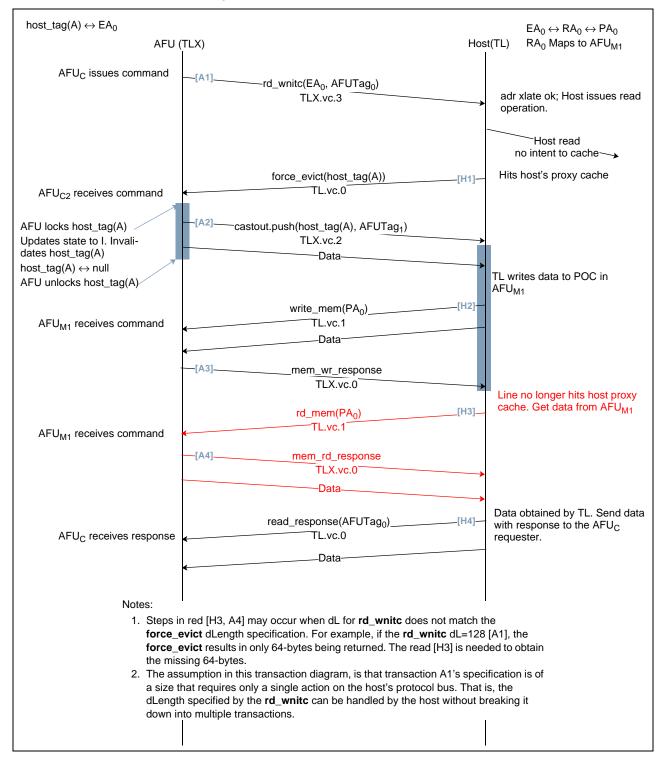

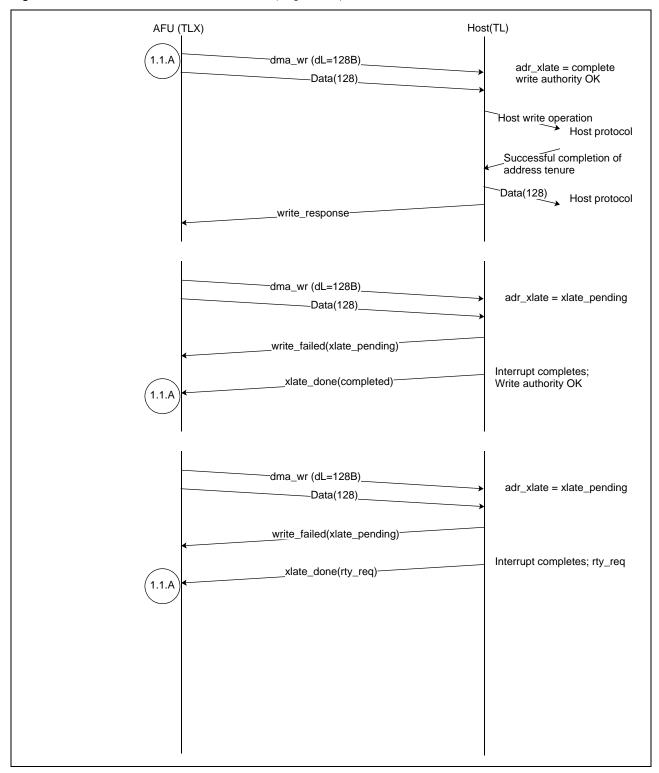

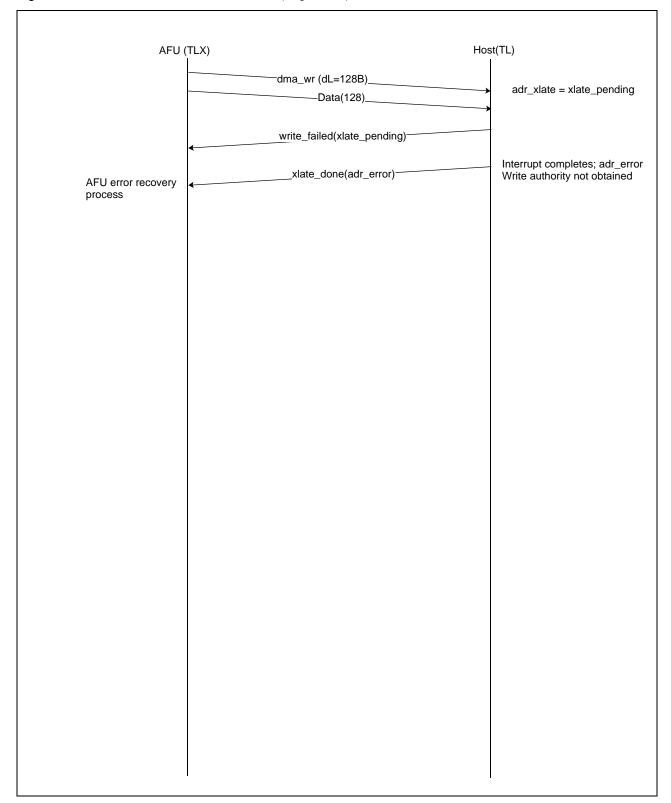

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes                                                                                                                                                                                                                                                                                                                                                                                                        | <b>219</b> 219 221 222   |

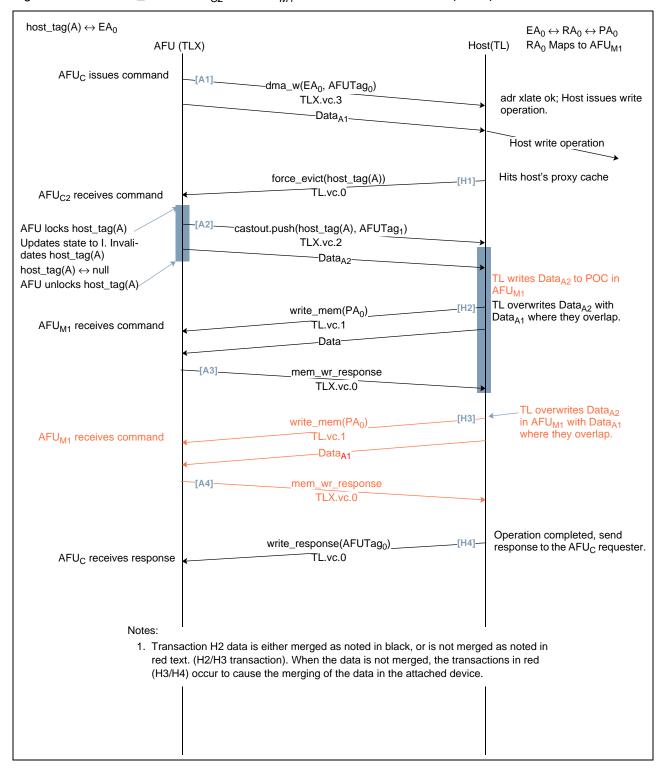

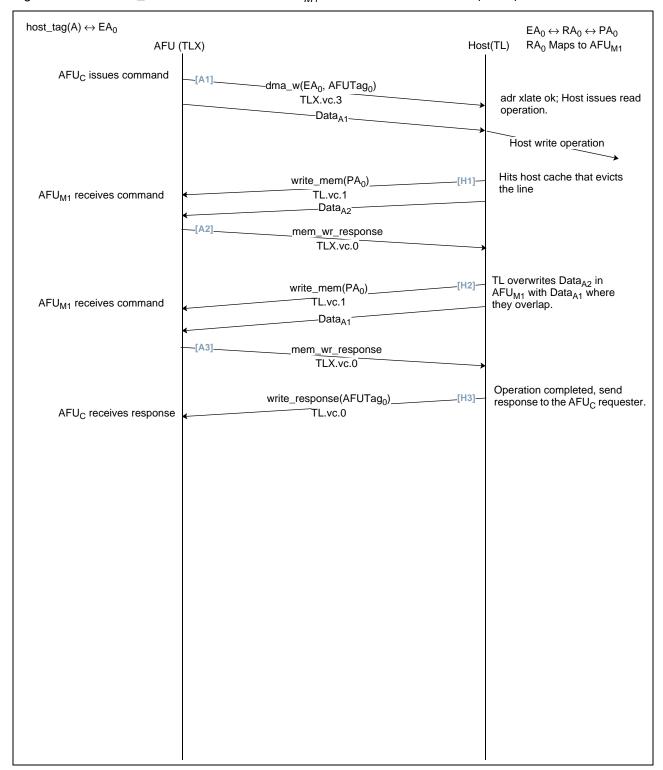

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub>                                                                                                                                                                                                                                                                                                                      | 219 219 221 222 225      |

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub>                                                                                                                                                                                                                                                           |                          |

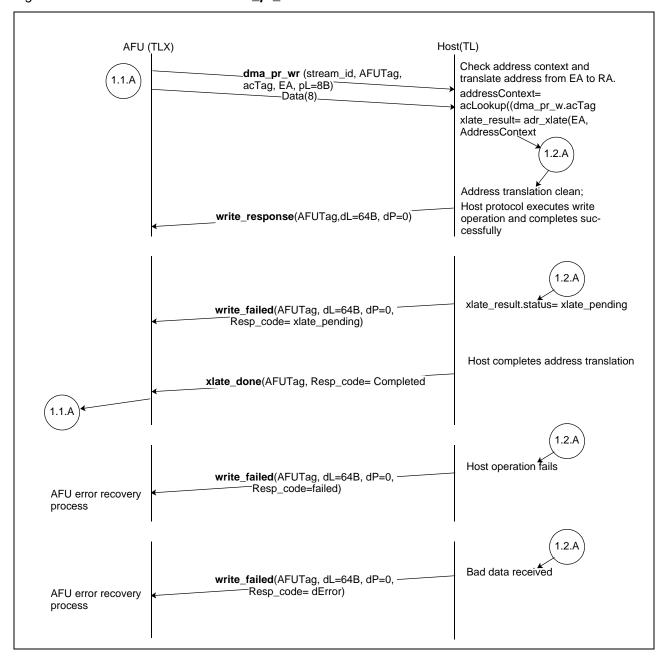

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub> A.6 AFU DMA partial write; non-posted, 8 bytes                                                                                                                                                                                                            |                          |

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub>                                                                                                                                                                                                                                                           |                          |

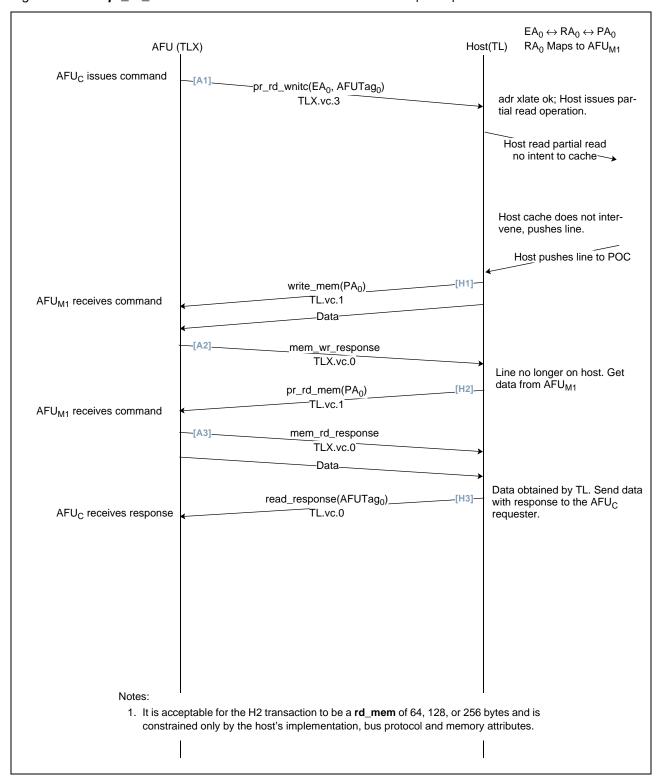

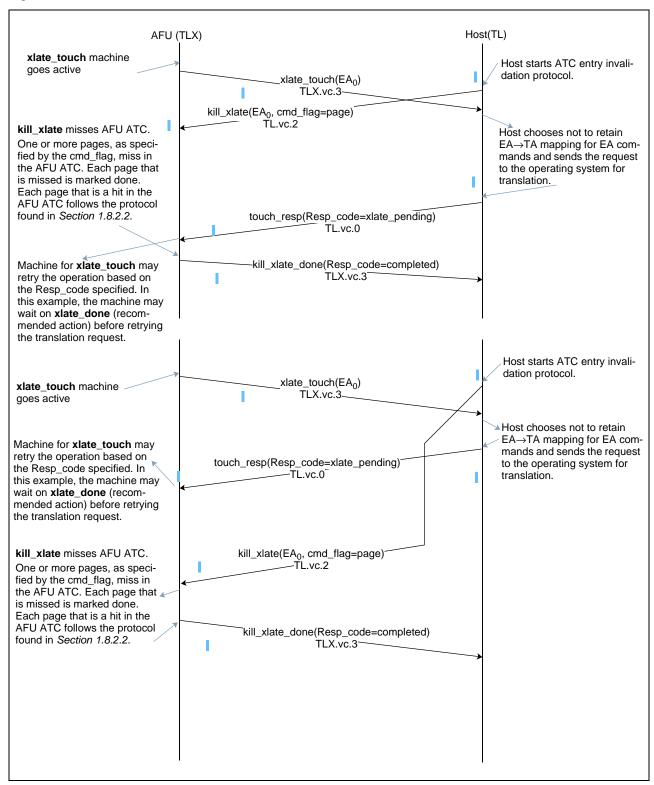

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub> A.6 AFU DMA partial write; non-posted, 8 bytes  A.7 AFU Partial read with no intent to cache hits device co-located AFU <sub>M1</sub> A.8 Translate touch (xlate_touch, ta_req)                                                                           |                          |

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub> A.6 AFU DMA partial write; non-posted, 8 bytes  A.7 AFU Partial read with no intent to cache hits device co-located AFU <sub>M1</sub> A.8 Translate touch (xlate_touch, ta_req)  A.9 Upgrade state                                                        |                          |

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub> A.6 AFU DMA partial write; non-posted, 8 bytes  A.7 AFU Partial read with no intent to cache hits device co-located AFU <sub>M1</sub> A.8 Translate touch (xlate_touch, ta_req)                                                                           |                          |

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub> A.6 AFU DMA partial write; non-posted, 8 bytes  A.7 AFU Partial read with no intent to cache hits device co-located AFU <sub>M1</sub> A.8 Translate touch (xlate_touch, ta_req)  A.9 Upgrade state  A.10 Host tag locking transactions  A.11 Castout push |                          |

| Appendix A. AP (TLX) command transaction diagrams  A.1 AFU read with no intent to cache; 128 bytes  A.2 TLX read with no intent to cache hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.3 AFU DMA write; non-posted; 128 bytes  A.4 AFU DMA Write hits device co-located AFU <sub>C2</sub> and AFU <sub>M1</sub> A.5 AFU DMA Write hits device co-located AFU <sub>M1</sub> A.6 AFU DMA partial write; non-posted, 8 bytes  A.7 AFU Partial read with no intent to cache hits device co-located AFU <sub>M1</sub> A.8 Translate touch (xlate_touch, ta_req)  A.9 Upgrade state  A.10 Host tag locking transactions                    |                          |

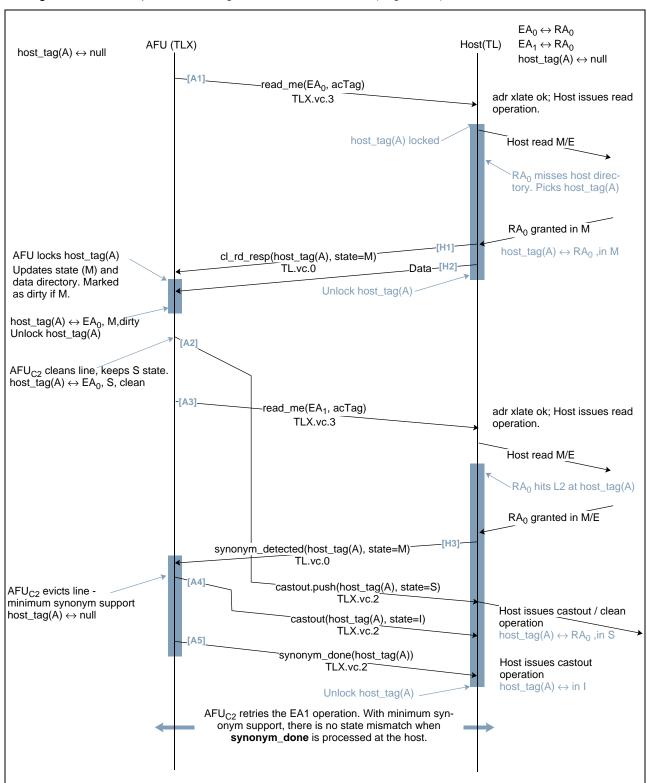

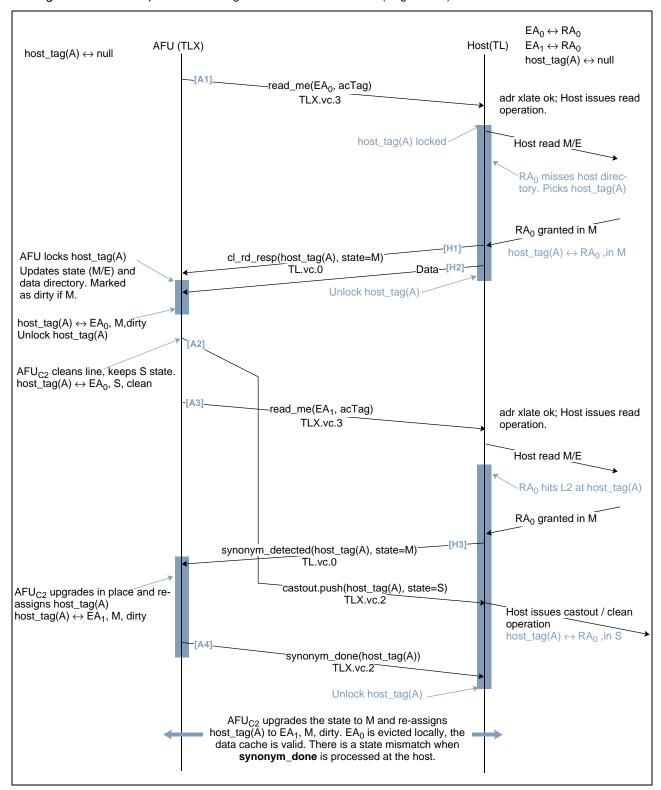

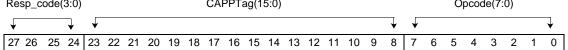

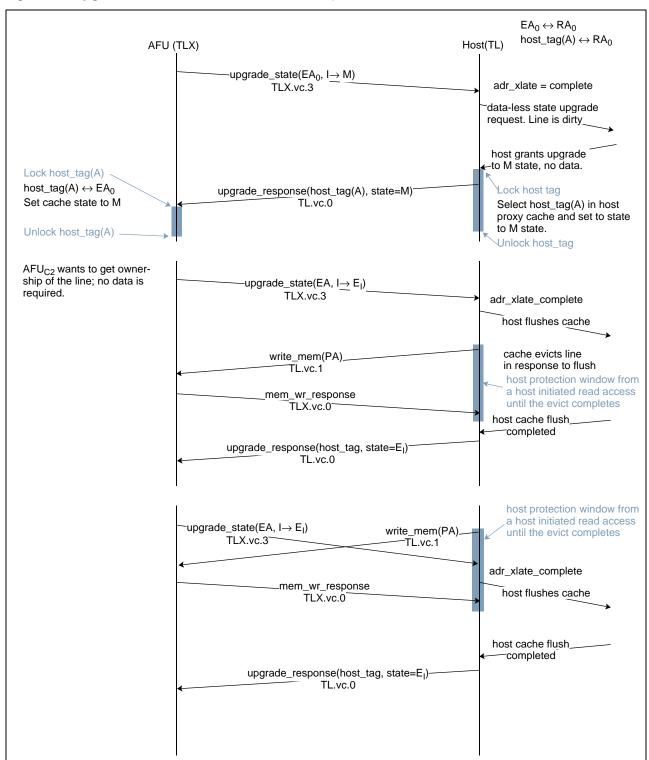

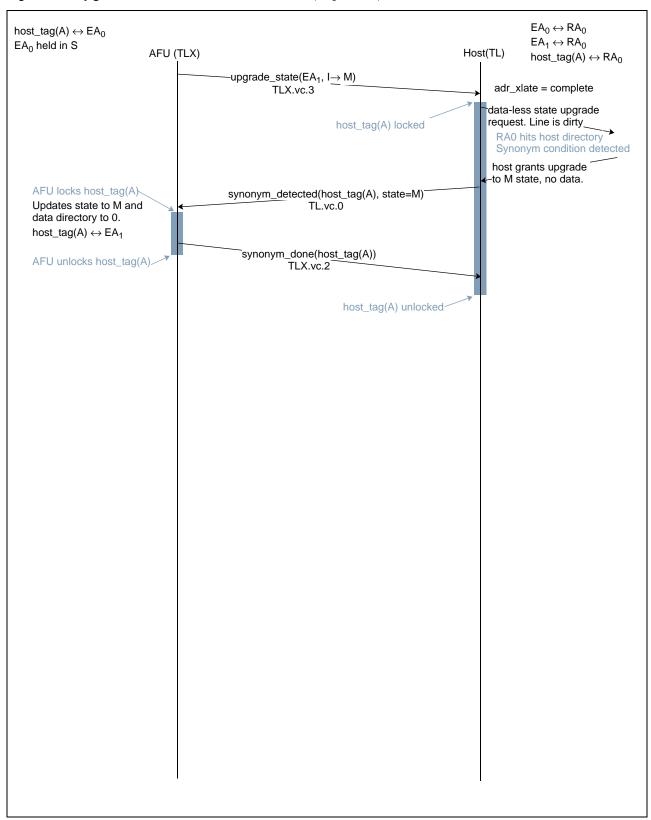

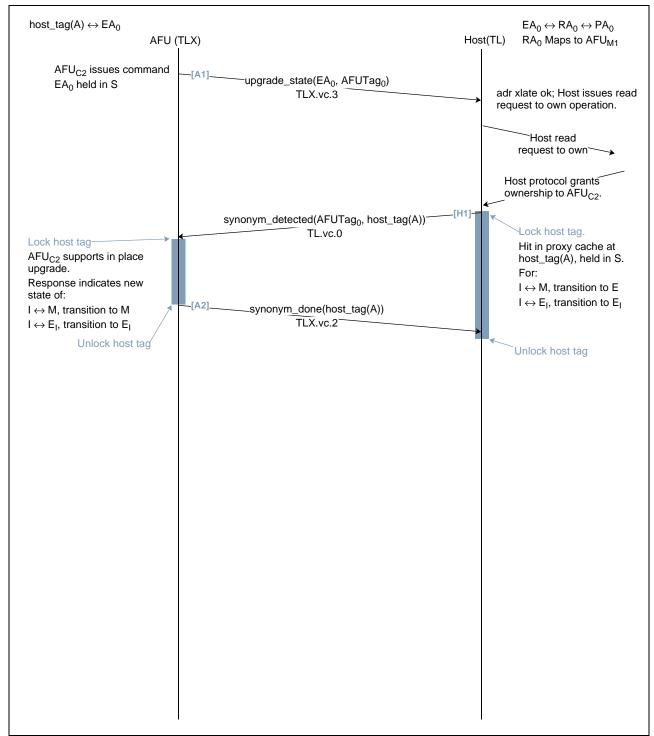

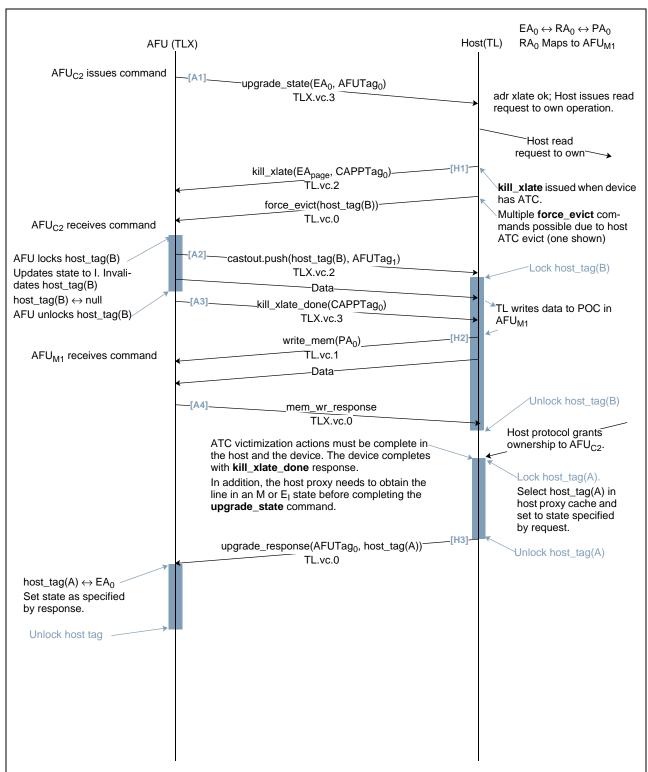

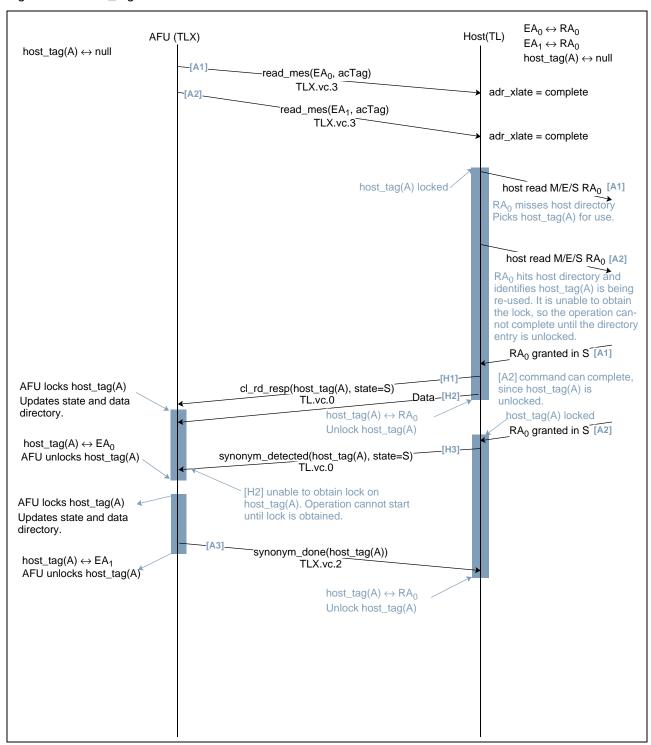

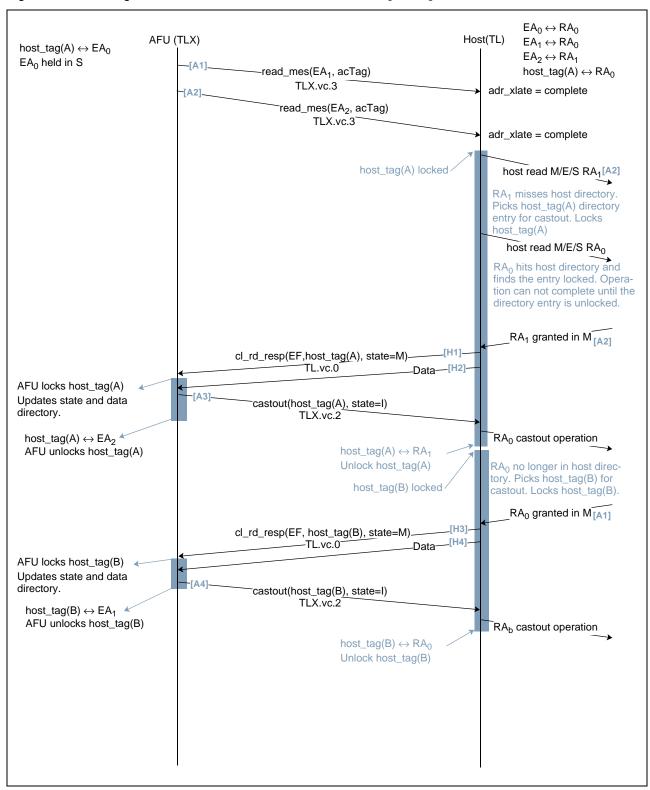

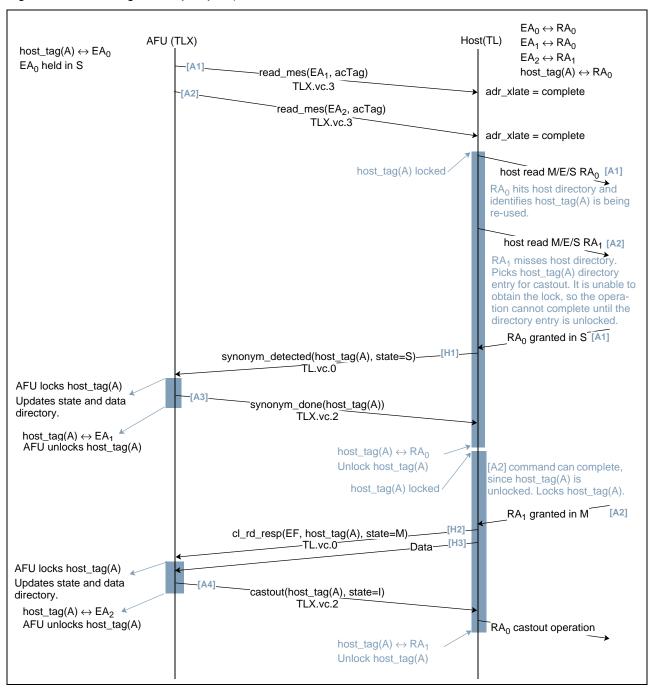

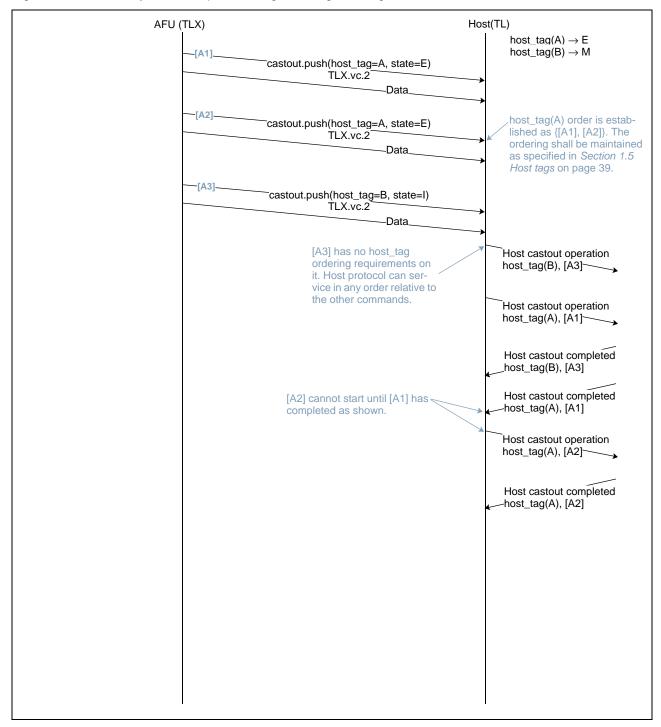

#### List of figures Figure 1. Big- and little-endian comparisons ......12 Figure 2. Example TLX and TL transaction diagram ......16 Figure 3. Figure 1-1. Figure 2-1. Figure 3-1. Figure 3-2. TL command flow from a service queue with a designated presync queue .......172 Figure 3-3. TLX command and response flow from the VC to the AFU protocol stack .......176 Figure 3-4. Figure 3-5. Figure 3-6. Figure A-1. Figure A-2. TLX **rd\_wnitc** hits AFU<sub>C2</sub> and AFU<sub>M1</sub> ......221 Figure A-3. Figure A-4. Figure A-5. Figure A-6. Figure A-7. Figure A-8. Figure A-9. Figure A-10. TLX upgrade\_state hits host cache and AFU<sub>M1</sub> ......232 Figure A-11. TLX **upgrade\_state** hits AFU<sub>C2</sub> and AFU<sub>M1</sub> ......233 Figure B-1. Figure B-2.

## List of tables

| Table 1.    | Architecture terms                                           | 11  |

|-------------|--------------------------------------------------------------|-----|

| Table 1-1.  | Cache state descriptions                                     | 32  |

| Table 1-2.  | Concurrent host proxy cache (L2) and L1 EA cache states (L1) | 33  |

| Table 1-3.  | L1 EA Cache state change request and notification            | 35  |

| Table 1-4.  | host_tag run-length-capability definition                    | 41  |

| Table 2-1.  | TL and TLX command operands                                  | 48  |

| Table 2-2.  | The Resp_code specification for xlate_done                   | 58  |

| Table 2-3.  | The Resp_code specification for intrp_rdy                    | 59  |

| Table 2-4.  | The cmd_flag specification for amo_rd                        | 63  |

| Table 2-5.  | The cmd_flag specification for amo_rw                        | 65  |

| Table 2-6.  | The cmd_flag specification for amo_w                         | 67  |

| Table 2-7.  | The cmd_flag specification for kill_xlate                    | 73  |

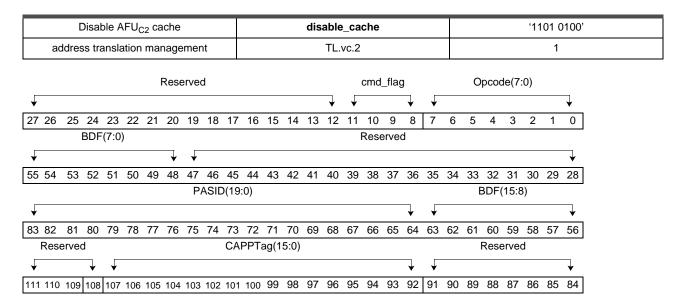

| Table 2-8.  | The cmd_flag specification for disable_cache                 | 75  |

| Table 2-9.  | The cmd_flag specification for enable_cache                  | 76  |

| Table 2-10. | The cmd_flag specification for disable_atc                   | 77  |

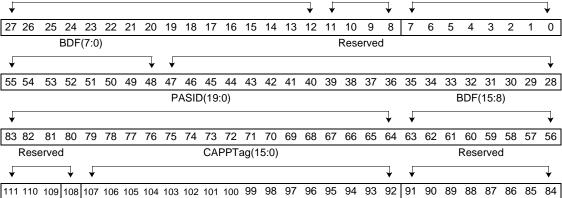

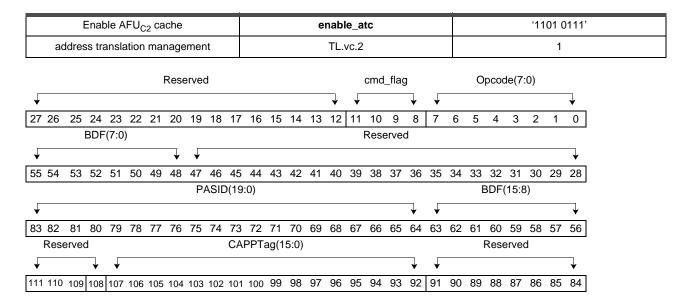

| Table 2-11. | The cmd_flag specification for enable_atc                    | 78  |

| Table 2-12. | The cmd_flag specification for amo_rd                        | 89  |

| Table 2-13. | The cmd_flag specification for amo_rw                        | 91  |

| Table 2-14. | The cmd_flag specification for amo_w                         | 93  |

| Table 2-15. | The command flag specification for castout                   | 96  |

| Table 2-16. | The cmd_flag specification for upgrade_state                 | 101 |

| Table 2-17. | The cmd_flag specification for xlate_touch (all forms)       | 106 |

| Table 2-18. | The cmd_flag specification for sync                          | 121 |

| Table 2-19. | The Resp_code specification for touch_resp                   | 123 |

| Table 2-20. | touch_resp Resp_code use by TLX command                      | 124 |

| Table 2-21. | synonym_detected formation and actions                       | 127 |

| Table 2-22. | The Resp_code specification for read_failed                  | 135 |

| Table 2-23. | read_failed Resp_code use by TLX command                     | 136 |

| Table 2-24. | The Resp_code specification of write_failed                  | 142 |

| Table 2-25. | write_failed Resp_code use by TLX command                    | 143 |

| Table 2-26. | The Resp_code specification for intrp_resp                   | 144 |

| Table 2-27. | intrp_resp Resp_code use by TLX command                      | 145 |

| Table 2-28. | The Resp_code specification for wake_host_resp               | 148 |

| Table 2-29. | The Resp_code specification for mem_rd_fail                  | 152 |

| Table 2-30. | mem_rd_fail Resp_code use by TL command                      | 153 |

| Table 2-31. | The Resp_code specification for mem_wr_fail                  | 155 |

| Table 2-32. | mem_wr_fail Resp_code use by TL command                      | 156 |

| Table 2-33. | The Resp_code specification for mem_cntl_done                | 158 |

| Table 2-34. | The Resp_code specification for kill_xlate_done                     | 159 |

|-------------|---------------------------------------------------------------------|-----|

| Table 2-35. | The Resp_code specification for cache_disabled                      | 160 |

| Table 2-36. | The Resp_code specification for cache_enabled                       | 161 |

| Table 2-37. | The Resp_code specification for atc_disabled                        | 162 |

| Table 2-38. | The Resp_code specification for atc_enabled                         | 162 |

| Table 3-1.  | VC maximum credit count specification                               | 165 |

| Table 3-2.  | DCP maximum credit count specification                              | 166 |

| Table 3-3.  | Summary VC and DCP assignments                                      | 166 |

| Table 3-4.  | Example sequence of 2 block writes and 2 flag writes                | 172 |

| Table 5-1.  | DL frame format showing CRC and "bad data flit" coverage            | 182 |

| Table 5-2.  | DL frame loading to illustrate data ordering                        | 186 |

| Table 6-1.  | Template capability definitions                                     | 190 |

| Table 6-2.  | Terms used in template capability specifications                    | 190 |

| Table 6-3.  | TLX receive/TL transmit template                                    | 191 |

| Table 6-4.  | TL receive/TLX transmit template                                    | 194 |

| Table 7-1.  | Error event specification                                           | 199 |

| Table 7-2.  | Cache state transition errors                                       | 208 |

| Table 8-1.  | Feature compliance requirement notation                             | 210 |

| Table 8-2.  | Profile specifications for TL commands                              | 211 |

| Table 8-3.  | Profile specifications for TLX commands                             | 211 |

| Table 8-4.  | Profile specifications for TL responses                             | 213 |

| Table 8-5.  | Profile specifications for TLX responses                            | 214 |

| Table 8-6.  | Profile specifications for TLX receive/TL transmit templates        | 215 |

| Table 8-7.  | Profile specifications for TL receive/TLX transmit templates        | 215 |

| Table 8-8.  | Profile specifications host operation modes                         | 216 |

| Table 8-9.  | Profile specifications supported page size                          | 217 |

| Table 8-10. | Profile specifications supported dLength by TLX                     | 217 |

| Table 8-11. | Profile specifications supported dLength by TL                      | 217 |

| Table 8-12. | Profile specifications support of endianness data format by the TL  | 217 |

| Table 8-13. | Profile specifications support of endianness data format by the TLX | 218 |

## **Revision log**

Each release of this document supersedes all previously released versions. The revision log lists all significant changes made to the document since its initial release. In the rest of the document, change bars in the margin indicate that the adjacent text was modified from the previous release of this document.

| Revision date | Description                                        |

|---------------|----------------------------------------------------|

| 16 June 2020  | Release of Approved OpenCAPI TL 4.0 specification. |

## About this document

This document provides the architectural specification of the OpenCAPI<sup>TM</sup> transaction layer (TL and TLX).

## **Architecture compliance terminology**

In architecture descriptions, certain terms carry meaning in addition to their normal use in English. The following terms are used within this architecture specification to describe the requirements an implementation must meet to be considered compliant.

Table 1. Architecture terms

| Term      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| invalid   | Used for multi-bit fields where the contents are not reliable. The field or bus shall not be examined for any functional or error checking actions.                                                                                                                                                                                                                                                                                                                                                                                                      |

| may       | An architectural option indicating that an implementation is allowed to have this behavior or characteristic.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| reserved  | With respect to a field of a register or bus:  A reserved field shall be set to 0 by an implementation.  A reserved field shall not be examined by an implementation.  With respect to a code point:  A reserved code point shall not be issued by a compliant implementation  A reserved code point shall cause a bounded undefined response (that is, it won't hang the system).  A reserved code point may be used in future revisions of the architecture. The architecture may specify that the use of a reserved code point is an error condition. |

| shall     | An architectural requirement indicating a required behavior or characteristic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| uncertain | Used for single-bit fields where the contents are not reliable. The field or bus shall not be examined for any functional or error checking actions.                                                                                                                                                                                                                                                                                                                                                                                                     |

| undefined | When the value of a field or a bus is undefined, the value may vary between implementations and may vary for a particular implementation for different actions. An implementation shall not examine a field when its value is undefined for functional purposes. However, the field may be checked for errors in those cases where an implementation includes error checking (that is, parity, ECC and so on)                                                                                                                                            |

## Conventions used in this specification

## Bit and byte numbering

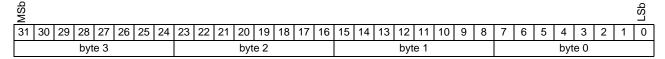

Throughout this document, little-endian notation is used, which means that bits and bytes are numbered in descending order from left to right.

Thus, in the description of a 4-byte field, bit 31 is the most significant bit (MSb) and bit 0 is the least significant bit (LSb). The corresponding byte numbering is also shown.

The big-endian and little-endian byte ordering are described in the *POWER ISA*, *version 3.0*, *Book I. Figure 1* compares big-endian and little-endian notation.

Figure 1. Big- and little-endian comparisons

| LE | 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------------------------|---|---|---|---|---|---|---|

|    | Bit numbering within a byte |   |   |   |   |   |   |   |

| BE | 0                           | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

4-byte field with character data shown

| LE       | 3 | 2 | 1 | 0 |

|----------|---|---|---|---|

| Content: | М | 1 | K | Е |

| BE       | 0 | 1 | 2 | 3 |

Illustrating the difference between little endian and big endian storing to memory of the 4-byte field shown to the left.

| Memory offset | LE stored | BE stored |  |

|---------------|-----------|-----------|--|

| 0             | Е         | М         |  |

| 1             | K         | I         |  |

| 2             | I         | К         |  |

| 3             | M         | Е         |  |

## Representation of numbers

The notation for bit encoding is as follows:

- Hexadecimal values are preceded by an x and enclosed in single quotation marks. For example x'0A00'. Bit numbering is little endian and, in this example, is 15 to 0.

- Binary values in sentences are shown in single quotation marks. For example '1010'. Bit numbering in is little endian and, in this example, is 3 to 0.

- <sup>n</sup>x means the replication of x, n times. That is, x is concatenated to itself n-1 times. <sup>n</sup>0 and <sup>n</sup>1 are special cases:

- <sup>n</sup>0 means a field of n bits with each bit equal to 0. For example, <sup>5</sup>0 is equivalent to '00000'.

- <sup>n</sup>1 means a field of n bits with each bit equal to 1. For example, <sup>5</sup>1 is equivalent to '11111'.

### **RTL** notation

RTL notations are used to specify the architectural transformation performed by the execution of a command.

| Notation     | Meaning                                                    |

|--------------|------------------------------------------------------------|

| $\leftarrow$ | Assignment.                                                |

|              | Concatenation.                                             |

| =, ≠         | Equal, not equal relations.                                |

| ≥, ≤         | Greater than or equal to, less than or equal to relations. |

| Notation     | Meaning                                                                                   |

|--------------|-------------------------------------------------------------------------------------------|

| >, <         | Greater than or less than relations.                                                      |

| +            | Two's complement addition.                                                                |

| -            | Two's complement subtraction, unary minus                                                 |

| <b>V</b>     | Bitwise logical OR                                                                        |

| ٨            | Bitwise logical AND                                                                       |

| $\oplus$     | Bitwise logical exclusive OR                                                              |

| Max(x,y)     | Returns x when $x \ge y$ ; otherwise returns y                                            |

| Min(x,y)     | Returns x when $x \le y$ ; otherwise returns y.                                           |

| {xy}         | All integer values from x through y.                                                      |

| $A = \{xy\}$ | Returns true when A is a member of the set of integer values in the range of x through y. |

## **Notes**

This document contains engineering and developer notes.

## **Engineering notes**

Engineering notes provide additional implementation details and recommendations not found elsewhere. The notes might include architectural compliance requirements. That is, the text might include *Architecture compliance terminology*. These notes should be read by all implementation and verification teams to ensure architectural compliance.

#### Engineering note

Lorem ipsum dolor sit amet, consectetur adipiscing elit. Proin cursus hendrerit enim, vel tempus nibh ornare ut. Quisque ac augue eu augue convallis hendrerit. Mauris iaculis viverra ipsum nec dapibus. Nunc at porta libero. Curabitur luctus ultrices augue non pulvinar. Vestibulum mattis non ipsum at venenatis. Suspendisse euismod, neque et suscipit luctus, odio metus semper lectus, quis volutpat est libero quis nunc. Vivamus rutrum mauris sed tristique malesuada. Vivamus at augue vitae nisl cursus feugiat. Pellentesque efficitur sed nisi in dapibus. Curabitur vestibulum cursus arcu, ut mattis nisl.

## **Developer notes**

Developer notes are used to document the reasoning and discussions that led to the current version of the architecture. These notes might also include recommended changes for future versions of the architecture, or warnings of approaches that have failed in the past. These notes should be read by verification teams and contributors to the architecture.

#### Developer note

Lorem ipsum dolor sit amet, consectetur adipiscing elit. Proin cursus hendrerit enim, vel tempus nibh ornare ut. Quisque ac augue eu augue convallis hendrerit. Mauris iaculis viverra ipsum nec dapibus. Nunc at porta libero. Curabitur luctus ultrices augue non pulvinar. Vestibulum mattis non ipsum at venenatis. Suspendisse euismod, neque et suscipit luctus, odio metus semper lectus, quis volutpat est libero quis nunc. Vivamus rutrum mauris sed tristique malesuada. Vivamus at augue vitae nisl cursus feugiat. Pellentesque efficitur sed nisi in dapibus. Curabitur vestibulum cursus arcu, ut mattis nisl.

## **Command flows and transaction diagrams**

## **Command flow diagrams**

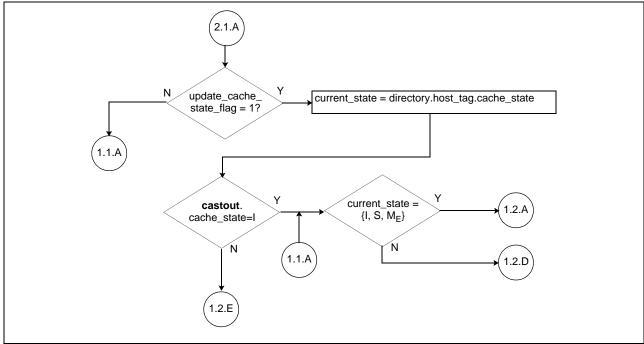

Command-flow diagrams show interactions within and across the different levels of the OpenCAPI protocol stack. Command flows use diamonds for decision blocks and rectangles for actions taken. Circles are used for on-page and off-page connectors and indicate a from-to direction based on the text content of the circle.

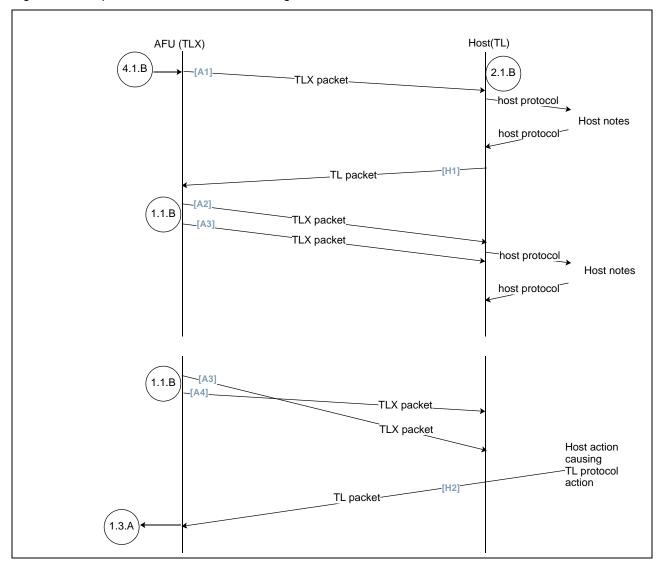

In *Figure 2*, a simple decision block with a state change and an off-page connector is shown. The text within the off-page connector has the format of "source page".destination page"."instance". The off-page connectors shown in the figure is on page 1 of the figure<sup>1</sup> and is connecting to page 2 of the figure. On page 2, identical off-page connectors can be found. The instance indication allows for multiple connections to be shown between two pages. Connector 2.1.A illustrates a connection from page 2 to page 1 of *Figure 2*. An off-page connector can also be used to "connect" two spots on the same page as illustrated by connector 1.1.A. The direction of the arrow, into or out of a connector, decision block, or assignment-action block, indicates the direction of the sequence within the flow diagram.

Figure 2. Command flow example

## **Transaction diagrams**

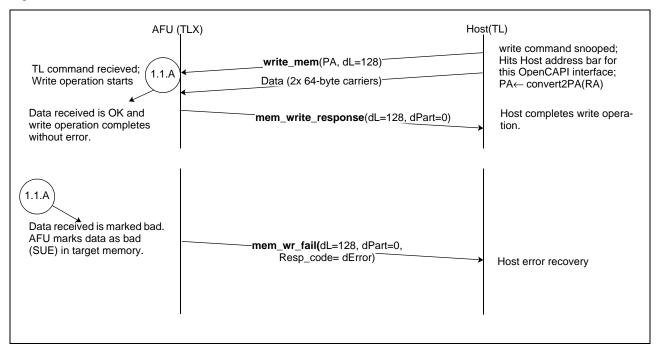

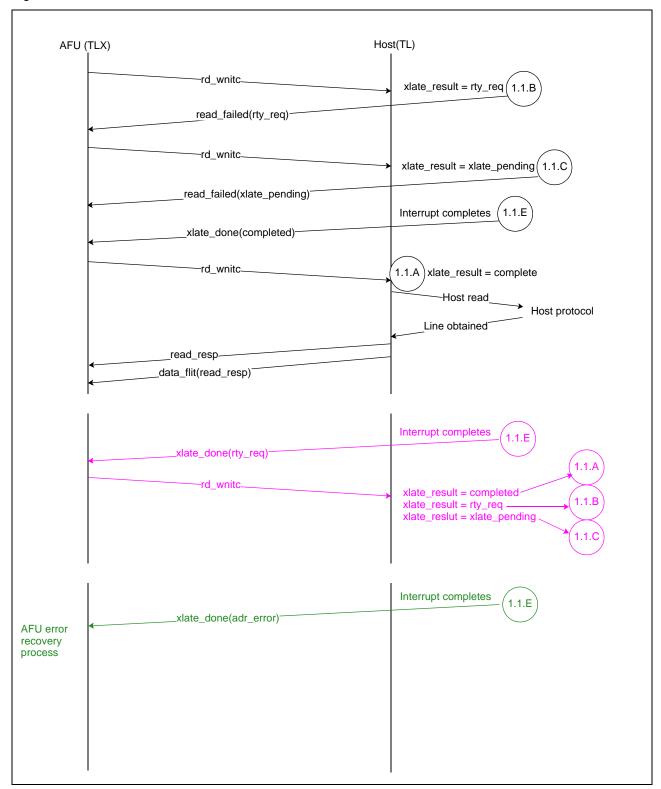

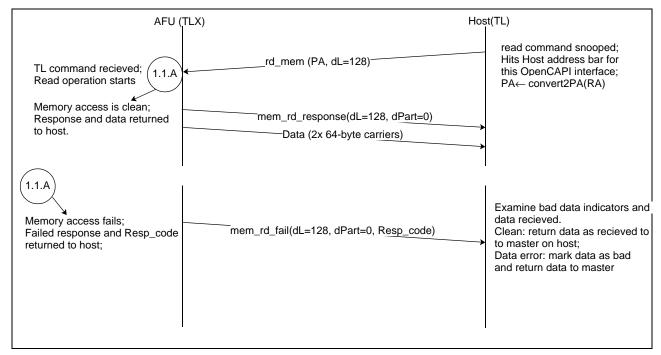

Transaction diagrams show the interaction between the TL and TLX layers and provide some illustrative notes for actions taken at the host protocol layer and the attached functional unit (AFU) protocol layer. In *Figure 3* on page 16, the diagram is broken into three vertical sections. From left to right, these are the AFU protocol layer notes, transactions between the TL and TLX layers, which are typically command and response packets, and the host protocol layer notes. Arrows indicate the direction in which the packet or action flows; for example, towards or away from the host (TL) layer.

<sup>1.</sup> All multi-page figures contain a "page n of y" notation in the figure description.

Circles are used for on-page and off-page connectors and indicate a from-to direction based on the text content of the circle. The text content is specified in the same manner for transaction diagrams as previously described for command flows. In addition to the specification of how connectors are used in command flows, in transaction diagrams, when a connector is used without an arrow, the transaction shown is one of multiple possible transaction outcomes. The use of this technique reduces the size of the transaction figure because the preceding set of transactions do not have to be repeated.

In *Figure 3*, connector 1.1.B illustrates an on-page connection without an arrow to indicate a different transaction out come. The prior events are assumed to have occurred when looking at the second instance of the 1.1.B connector. In the second case, one TLX packet has passed a previously issued TLX packet; this is something that can occur when two packets use different virtual channels. Connector 1.3.A shows an off-page connection to page 3, and connector 4.1.B shows an off-page connection from page 4.

Arrow numbering is included in transaction diagrams to simplify references to transactions. The form of the arrow references indicates the source of the transaction (AFU or Host) and the instance of the arrow. As seen in *Figure 3*, [A1] is the first arrow from the TLX packet transaction and [H1] is the first TL transaction.

A break in the vertical lines indicates where a new transaction illustration starts or ends.

Figure 3. Example TLX and TL transaction diagram

## **Terms**

The following terms are used in this document.

| {EA, address context}     | A short hand notation to indicate an EA and address context pair.     Used when specifying an entry in an AFU L1 directory     Use in discussions about address translation from EA to either an RA or PA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| acLookUp(acTag)           | <ul> <li>This is a function call used in command flows and transaction diagrams. It converts an acTag found in a TLX command packet into the address context (ac) used by the host's platform architecture to authenticate and provide the function requested by the TLX command.</li> <li>The result of an acLookUp provides the error state of the address context provided. The state is shown as addressContext.state in the flows. The states are: <ol> <li>Good. The address context provided is valid.</li> <li>Invalid acTag. The acTag entry in the acTag table is not valid, or the acTag is specified outside the acTag table range. See <i>Table 7-1</i> on page 199.</li> <li>Invalid address context. The BDF and PASID associated with the acTag are invalid. The address context returned by the look up is not valid. See <i>Table 7-1</i> on page 199.</li> </ol> </li> <li>The function description is host specific.</li> </ul> |  |  |  |  |

| ACK                       | Acknowledgment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| address context           | (ac or addressContext). Address context is the information associated with a particular BDF and PASID pair. The association is formed by actions specified by the host's platform architecture. For TLX commands, the acTag and the acTag table provide the BDF and PASID. See Section 4 The acTag table on page 180 for additional details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| address context space     | A PASID paired with a BDF uniquely identifies the address space associated with a request. In OpenCAPI, a request is a TLX command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| address tenure            | In a split transaction bus protocol, the commands and addresses are sent on the bus by the master before any data that might be associated with the transaction is moved. After the address tenure is completed, the status of the completion is examined. The data, if any is specified, is sent conditionally based on the status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| AFU                       | Attached functional unit. Architecturally, AFU refers to an end point unit or resource. Communication from the processor to the AFU goes through a protocol stack, transaction layer (TL), data link layer (DL), and physical medium layer (PHY). Command and data packets at the AFU interface are specified by the AFU command/data interface, which is the interface between the AFU protocol stack and the AFU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| AFU protocol              | AFU protocol layer. This layer currently consists of:  • AFU <sub>C</sub> protocol layer  • AFU <sub>M</sub> protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| AFU <sub>C</sub>          | A processing element that is able to generate and receive commands to obtain data either in a cached state (using an attached L1), or in a checked-out (non-cached) state. It uses the AFU command/data interface to communicate with the AFU <sub>C</sub> protocol stack. All addressing to the AFU <sub>C</sub> protocol uses an EA only. It uses the AFU <sub>C</sub> protocol stack to send and receive commands through the TLX. If the device contains an EA L1 cache, commands may result in cache line installation (cacheable operations). Non caching operations also specified for this device (non-allocating cache operations). See <i>AFU type on page 28</i> for the different sub-types of an AFU <sub>C</sub> .                                                                                                                                                                                                                    |  |  |  |  |

| AFU <sub>C</sub> protocol | $AFU_C$ protocol layer. This protocol specifies the sequences on the AFU command/data interface and the OpenCAPI packet interface (TLX boundary) for an $AFU_C$ -defined AFU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| AFU <sub>M</sub>          | A processing element that receives commands to either provide or receive data. This element is a memory storage device and may be mapped to the system's memory address range.  The attributes of the memory held by an AFU <sub>M</sub> are managed by the operating system. It uses the AFU interface to communicate with the AFU <sub>M</sub> protocol stack. All addressing to the AF uses a PA only.  See AFU type on page 28 for the different subtypes of an AFU <sub>M</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| AFU <sub>M</sub> protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AFU <sub>M</sub> protocol layer. This protocol specifies the sequences on the AFU command/data interface and the OpenCAPI packet interface (TLX boundary) for an AFU <sub>M</sub> -defined AFU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| alias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>When address translation from one address type to another results in a many to one mapping, the set of addresses that map into the single address are referred to as alias of each other.</li> <li>During address translation, an alias is formed when two different addresses translate into the same address. For example: <ul> <li>Two or more physical addresses (PA) of an OpenCAPI device map to the same host real address (RA).</li> <li>Two or more host RA map to a single attached OpenCAPI device's physical address.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Allocate command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Class of commands on the AFU command interface that indicates the allocation of a cache line. That is, a read operation that results in a cache line installed in the AFU L1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| АМО                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Atomic memory operation. This operation performs an atomic update to a naturally aligned memory location. In some cases, this type of operation returns the original value of the memory location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

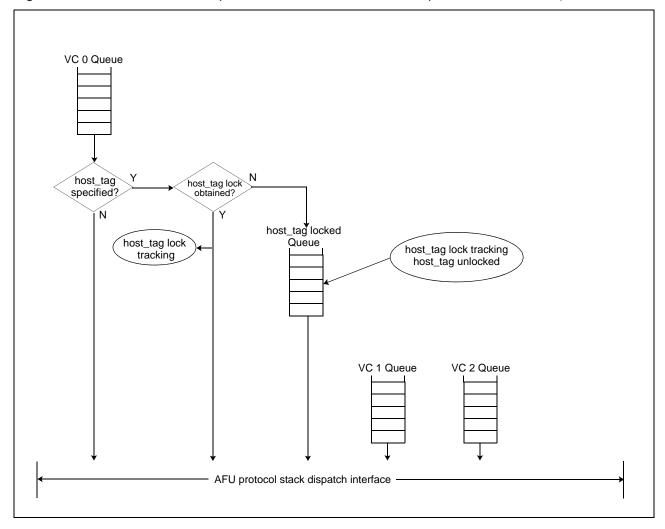

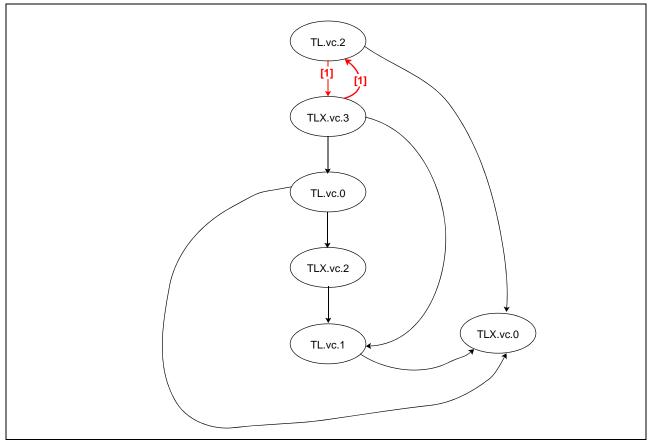

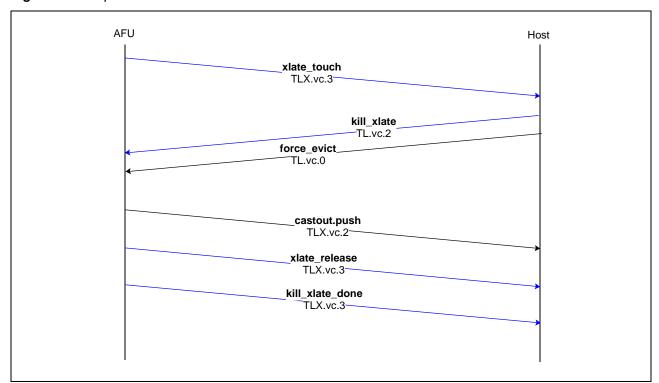

| AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Attached processor. Synonymous with AFU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |