# **OpenCAPI Data Link Layer (DL 3.0/3.1/4.0) Architecture Specification**

Version 2.0 9 July 2020

# Approved

Approved for Distribution to OpenCAPI Members Approved for Distribution to Non-Members for Learning Purposes Only

### OpenCAPI Data Link Layer (DL 3.0/3.1/4.0) Architecture

OpenCAPI DL Architecture Specification Work Group OpenCAPI Consortium

Version 2.0 (9 July 2020)

Copyright © OpenCAPI Consortium 2019, 2020

Use of this document is controlled by the OpenCAPI Consortium License Agreement, which is available at <u>https://opencapi.org/license/</u>.

All capitalized terms in the following text have the meanings assigned to them in the OpenCAPI Intellectual Property Rights Policy (the "OpenCAPI IPR Policy"). The full Policy may be found at the OpenCAPI Consortium website.

THE SPECIFICATION IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY, COMPLETENESS AND NONINFRINGEMENT OF THIRD PARTY RIGHTS. IN NO EVENT SHALL LICENSOR, ITS MEMBERS OR ITS CONTRIBUTORS BE LIABLE FOR ANY CLAIM, OR ANY DIRECT, SPECIAL, INDIRECT OR CONSEQUENTIAL DAMAGES, OR ANY DAMAGES WHATSOEVER RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, ARISING OUT OF OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THE SPECIFICATION.

OpenCAPI and the OpenCAPI logo design are trademarks of the OpenCAPI Consortium.

Other company, product, and service names may be trademarks or service marks of others.

#### Abstract

This document provides the architectural specification of the OpenCAPI data link layer (DL and DLX). It is the work product of the OpenCAPI Consortium DL Architecture Specification Work Group.

This document is handled in compliance with the requirements outlined in the OpenCAPI Consortium Work Group (WG) process document. Comments, questions, etc. can be submitted to <u>membership@opencapi.org</u>.

# **Participants**

Lonny Lambrecht, IBM

Brian Allison, IBM, Chair Mike J Palmer, IBM

Sanjay Goyal, Microchip

# Contents

| List of figures                                                    | 7    |

|--------------------------------------------------------------------|------|

| List of tables                                                     | 8    |

| Revision log                                                       | 9    |

| About this document                                                | 10   |

| Architecture compliance terminology                                | . 10 |

| Conventions                                                        | . 10 |

| Bit and byte numbering                                             |      |

| Representation of numbers                                          |      |

| RTL notation                                                       |      |

| Notes                                                              |      |

| Engineering notes                                                  |      |

| Developer notes                                                    | . 13 |

| Terms                                                              | 14   |

| 1. Overview                                                        | 17   |

| 2. Link training                                                   | 18   |

| 2.1 PHY training                                                   | . 20 |

| 2.2 PHY initialization                                             | . 20 |

| 2.3 DL training sets                                               | . 20 |

| 2.4 Deskew markers                                                 | . 23 |

| 2.5 [Category DL 3.1] Alternative training step                    | . 24 |

| 2.6 Endpoint link speed discovery                                  | . 24 |

| 2.7 Degraded modes                                                 | . 26 |

| 2.8 Lane width detection and degraded mode flit transmission order | . 26 |

| 2.9 Lane (bus) reversal                                            | . 32 |

| 2.10 DL transmit configurations for link debug                     | . 33 |

| 3. TL flits                                                        | 34   |

| 4. DL content fields                                               | 35   |

| 4.1 CRC (63:28)                                                    | . 35 |

| 4.2 ACK count (27:23)                                              | . 36 |

| 4.3 [Category DL 3.1] Recal Info (22:21)                           | . 37 |

| 4.4 [Category DL 3.1] Reserved (20)                                | . 37 |

| 4.5 [Category DL 3.0/4.0] Reserved (22:20)                         | . 37 |

| 4.6 Data Stalled (19)                                              | . 37 |

| 4.7 Short Flit Next (18)                                           |      |

| 4.7.1 [Category DL 3.1] Selectable Idle Flit Size                  |      |

| 4.8 TL Template (17:12)                                            |      |

| 4.9 Bad Data Flit (11:4)                                           | . 38 |

|    | 4.10 Data Run Length (3:0)                                                | . 38 |

|----|---------------------------------------------------------------------------|------|

| 5  | DL-to-DL flits                                                            | 30   |

| J. | 5.1 DL idle flit                                                          |      |

|    | 5.1.1 CRC (63:28)                                                         |      |

|    | 5.1.2 ACK Count (27:23)                                                   |      |

|    | 5.1.3 [Category DL 3.1] Recal Info (22:21)                                |      |

|    | 5.1.4 [Category DL 3.1] Reserved (20)                                     |      |

|    | 5.1.5 [Category DL 3./4.0] Reserved (22:20)                               |      |

|    | 5.1.6 Data Stalled (19)                                                   |      |

|    | 5.1.7 Short Flit Next (18)                                                |      |

|    | 5.1.8 [Category DL 3.0/4.0] Reserved (17:8)                               |      |

|    | 5.1.9 [Category DL 3.1] Reserved (17:12)                                  |      |

|    | 5.1.10 [Category DL 3.1] Power Management Message (11:8)                  |      |

|    | 5.1.11 Stalled Data Run Length (7:4)                                      |      |

|    | 5.1.12 Data Run Length (3:0)                                              |      |

|    | 5.2 DL Replay Flit                                                        |      |

|    | 5.2.1 CRC (159:124)                                                       |      |

|    | 5.2.2 ACK Count (123:119)                                                 |      |

|    | 5.2.3 [Category DL 3.0/4.0] Reserved (118:117)                            |      |

|    | 5.2.4 [Category DL 3.1] Recal Info (118:117)                              |      |

|    | 5.2.5 NACK (116)                                                          | . 44 |

|    | 5.2.6 Data Stalled (115)                                                  | . 44 |

|    | 5.2.7 Short Flit Next (114)                                               | . 44 |

|    | 5.2.8 Reserved (113:112)                                                  | . 44 |

|    | 5.2.9 Link Errors (111:104)                                               |      |

|    | 5.2.10 Previous Command Run Length (103:100)                              |      |

|    | 5.2.11 Data Run Length (99:96)                                            |      |

|    | 5.2.12 [Category DL 3.0/4.0] Starting Sequence Number (95:80)             |      |

|    | 5.2.13 [Category DL 3.0/4.0] Acknowledge Sequence Number (79:64)          |      |

|    | 5.2.14 [Category DL 3.1] Power Management Message (95:92)                 |      |

|    | 5.2.15 [Category DL 3.1] Starting Sequence Number (91:80)                 |      |

|    | 5.2.16 [Category DL 3.1] Reserved (79:76)                                 |      |

|    | 5.2.17 [Category DL 3.1] Acknowledge Sequence Number (75:64)              |      |

|    | 5.2.18 DL Link Information (63:0)                                         |      |

|    | 5.3 Other Run Lengths                                                     | . 45 |

| 6. | Flit flow diagrams                                                        | 46   |

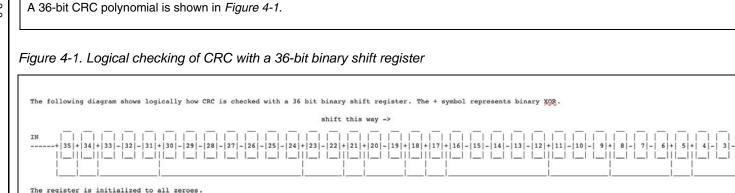

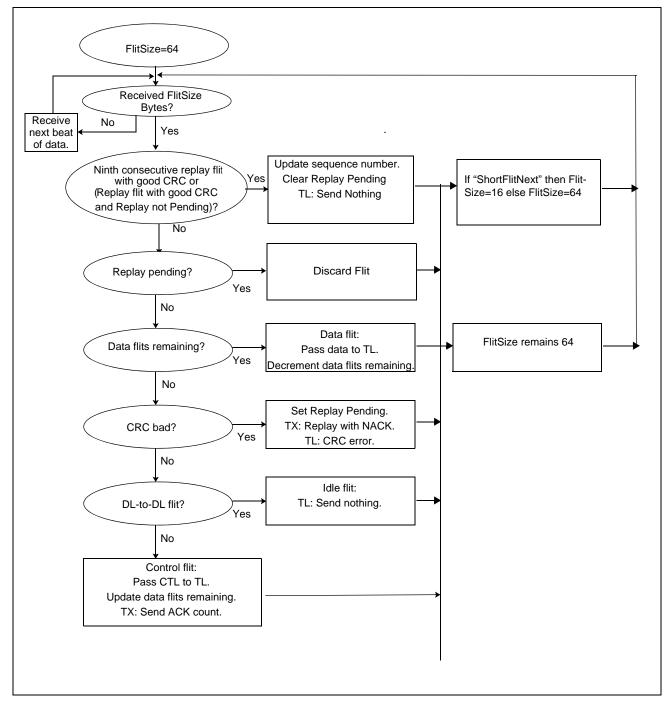

|    | 6.1 Receive flow                                                          | . 46 |

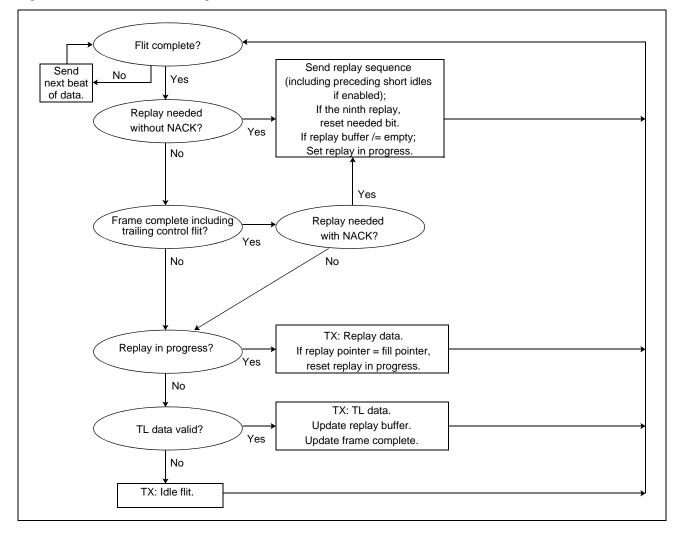

|    | 6.2 Transmit flow                                                         | . 47 |

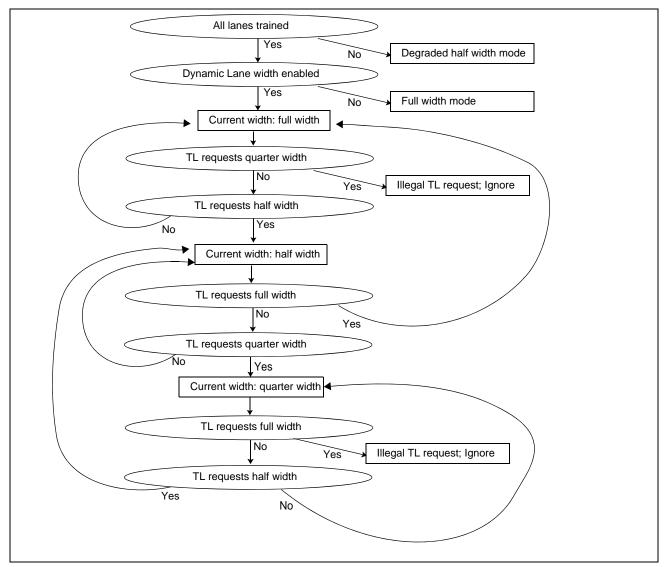

| 7  | [Category DL 3.1] Dynamic lane power down                                 | /18  |

| 1. |                                                                           |      |

|    | 7.1 Example 1: Lane width increase from ×4 half-width to ×8 full-width    |      |

|    | 7.2 Example 2: Lane width decrease from ×4 half-width to ×2 quarter-width |      |

|    | 7.3 Recalibration                                                         | . 50 |

| 8. | OpenCAPI data link layer versions                                         | 52   |

| 9. | Replay buffer                                                             | 54   |

|    | 9.1 Replay buffer sizing                                                  |      |

|    | o. Thoplay ballor sizing                                                  | . 54 |

| 9.2 Control pointers          | 55   |

|-------------------------------|------|

| 10. Encoding and scrambling   | . 56 |

| 10.1 Encoding                 | 56   |

| 10.2 Error detection per lane |      |

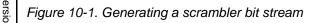

| 10.3 Scrambling               | 56   |

# List of figures

| Figure 1.    | Big- and little-endian comparisons                          | 11 |

|--------------|-------------------------------------------------------------|----|

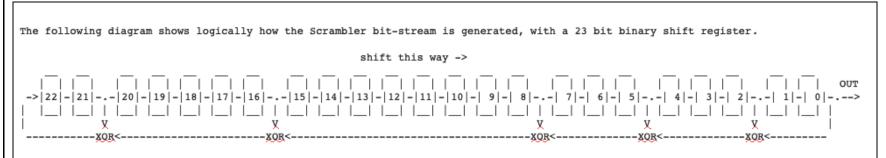

| Figure 1-1.  | OpenCAPI stack                                              | 17 |

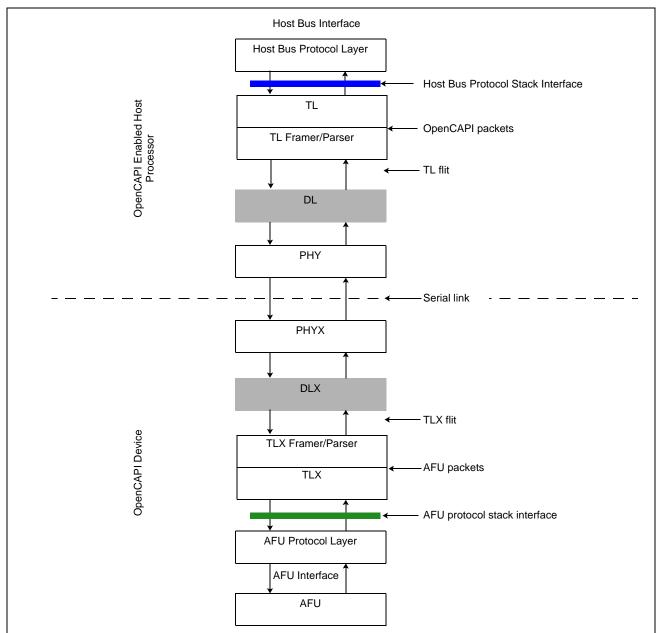

| Figure 2-1.  | Training exchange between the host and endpoint             | 18 |

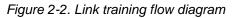

| Figure 2-2.  | Link training flow diagram                                  | 19 |

| Figure 2-3.  | Faster pattern A                                            | 25 |

| Figure 2-4.  | Slower pattern A                                            | 25 |

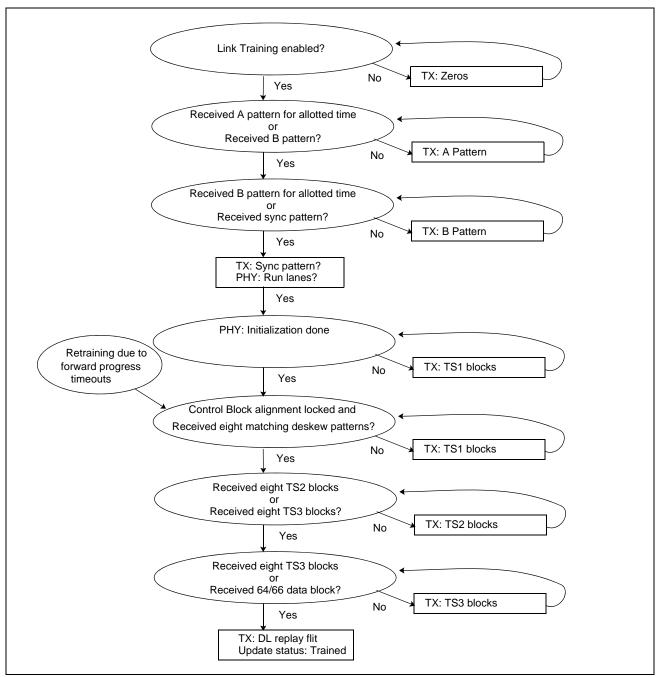

| Figure 4-1.  | Logical checking of CRC with a 36-bit binary shift register | 36 |

| Figure 6-1.  | Receive flit flow diagram                                   | 46 |

| Figure 6-2.  | Transmit flit flow diagram                                  | 47 |

| Figure 7-1.  | [Category DL 3.1] Dynamic Lane width states                 | 48 |

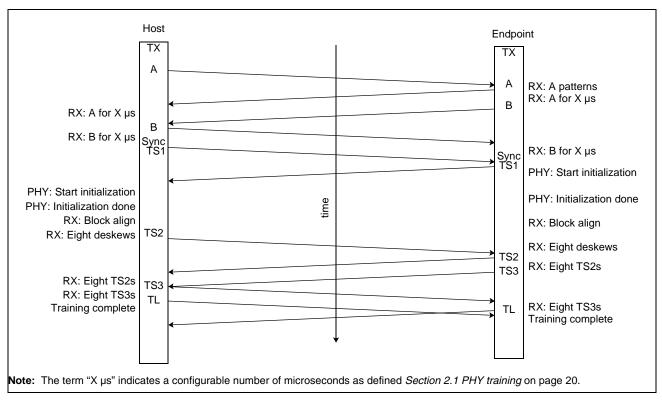

| Figure 10-1. | Generating a scrambler bit stream                           | 57 |

#### List of tables Table 1. Table 2-1. Table 2-2. Table 2-3. Table 2-4. Table 2-5. Table 2-6. Table 2-7. Table 2-8. Table 2-9. Table 2-10. Table 2-11. Table 2-12. Flit bytes to lane multiplexing on full-width mode (×8) for versions 3, 4, 5, 6, 8, 9, and 10 .... 29 Table 2-13. Flit bytes to lane multiplexing on half-width degraded outside lanes ( $\times$ 8), half-width degraded lanes for power management ( $\times$ 8), or full-width mode ( $\times$ 40L) for versions 3, 4, 5, 6, 8, 9, and 10 ......29 Flit bytes to lane multiplexing on half-width degraded inside lanes (×8) Table 2-14. Flit bytes to lane multiplexing on quarter-width for power management (×2), half-width degraded Table 2-15. outside lanes (×40L), or half-width for power management (×40L) for versions 8, 9, 10 ..... 30 Table 2-16. Flit bytes to lane multiplexing on half-width degraded inside lanes (×40L) Flit bytes to lane multiplexing on half-width degraded outside lanes, store and forward, Table 2-17. Flit bytes to lane multiplexing on half-width degraded inside lanes, store and forward, Table 2-18. Table 2-19. Table 2-20. Table 2-21. Table 4-1. Table 4-2. Table 4-3. Table 5-1. Table 5-2. Table 5-3. Table 5-4. Table 5-5. Table 8-1. Data link layer version numbers ......52 Table 8-2. Version number interoperability ......53 Table 8-3. Version number compliance ......53

Table 9-1.

# **Revision log**

Each release of this document supersedes all previously released versions. The change history log lists all significant changes made to the document since its initial release. The use of change bars and mark up notation may be included and are noted in the revision log.

| Revision date   | Summary of changes                                                                                                                                            |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9 July 2020     | <ul> <li>Version 2.0.</li> <li>Revised Section 2.6 Endpoint link speed discovery on page 24.</li> <li>Revised Section 5.1 DL idle flit on page 39.</li> </ul> |

| 8 July 2019     | Initial version 2.0 of the OpenCAPI Data Link Layer (DL 3.0/3.1/4.0) Architecture Specification in the OpenCAPI Consortium template.                          |

| 6 December 2019 | Initial version 2.0 release with the latest updates and book creation.                                                                                        |

# About this document

This preface contains some general format information (for example, headings) and document conventions.

### Architecture compliance terminology

In architecture descriptions, certain terms carry meaning in addition to their normal use in English. The following terms are used within this architecture specification to describe the requirements an implementation must meet to be considered compliant.

Table 1. Architecture terms

| Term      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| invalid   | Used for multi-bit fields where the contents are not reliable. The field or bus shall not be examined for any functional or error checking actions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| may       | An architectural option indicating that an implementation is allowed to have this behavior or characteristic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| reserved  | <ul> <li>With respect to a field of a register or bus: <ul> <li>A reserved field shall be set to 0 by an implementation.</li> <li>A reserved field shall not be examined by an implementation.</li> </ul> </li> <li>With respect to a code point: <ul> <li>A reserved code point shall not be issued by a compliant implementation</li> <li>A reserved code point shall not be issued by a compliant implementation</li> <li>A reserved code point shall cause a bounded undefined response (that is, it won't hang the system).</li> <li>A reserved code point may be used in future revisions of the architecture. The architecture may specify that the use of a reserved code point is an error condition.</li> </ul> </li> </ul> |

| shall     | An architectural requirement indicating a required behavior or characteristic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| uncertain | Used for single-bit fields where the contents are not reliable. The field or bus shall not be examined for any functional or error checking actions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| undefined | When the value of a field or a bus is undefined, the value may vary between implementations and may vary for a particular implementation for different actions. An implementation shall not examine a field when its value is undefined for functional purposes. However, the field may be checked for errors in those cases where an implementation includes error checking (that is, parity, ECC and so on).                                                                                                                                                                                                                                                                                                                        |

### Conventions

The OpenCAPI Consortium documentation uses several typesetting conventions.

### Bit and byte numbering

Throughout this document, little-endian notation is used, which means that bits and bytes are numbered in descending order from left to right.

Thus, in the description of a 4-byte field, bit 31 is the most significant bit (MSb) and bit 0 is the least significant bit (LSb). The corresponding byte numbering is also shown.

| MSb |        |    |    |        |    |    |    |        |    |    |    |    |        |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | LSb |

|-----|--------|----|----|--------|----|----|----|--------|----|----|----|----|--------|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----|

| 31  | 30     | 29 | 28 | 27     | 26 | 25 | 24 | 23     | 22 | 21 | 20 | 19 | 18     | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|     | byte 3 |    |    | byte 2 |    |    |    | byte 1 |    |    |    |    | byte 0 |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |     |

Big-endian and little-endian byte ordering are shown in *Figure 1* and described in the *POWER* <u>ISA</u>, version 3.0, Book I.

| Figure 1. | Big- and | little-endian | comparisons |

|-----------|----------|---------------|-------------|

|-----------|----------|---------------|-------------|

| <u>LE</u> | 7 | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|---|-----------------------------|---|---|---|---|---|---|--|

|           |   | Bit numbering within a byte |   |   |   |   |   |   |  |

| <u>BE</u> | 0 | 1                           | 2 | 3 | 4 | 5 | 6 | 7 |  |

4-byte field with character data shown

| LE       | 3 | 2 | 1 | 0 |

|----------|---|---|---|---|

| Content: | М | I | к | E |

| BE       | 0 | 1 | 2 | 3 |

Illustrating the difference between little endian and big endian storing to memory of the 4-byte field shown to the left.

| LE stored | BE stored   |            |

|-----------|-------------|------------|

| E         | М           |            |

| К         | I           |            |

| I         | К           |            |

| М         | E           |            |

|           | E<br>K<br>I | K I<br>I K |

### **Representation of numbers**

The notation for bit encoding is as follows:

- Hexadecimal values are preceded by x and enclosed in single quotation marks. For example x'0A00'. Bit numbering is little endian and, in this example, is 15 to 0.

- Binary values in sentences are shown in single quotation marks. For example '1010'. Bit numbering in is little endian and, in this example, is 3 to 0.

- <sup>n</sup>x means the replication of x, n times. That is, x is concatenated to itself n-1 times. <sup>n</sup>0 and <sup>n</sup>1 are special cases:

- <sup>n</sup>0 means a field of n bits with each bit equal to 0. For example, <sup>5</sup>0 is equivalent to '00000'.

- <sup>n</sup>1 means a field of n bits with each bit equal to 1. For example, <sup>5</sup>1 is equivalent to '11111'.

### **RTL** notation

<u>RTL</u> notations are used to specify the architectural transformation performed by execution of a command.

| Notation     | Meaning                                                                                   |

|--------------|-------------------------------------------------------------------------------------------|

| $\leftarrow$ | Assignment.                                                                               |

| ll           | Concatenation.                                                                            |

| =, ≠         | Equal, not equal relations.                                                               |

| ≥, ≤         | Greater than or equal to, less than or equal to relations.                                |

| +            | Two's complement addition.                                                                |

| -            | Two's complement subtraction, unary minus                                                 |

| $\checkmark$ | Bitwise logical OR                                                                        |

| ^            | Bitwise logical AND                                                                       |

| $\oplus$     | Bitwise logical exclusive OR                                                              |

| Max(x,y)     | Returns x when $x \ge y$ ; otherwise, returns y.                                          |

| Min(x,y)     | Returns x when $x \le y$ ; otherwise, returns y.                                          |

| {xy}         | All integer values from x through y.                                                      |

| $A = \{xy\}$ | Returns true when A is a member of the set of integer values in the range of x through y. |

### Notes

This section describes engineering, developer, and editor notes.

### **Engineering notes**

Engineering notes provide additional implementation details and recommendations not found elsewhere. The notes might include architectural compliance requirements. That is, the text might include *Architecture compliance terminology*. These notes should be read by all implementation and verification teams to ensure architectural compliance.

#### — Engineering note -

This is an example of an Engineering note. Lorem ipsum dolor sit amet, consectetur adipiscing elit. Proin cursus hendrerit enim, vel tempus nibh ornare ut. Quisque ac augue eu augue convallis hendrerit. Mauris iaculis viverra ipsum nec dapibus. Nunc at porta libero. Curabitur luctus ultrices augue non pulvinar. Vestibulum mattis non ipsum at venenatis. Suspendisse euismod, neque et suscipit luctus, odio metus semper lectus, quis volutpat est libero quis nunc. Vivamus rutrum mauris sed tristique malesuada. Vivamus at augue vitae nisl cursus feugiat.

#### **Developer notes**

Developer notes are used to document the reasoning and discussions that led to the current version of the architecture. These notes might also include recommended changes for future versions of the architecture, or warnings of approaches that have failed in the past. These notes should be read by verification teams and contributors to the architecture.

#### **Developer note**

This is an example of a Developer note. Lorem ipsum dolor sit amet, consectetur adipiscing elit. Proin cursus hendrerit enim, vel tempus nibh ornare ut. Quisque ac augue eu augue convallis hendrerit. Mauris iaculis viverra ipsum nec dapibus. Nunc at porta libero. Curabitur luctus ultrices augue non pulvinar. Vestibulum mattis non ipsum at venenatis. Suspendisse euismod, neque et suscipit luctus, odio metus semper lectus, quis volutpat est libero quis nunc.

# Terms

The following terms are used in this document.

| АСК          | Acknowledgment or acknowledge. A transmission that is sent as an affirmative response to a data transmission.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AFU          | Attached functional unit. Architecturally, this term refers to an endpoint unit or resource.<br>Communication from the processor to the AFU goes through a protocol stack, transac-<br>tion layer (TL), data link layer (DL), and physical medium layer (PHY). Command and<br>data packets at the AFU interface are specified by the AFU command/data interface,<br>which is the interface between the AFU protocol stack and the AFU. |  |  |  |  |

| AFU protocol | AFU protocol layer. This layer currently consists of:                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|              | AFU <sub>C</sub> protocol layer                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|              | AFU <sub>M</sub> protocol                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ASIC         | Application-specific integrated circuit                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CAPI         | Coherent Accelerator Processor Interface.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| CDR          | Clock and data recovery.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| CRC          | Cyclic redundancy check.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| DL           | OpenCAPI data link layer on the host processor.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| DLX          | OpenCAPI data link layer on the external OpenCAPI device                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ECC          | Error correction code. A code appended to a data block that can detect and correct bit errors within the block.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| FIR          | Fault Isolation Register. Register bits that show which piece of hardware failed.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Flit         | An acronym for flow control digits. Typically used in networking to specify the smaller pieces that a larger network layer packet is broken into. See <u>FLITs</u> .                                                                                                                                                                                                                                                                   |  |  |  |  |

|              | In OpenCAPI version 3.0, a flit is associated with the specification of a DL packet and is defined as a 64-byte unit of data. Control and data flits are specified.                                                                                                                                                                                                                                                                    |  |  |  |  |

| FPGA         | Field-programmable gate array.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Frame        | A control flit followed by 0 - 8 data flits.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Gbps         | Gigabits per second.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| GHz          | Gigahertz.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Inbound      | Specifies the direction from the attached OpenCAPI device towards the attached processor chip.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| LFSR         | Linear Feedback Shift Register.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| LP           | Low power.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LX           | Transaction layer external.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MMIO         | Memory-mapped input/output. Refers to the mapping of the address space required by an I/O device for Load or Store operations into the system's address space.                                                                                                                                                                                                                                                                         |  |  |  |  |

| NACK         | Negative acknowledgment.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| OCDE            | OpenCAPI device enable.                                                                                                                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OL              | Outside lane.                                                                                                                                                                                                                                                                                    |

| Outbound        | Specifies the direction from the processor chip to the attached OpenCAPI device.                                                                                                                                                                                                                 |

| Packet          | A TL or TLX unit of information. A command packet contains commands. A response packet contains response information. See the specification of these in the <i>OpenCAPI 3.0 Transaction Layer Specification</i> .                                                                                |

|                 | Data is transferred in address-aligned 64-byte packets.                                                                                                                                                                                                                                          |

| PHY             | The Host PHY layer interfaces to the DL and the network.                                                                                                                                                                                                                                         |

|                 | This is the bit stream level that specifies the electrical and optical transmission medium as well as the network interconnect topology.                                                                                                                                                         |

|                 | The current specification for the network is a point-to-point connection.                                                                                                                                                                                                                        |

| РНҮХ            | On the OpenCAPI device, the PHYX layer interfaces to the DLX and the network. This is the bit stream level that specifies the electrical and optical transmission medium as well as the network interconnect topology. The current specification for the network is a point-to-point connection. |

| PLL             | Phase-locked loop.                                                                                                                                                                                                                                                                               |

| P/N             | Positive/negative.                                                                                                                                                                                                                                                                               |

| PRBS23          | Pseudo-random binary sequence 23.                                                                                                                                                                                                                                                                |

| Reserved        | A field that might be defined at a later date. Senders are not required to drive zeros, although that is good practice. Receivers must ignore reserved fields except for the CRC.                                                                                                                |

| Response packet | The Host TL construct that contains response information to commands. Used for Host TL-to-Device TLX and Device TLX-to-Host TL communication.                                                                                                                                                    |

| RX              | Receiver.                                                                                                                                                                                                                                                                                        |

| SerDes          | Serializer/deserializer.                                                                                                                                                                                                                                                                         |

| TL              | OpenCAPI transaction layer found on the host processor.                                                                                                                                                                                                                                          |

|                 | Interfaces to the DL and the protocol layer. Responsible for command-packet formation and response-packet handling and formation. Ensures that the order of data sent to the DL matches the command and response packet order sent to the DL.                                                    |

|                 | Manages data flits from the DL, and associates the data with the command or response packet that was received prior to the arrival of the data. The command and response packets contain data descriptors that enable this association.                                                          |

|                 | Provides flow control.                                                                                                                                                                                                                                                                           |

|                 | Provides error handling and control.                                                                                                                                                                                                                                                             |

|                 | Manages virtual channels, virtual queues, and service queues associated with the virtual channels. Order is retained within virtual channels.                                                                                                                                                    |

| TLX | OpenCAPI transaction layer found on the OpenCAPI device.                                                                                                                                                                                                 |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     | Interfaces to the DLX and the protocol layer. Responsible for command-packet forma-<br>tion and response-packet handling and formation. Ensures that the order of data sent to<br>the DLX matches the command and response packet order sent to the DLX. |  |  |  |  |

|     | Manages data flits from the DLX, and associates the data with the command or response packet that was received prior to the arrival of the data. The command and response packets contain data descriptors that enable this association.                 |  |  |  |  |

|     | Provides flow control.                                                                                                                                                                                                                                   |  |  |  |  |

|     | Provides error handling and control.                                                                                                                                                                                                                     |  |  |  |  |

| TS1 | Training set 1.                                                                                                                                                                                                                                          |  |  |  |  |

| TS2 | Training set 2.                                                                                                                                                                                                                                          |  |  |  |  |

| TS3 | Training set 3.                                                                                                                                                                                                                                          |  |  |  |  |

| ТХ  | Transmitter.                                                                                                                                                                                                                                             |  |  |  |  |

### 1. Overview

The Open<u>CAPI</u><sup>™</sup> data link layer supports a serial data rate per lane that is consistent with the OIF CEI-28G-SR specification that connects any OpenCAPI-enabled processor, including the IBM® POWER® processor to an <u>FPGA</u>, <u>ASIC</u>, and other devices that contain an attached functional unit(s) [AFU(s)]. The base configuration uses eight lanes running at 25.78125 <u>Gbps</u> data rate. The supported <u>SerDes</u> rates are defined in *Table 2-7 Planned revisions and supported speeds* on page 26.

The data link layer that is implemented on the host is referred to as the <u>DL</u>. The data link layer that is implemented on the OpenCAPI device is referred to as the <u>DLX</u>. *Figure 1-1* shows where the DL and DLX fit in the OpenCAPI protocol layers. Any future references to DL apply to DL and the DLX.

Figure 1-1. OpenCAPI stack

# 2. Link training

The endpoint shall be held in reset by an out-of-band OpenCAPI Device Enable (OCDE) signal. After the OCDE signal is enabled (active high), link training begins. The definition of the OCDE implementation is found in a host's platform architecture specification.

The link training is broken into three parts: <u>PHY</u> training, PHY initialization, and <u>DL</u> training. *Figure 2-1* illustrates the exchange of training steps. The left side is a host processor; the right side is an attached OpenCAPI device endpoint. The information that is inside the boxes is what the transmitters are sending.

Figure 2-1. Training exchange between the host and endpoint

Figure 2-2 on page 19 provides a training flow diagram for each side of the link.

### 2.1 PHY training

When training is enabled, a slow-speed, non-scrambled signal shall be sent to reliably communicate across the link. All training shall be done on a per-lane basis. The first pattern transmitted shall be an A pattern, which is a repeating pattern of x'FF00'. This pattern mimics a slow-speed clock, and shall be transmitted until the same pattern is received. Detecting the pattern shall be programmable to search for 4, 6, or 7 consecutive one values followed by the same number of zero values. The bits around the transition are not reliable and are ignored. For example, "1111----0000----" for the 4 consecutive case, where "-" signifies a don't care. After receiving training pattern A for a programmable amount of time (1 µs - 16 ms), the lane switches to sending a B pattern. The B pattern is an A pattern with a pattern of x'FFF0000' inserted after every 30 - 48, x'FF00' patterns. The receipt of an inverted B pattern adjusts the receiver polarity (P/N swap). After receiving the B pattern for the allotted time (the same time requirement as an A pattern), the transmitter of the lane shall send a sync pattern, x'FF0000FF', followed by the first DL training set. The A, B, and sync patterns are all non-scrambled and do not have any encoding on them. Again, the bits around the transition are not reliable and are ignored for the B pattern and the sync pattern.

#### Engineering note -

Patterns in this section are transmitted from left to right. For example, Pattern A of x'FF00' is sent down the physical wire as '1111 1111 0000 0000'.

*Table 2-1* summarizes the DL PHY training patterns.

| Name         | TX pattern                                         | Frequency | Purpose                                      |

|--------------|----------------------------------------------------|-----------|----------------------------------------------|

| A pattern    | x'FF00'                                            | Repeating | Device detection due to resetting of a link. |

| B pattern    | x'FFFF0000' followed by 30 - 48 repeats of x'FF00' | Repeating | Lane polarity (P/N swap).                    |

| Sync pattern | x'FF0000FF'                                        | Once      | Start RX PHY initialization.                 |

Table 2-1. PHY training patterns

### 2.2 PHY initialization

When receiving the sync pattern on at least two lanes, the DL shall tell the PHY that it is about to receive random data by way of the "run lane" signal. It then waits for the "initialization done" signal from the PHY. Upon receiving the "run lane" signal, the PHY re-locks the clock data recovery (CDR), centers the eye, and obtains the high-speed bit lock. The DL ignores received data until PHY initialization is complete.

### 2.3 DL training sets

While the PHY is initializing and the DL is training, blocks that are associated with patterns <u>TS</u>1, TS2, TS3, and deskew are 64/66 encoded and scrambled (for more information, see *Section 10 Encoding and scrambling* on page 56). A block is a contiguous set of 64 bits following the sync header.

During PHY initialization, the DL sends control blocks with a TS1 pattern. After the PHY indicates that initialization completes, the RX searches for control block alignment and the receipt of eight deskew patterns with identical configuration information. When the receiver achieves block alignment and consistent deskew information (previously described eight deskew patterns with identical configuration information), the transmitter for this lane switches to sending TS2 blocks with valid receive lane information. After receiving eight TS2 blocks or eight TS3 blocks, it switches to sending TS3 blocks. After receiving eight TS3 blocks or a 64/66 data sync

#### Approved

header, the DL sends a minimum of nine DL-to-DL replay <u>flits</u> to sync up the sequence numbers, followed by <u>TL</u> data or DL-to-DL idle flits. *Table 2-2* describes the DL training sets. *Table 2-3* describes the DL3.0 TS2 and TS3 good lanes bit definitions, and *Table 2-4* on page 22 describes the DL 3.1/4.0 TS2 and TS3 good lanes bit definitions.

#### Table 2-2. DL training sets

| Name                 | Bytes            |                  |                  |    |    |    |    | Dumana |                                                                                                                                                        |  |

|----------------------|------------------|------------------|------------------|----|----|----|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                 | 7                | 6                | 5                | 4  | 3  | 2  | 1  | 0      | Purpose                                                                                                                                                |  |

| Training set 1 (TS1) | 4A               | 4A               | 4A               | 4A | 4A | 4A | 4A | 4B     | Block alignment and scrambler lock.                                                                                                                    |  |

| Training set 2 (TS2) | TS Byte<br>1     | TS Byte<br>0     | 45               | 45 | 45 | 45 | 45 | 4B     | Receipt of TS1 and valid lanes.                                                                                                                        |  |

| Training set 3 (TS3) | TS Byte<br>1     | TS Byte<br>0     | 41               | 41 | 41 | 41 | 41 | 4B     | Receipt of TS2 and valid lanes.                                                                                                                        |  |

| Deskew               | Deskew<br>Byte 2 | Deskew<br>Byte 1 | Deskew<br>Byte 0 | 1E | 1E | 1E | 1E | 4B     | Every 32 <sup>nd</sup> block during training sets.<br>Lane-to-lane deskew and configura-<br>tion. See <i>Section 2.4 Deskew markers</i><br>on page 23. |  |

1. Bytes 5:0 of the TS1 are used to lock the unscrambler's LFSR.

2. Bytes 7 and 6 of the TS2 and TS3 training sets, the good lane field defined in Tables 2-3 and 2-4, indicate the configured lane width and which lanes are receiving good data. Bits (7:4) are one hot, and bits (3:0) may have multiple sets.

#### - Engineering note

The bytes are sent in 0-1-2-3-4-5-6-7 order on a per lane basis.

Within each byte, the right most bit is sent first and the left most bit is sent last.

#### – Engineering note -

For example, Training set 1 (TS1) is sent down the physical wire as "1101\_0010\_0101\_0010\_0101\_0010\_0101\_0010\_0101\_0010\_0101\_0010\_0101\_0010".

| Bytes | Bits | Description of bytes 7 and 6      |  |  |  |

|-------|------|-----------------------------------|--|--|--|

| 0     | 7:0  | Reserved.                         |  |  |  |

| 1     | 7:6  | Reserved.                         |  |  |  |

|       | 5    | Capable lane width of $\times$ 8. |  |  |  |

|       | 4    | Reserved.                         |  |  |  |

|       | 3    | All odd lanes trained (7,5,3,1).  |  |  |  |

|       | 2    | All even lanes trained (6,4,2,0). |  |  |  |

|       | 1    | Lane 1 trained.                   |  |  |  |

|       | 0    | Lane 0 trained.                   |  |  |  |

[Category DL 3.1] Table 2-4 describes the TS2 and TS3 good lanes bit descriptions.

| Bytes | Bits | Description of bytes 7 and 6                                                                                                                                                        |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 7:0  | Reserved.                                                                                                                                                                           |

| 1     | 7:6  | Reserved.                                                                                                                                                                           |

|       | 5    | Capable lane width of ×8.                                                                                                                                                           |

|       | 4    | Capable lane width of ×4 OL.<br>Four outside lanes of a ×8 are capable in full function mode. Lanes may further degrade to ×2 and/or switch between ×2 and ×4 for power management. |

|       | 3    | All inside lanes of the capable width trained: [×8] 6,4,3,1 or [×4 OL] 5,2.                                                                                                         |

|       | 2    | All outside lanes of the capable width trained: [×8] 7,5,2,0 or [×4 OL] 7,0.                                                                                                        |

|       | 1    | Reserved.                                                                                                                                                                           |

|       | 0    | Reserved.                                                                                                                                                                           |

| Table 2-4. [Category DL 3.1/4.0] TS2 al | and TS3 good lanes bit definitions |

|-----------------------------------------|------------------------------------|

|-----------------------------------------|------------------------------------|

Examples in byte 1:

- [Category DL 3.0]  $x'2F' = \times 8$  capable lane width, all lanes trained.

- [Category DL 3.0]  $x'2A' = \times 8$  capable lane width, but trained in  $\times 4$  degraded mode on odd lanes.

- [Category DL 3.1] x'1C' = ×4OL capable lane width, all 4 lanes trained.

- [Category DL 3.1] x'14' = ×4OL capable lane width, but trained to x2 degraded mode on lanes 7 and 0.

- [Category DL 3.1/4.0] x'2C' = ×8 capable lane width, all lanes trained.

- [Category DL 3.1/4.0] x'28' = ×8 capable lane width, but trained in ×4 degraded mode on inside lanes.

- [Category DL 3.1/4.0]  $x'24' = \times 8$  capable lane width, but trained in  $\times 4$  degraded mode on outside lanes.

Note: Bits 5 and 4 are mutually exclusive; therefore, only one of those bits may be set to a b'1'.

### 2.4 Deskew markers

When the TS1, TS2, or TS3 training sets are transmitted, deskew markers are sent every 32 blocks. The last three bytes of the deskew marker shall contain the following configuration information:

- Lane number

- Version number

- Lane widths supported

- TX transmission order

- TX lane swap requested

During TS1 transmission, if the received lane numbers are reversed, the link attempts to the swap the lanes. Each lane shall receive eight identical deskew markers in a row to accept the configuration information.

[Category DL 3.0/4.0] Table 2-5 defines the DL 3.0/4.0 deskew marker bits.

| Bytes | Bits | Last three bytes of deskew definition                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0     | 7:2  | Reserved.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|       | 1    | ×8 mode capable.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|       | 0    | Reserved.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 1     | 7    | Half width degraded mode capable.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       | 6    | Reserved.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|       | 5:0  | Version number.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 2     | 7    | <ul> <li>TX lane ordering for degraded modes:</li> <li>1 Transmit lanes as <u>FPGA</u>. (This lane's data is transmitted first.<br/>Then, the neighbor's data is transmitted.)</li> <li>0 Transmit lanes as host. (The neighbor's data is transmitted first. Then, this lane's data is transmitted.)</li> </ul> |  |  |  |  |  |

|       | 6    | TX lane swap requested (bus reversal). For more information, see Section 2.9 Lane (bu reversal on page 32.                                                                                                                                                                                                      |  |  |  |  |  |

|       | 5    | Reserved.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|       | 4:0  | Lane number.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

Table 2-5. [Category DL 3.0/4.0] Deskew marker bit definition

[Category DL 3.1] *Table 2-6* defines the DL 3.1 deskew marker bits. A device that supports both ×8 and ×4 OL shall handle the 4 lanes to be lanes 7, 5, 2, and 0.

| Bytes | Bits | Last three bytes of deskew definition                                                                                                                                                                          |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 7:4  | Reserved.                                                                                                                                                                                                      |

|       | 3    | Reserved.                                                                                                                                                                                                      |

|       | 2    | Reserved.                                                                                                                                                                                                      |

|       | 1    | ×8 mode capable.                                                                                                                                                                                               |

|       | 0    | $\times$ 4OL mode capable. Four outside lanes of a $\times$ 8 are capable in full function mode. Lanes may further degrade to $\times$ 2 and/or switch between $\times$ 2 and $\times$ 4 for power management. |

| 1     | 7    | Half-width degraded mode capable.                                                                                                                                                                              |

|       | 6    | Reserved.                                                                                                                                                                                                      |

|       | 5:0  | Version number.                                                                                                                                                                                                |

| 2     | 7    | Reserved.                                                                                                                                                                                                      |

|       | 6    | TX lane swap requested (bus reversal). For more information, see Section 2.9 Lane (bus) reversal on page 32.                                                                                                   |

|       | 5    | Power management capable.                                                                                                                                                                                      |

|       | 4:0  | Lane number.                                                                                                                                                                                                   |

Table 2-6. [Category DL 3.1] Deskew marker bit definition

### 2.5 [Category DL 3.1] Alternative training step

The host shall implement a configuration mode with an enable/disable bit to send scrambled data to allow endpoint RX devices or cable re-timers to sync.

If enabled and before transmitting the first pattern A, the host shall send scrambled data for a configurable length of time between 256  $\mu$ s - 4s. After the timer expires, the DL shall start the normal training sequence by sending pattern A. This alternative training step is defined in a host's platform architecture specification.

### 2.6 Endpoint link speed discovery

Both sides of the link initially run at their maximum link speed. The host DL initially transmits pattern A at its fastest supported speed. For more information, see *Table 2-7 Planned revisions and supported speeds* on page 26. It samples the periodicity of the received pattern A clock edges to determine if the RX is sampling a slower clock speed. If the host receiver detects an incoming periodicity that is slower than what its TX is sending, the RX sets a <u>FIR</u>. The exact definition of the FIR is defined by the host processor implementation specification. Software shall perform the following functions:

- 1. De-activate the OCDE to the endpoint (active high).

- 2. Reconfigure the host phase-locked loop (PLL) for the next supported slower speed. For more information, see *Table 2-7* on page 26.

- 3. Wait for the host's PLL to re-lock.

- 4. Activate the OCDE to the endpoint (active high).

- 5. Start the initialization procedure again. The number of iterations that is supported before an unrecoverable event is detected is defined by the host architecture specification.

*Figure 2-3* and *Figure 2-4* show how a faster or slower pattern A is decoded. (The speeds in the following figures are representative of mismatched frequencies as delineated in *Table 2-7* on page 26.)

#### Figure 2-3. Faster pattern A

| TX at 20.0 Gbps     |      |           |      |      |           |        |

|---------------------|------|-----------|------|------|-----------|--------|

| Pattern A           | FF00 | FF00      | FF00 | FF00 | FF00      | FF00   |

| RX at 25 Gbps       |      |           |      |      |           |        |

| Elongated pattern A | FFE0 | 03FF 001F | FC00 | FFE0 | 03FF 0011 | F FC00 |

|                     |      |           |      |      |           |        |

Detection of an elongated pattern A by the host indicates that the endpoint is running slower, and the host PLL shall be reconfigured to the next supported slower speed.

#### Figure 2-4. Slower pattern A

| TX at 25 Gbps       |      |      |      |      |      |      |      |      |

|---------------------|------|------|------|------|------|------|------|------|

| Pattern A           | FF00 |

| RX at 20.0 Gbps     |      |      |      |      |      |      |      |      |

| Shortened pattern A | FC0F | COF  | C    | 0FC0 | FC0F | CO   | FC   | 0FC0 |

Detection of a shortened pattern A by the host indicates that the endpoint is running faster, but no host action is required to be taken because the endpoint must be reconfigured to the next supported slower speed. For example, an endpoint FPGA must be reloaded with a new bit image that was created with the next supported slower speed and a new IPL must be re-initiated. Or, if an ASIC, the endpoint's PLL must be re-configured to the next supported slower speed during the IPL sequence. The ASIC IPL sequence is defined in the host's platform architecture specification.

*Table 2-7* on page 26 shows the planned revisions and supported speeds. Endpoints are not required to support all speeds for the versions that it implemented. Hosts are required to support all speeds for the version that it implemented.

| Revision                                                                                                                                                  | Speeds (Gbps)                                                                              | Reference_Clock                                  | Capable Link widths |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------|

| DL 3.0                                                                                                                                                    | 25.78125 <sup>(1)</sup> , 20.0 <sup>(4)</sup>                                              | 156.25 (OIF Standard)                            | ×8                  |

| DL 3.1                                                                                                                                                    | 25.6 <sup>(1)</sup> , 21.33 <sup>(2)</sup>                                                 | 133.33 (JEDEC Standard)                          | ×40L, ×8            |

| DL 4.0                                                                                                                                                    | 31.875 <sup>(1)</sup> , 25.78125 <sup>(3)</sup> , 20.0 <sup>(4)</sup><br>32 <sup>(1)</sup> | 156.25 (OIF Standard)<br>133.33 (JEDEC Standard) | ×8<br>x8            |

| <ol> <li>Plan of record.</li> <li>Pre-IPL knowledge of link speeds, so</li> <li>Backwards speed compatibility.</li> <li>Lab testing mode only.</li> </ol> | o no requirement to detect link speec                                                      | ls.                                              |                     |

Table 2-7. Planned revisions and supported speeds

When both sides of the link detect that they are running the same bit rate, the PHY initialization starts counting the number of A patterns that it received.

### 2.7 Degraded modes

During the TS2 and TS3 training patterns, the trained lanes are transmitted back to the sender. If all of the lanes are trained, the link transmits across all lanes. If any lane of a group does not receive good training sets, that lane is marked as invalid and the link transmits on only the valid trained lanes (degraded mode). For more information, see *Table 2-3 [Category DL 3.0] TS2 and TS3 good lanes bit definitions* on page 21 or *Table 2-4 [Category DL 3.1/4.0] TS2 and TS3 good lanes bit definitions* on page 22.

### 2.8 Lane width detection and degraded mode flit transmission order

During the deskew training pattern, each side of the link transmits all of the lane widths that it supports. If more than one lane width is common between the two ends, the widest width is used. The lane-width information is used to configure the TL-to-DL ratio and the corresponding bytes-to-lane multiplexes.

*Table 2-8* shows which table to use to determine the bytes-to-lane multiplexing.

| OpenCAPI<br>Data Link<br>Layer<br>Version(s) | Width     | Mode                                | Table<br>2-9 | Table<br>2-10 | Table<br>2-11 | Table<br>2-12 | Table<br>2-13 | Table<br>2-14 | Table<br>2-15 | Table<br>2-16 | Table<br>2-17 | Table<br>2-18 | Table<br>2-19 | Table<br>2-20 |

|----------------------------------------------|-----------|-------------------------------------|--------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| 0,1,2                                        | ×8        | Full-width                          | Х            |               |               |               |               |               |               |               |               |               |               |               |

| 0                                            | ×8        | Half-width degraded even lanes      |              | Х             |               |               |               |               |               |               |               |               |               |               |

| 0                                            | ×8        | Half-width degraded odd lanes       |              |               | Х             |               |               |               |               |               |               |               |               |               |

| 3,4,5,6,8,9,10                               | ×8        | Full-width                          |              |               |               | Х             |               |               |               |               |               |               |               |               |

| 3,4,5,6,8,9,10                               | ×8        | Half-width degraded outside lanes   |              |               |               |               | х             |               |               |               |               |               |               |               |

| 3,4,5,6,8,9,10                               | ×8        | Half-width degraded<br>inside lanes |              |               |               |               |               | х             |               |               |               |               |               |               |