# Introducing the CXL 3.1 Specification

Presented by Rob Blankenship and Mahesh Wagh

# CXL Ecosystem

Growth of CXL ecosystem since its inception

Ecosystem that meets the ever-increasing performance and scale requirements

Fully backwards compatible

Lower overall system cost

Comprehensive compliance and testing support

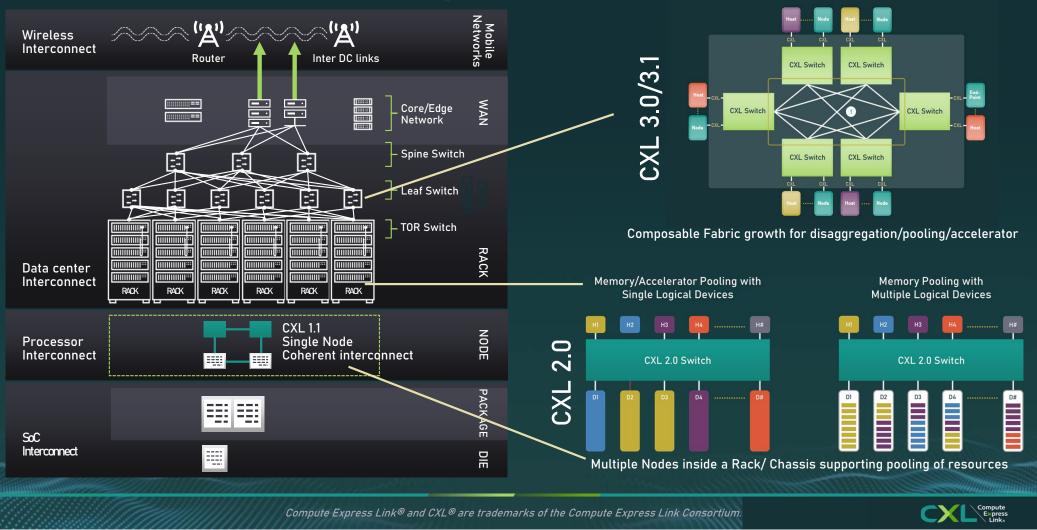

#### Data Center: Expanding Scope of CXL

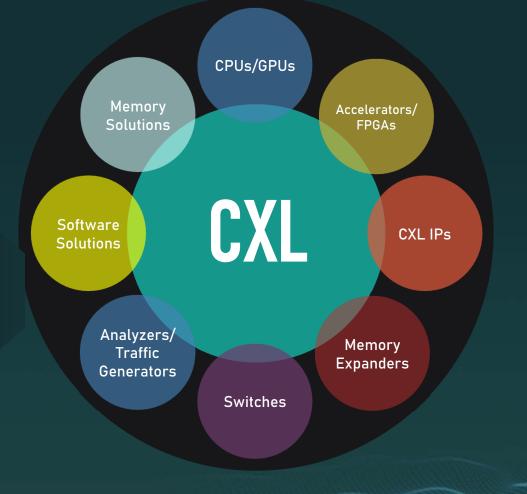

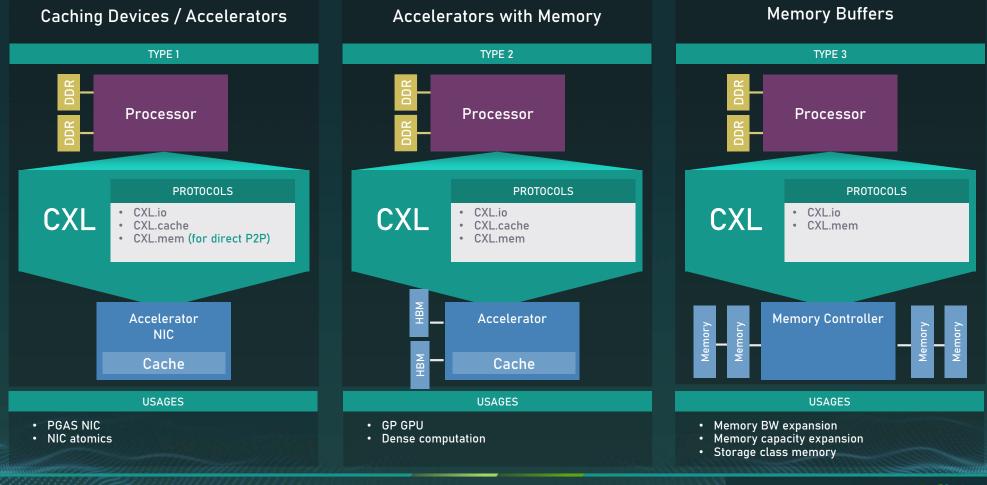

## **Representative CXL Usages**

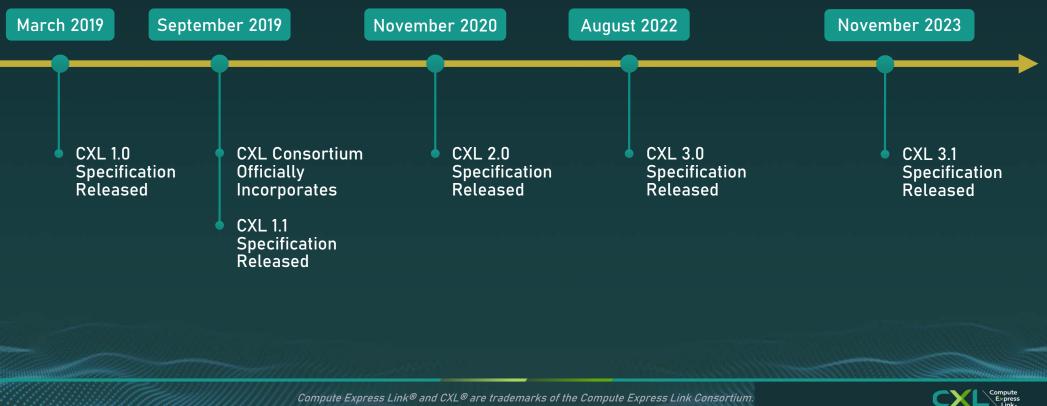

# **CXL** Specification Release Timeline

## **CXL** Specification Feature Summary

| Features                                     | CXL 1.0 / 1.1 | CXL 2.0      | CXL 3.0      |

|----------------------------------------------|---------------|--------------|--------------|

| Release date                                 | 2019          | 2020         | August 2022  |

| Max link rate                                | 32GTs         | 32GTs        | 64GTs        |

| Flit 68 byte (up to 32 GTs)                  | $\checkmark$  | $\checkmark$ | $\checkmark$ |

| Flit 256 byte (up to 64 GTs)                 |               |              | $\checkmark$ |

| Type 1, Type 2 and Type 3 Devices            | $\checkmark$  | $\checkmark$ | $\checkmark$ |

| Memory Pooling w/ MLDs                       |               | $\checkmark$ | $\checkmark$ |

| Global Persistent Flush                      |               | $\checkmark$ | $\checkmark$ |

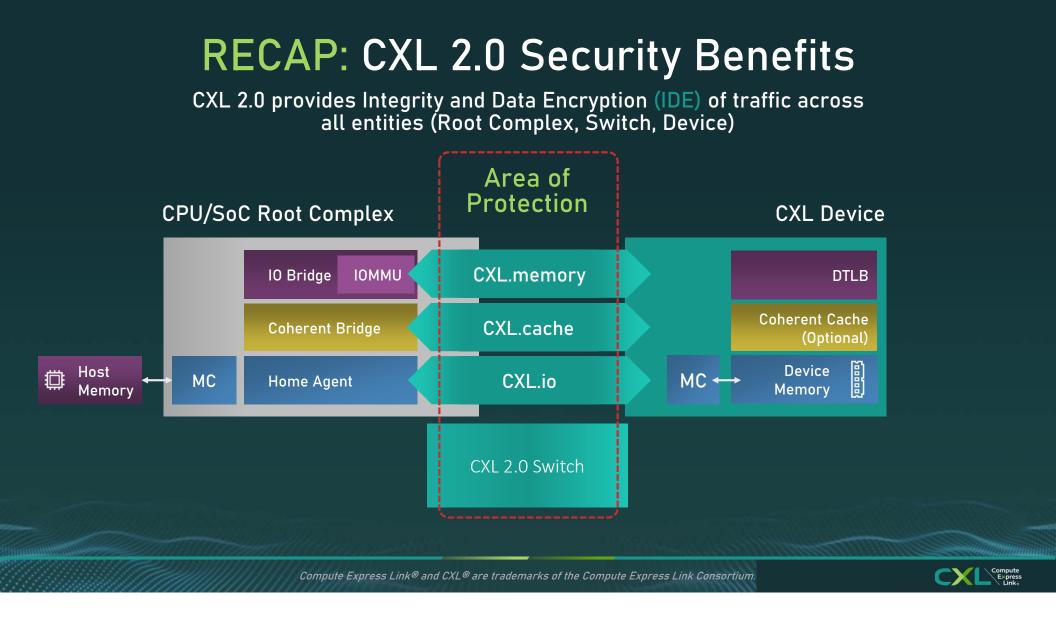

| CXL IDE                                      |               | $\checkmark$ | $\checkmark$ |

| Switching (Single-level)                     |               | $\checkmark$ | $\checkmark$ |

| Switching (Multi-level)                      |               |              | $\checkmark$ |

| Direct memory access for peer-to-peer        |               |              | $\checkmark$ |

| Enhanced coherency (256 byte flit)           |               |              | $\checkmark$ |

| Memory sharing (256 byte flit)               |               |              | $\checkmark$ |

| Multiple Type 1/Type 2 devices per root port |               |              | $\checkmark$ |

| Fabric capabilities (256 byte flit)          |               |              | $\checkmark$ |

Not Supported 🗸 Supported

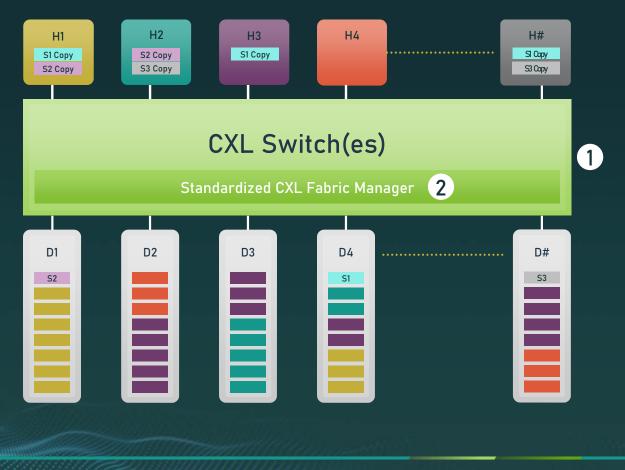

## **RECAP:** CXL 3.0: POOLING & SHARING

1 Expanded use case showing memory sharing and pooling

2 CXL Fabric Manager is available to setup, deploy, and modify the environment

#### CXL 3.1

Feature enhancements

Compute Express Link@ and CXL@ are trademarks of the Compute Express Link Consortium.

······

......

# **CXL 3.1** Feature Enhancements

- The CXL specification continues to evolve to meet new usage models

- New features introduced in the CXL 3.1 specification:

- CXL Fabric Improvements/Extensions

- Scale-out of CXL fabrics using PBR (Port Based Routing)

- Trusted-Execution-Environment Security Protocol (TSP)

- Allows for Virtualization-based Trusted Execution Environments (TEEs) to host Confidential Computing Workloads

- Memory Expander Improvements

- Up to 32-bit of meta data and RAS capability enhancements

#### CXL Fabric Improvements/ Extensions

*Compute Express Link® and CXL® are trademarks of the Compute Express Link Consortium.*

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### CXL Fabric Improvements/Extensions

- Fabric Decode/Routing requirements

- Host-to-Host communication with Global Integrated Memory (GIM) concept

- Direct P2P .mem support through PBR Switches

- Adds symmetric .mem Link Layer definition for devices

- Enables direct caching of CXL.mem for an accelerator, which is not possible with UIO

- Fabric Manager (FM) API definition for PBR Switch

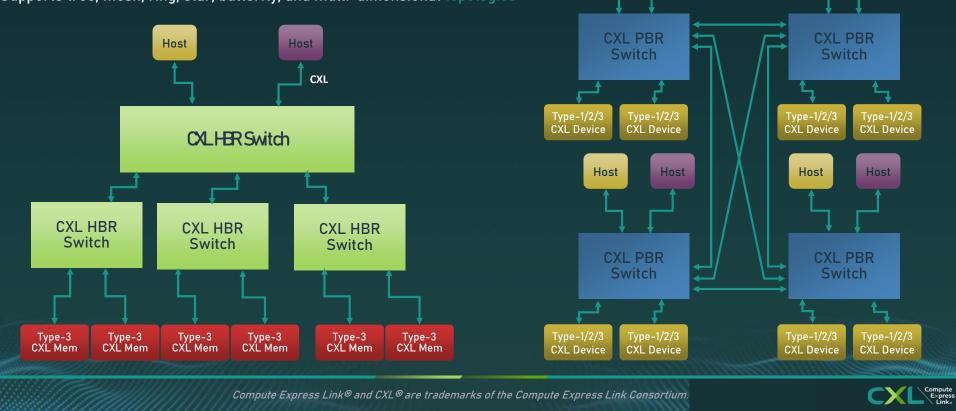

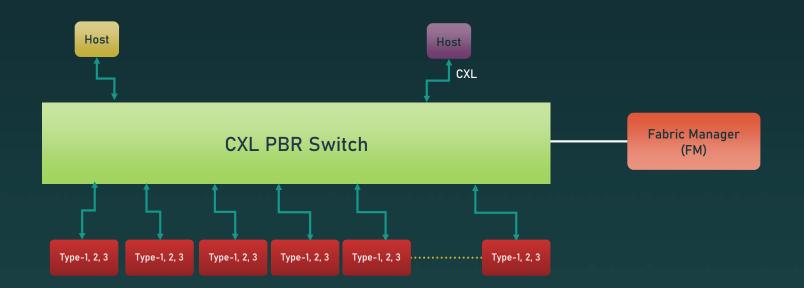

Port-Based Routing (PBR) compared to Hierarchy-Based Routing (HBR)

Support fabric topologies other than tree topologies that HBR switches offer

- Address-based, non-prescriptive routing for large memory fabrics

- Supports tree, mesh, ring, star, butterfly, and multi-dimensional topologies

Host

Host

Host

Host

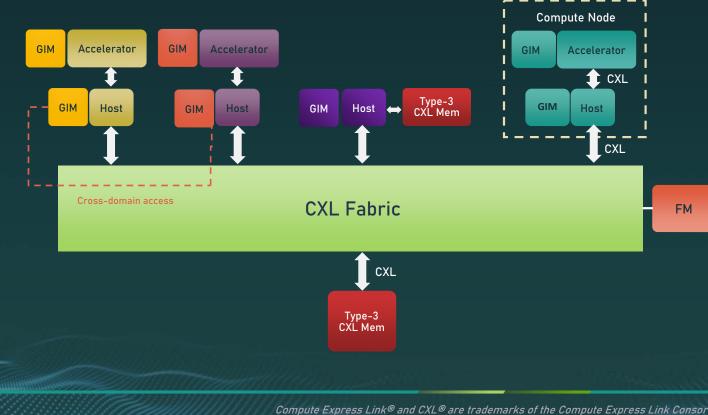

Host-to-Host communication with Global Integrated Memory (GIM) concept

Host to Fabric-Attached Memory (FAM) communication with Global Integrated Memory (GIM)

- Multiple Hosts mapping CXL ٠ Fabric-Attached Memory devices

- Hosts and FAM devices can initiate ٠ cross-domain accesses to GIM

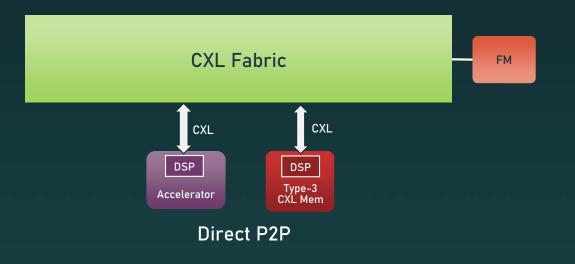

Direct peer-to-peer (P2P) .mem support for Accelerators through PBR Switches

#### Direct P2P CXL.mem for Accelerators

- Enables accelerator access to peer Type-3 memory

- The accelerator and Type-3 device must each be directly connected to an Edge Downstream Port (DSP)

- Utilizes port-based routing (PBR) for transactions

- Target memory device can be dedicated or shared with the host.

Fabric Manager (FM) API definition for PBR Switch

#### Trusted Execution Environment (TEE) & <u>TEE Security Protocol (TSP)</u>

*Compute Express Link® and CXL® are trademarks of the Compute Express Link Consortium.*

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

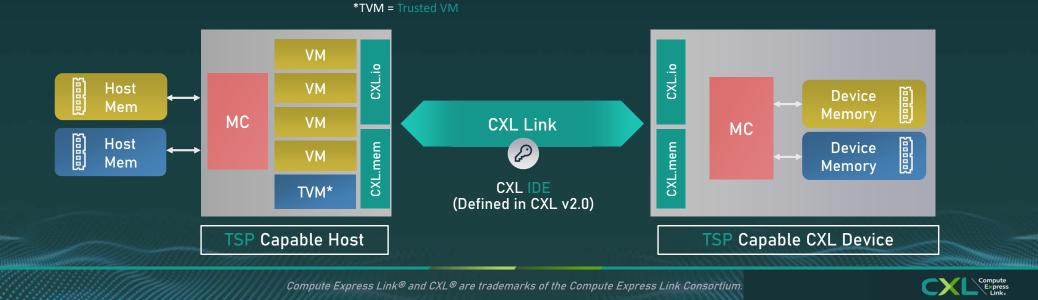

### CXL 3.1 Trusted Security Protocol (TSP)

Allows for Virtualization-based, Trusted Execution Environments (TEEs) to host Confidential Computing Workloads (CC WL)

#### Key Capabilities:

- Separation between TVM\* & CSP's infrastructure (VMM)

- Configuration of CXL device

- Encryption of sensitive data in both Host/Device memory

- Cryptographically verify correct configuration of trusted computing environment

#### **Benefits:**

- Freedom to migrate sensitive WLs to TSP-enabled Clouds

- Collaboration with multiple parties for sharing data

- Conform to Compliance & Data sovereignty programs

- Strengthen Application security & Software IP protection

### Elements of TSP / TSP Overview

#### TSP Components for Confidential Computing

- Trusted Execution State & Access Control

- How access to memory is controlled

- Configuration

- Ability to determine the supported security features on the device, enable required features, and lock the configuration

- Attestation & Authentication

- Trusting who you are talking to

- Memory Encryption

- Encrypting data-at-rest

- Transport Security

- Encrypting the link to protect data-in-flight and detect/prevent physical attacks

# Trusted Execution<br/>State & Access<br/>ControlConfigurationAttestation<br/>Attestation<br/>(Data-at-rest)Memory<br/>Encryption<br/>(Data-in-flight)Transport<br/>Security<br/>(Data-in-flight)CkL Intercond Execution Environment Security Protocol (TSP)CkL memory expander (target)

HDM-H (CXL 3.1), HDM-DB (Future)

## Memory Expander Improvements

*Compute Express Link® and CXL® are trademarks of the Compute Express Link Consortium.*

······

#### **Enhancements to CXL-Attached Memory**

Compute E×press Link₀

The CXL 3.1 specification provides for up to 32-bits of meta data per cacheline

CXL 3.1 supports 2-bits of meta-data for cache coherency that are used to describe if a cache line is shared, exclusive, modified, or invalid and up to 32-bits for additional meta-data

####

The extended meta data may be used with Host coherent and Device coherent memory

Extended meta data allows more information about the line to be available

Possible use cases • Access control, data type tagging, and memory-tiering algorithms • Supports proposed DDR6 feature that adds 16-32 bits of meta data for each 64B of data

#### Q

Improved visibility into CXL memory device errors

Additional information on errors such as correctable error limits New information on the source of the errors and the transaction occurring during the error condition

Added control over memory device RAS

Memory-sparing DDR5 error-check-scrubbing Media testing Patrol-scrub Capacity or performance degradation

Direct peer-topeer CXL memory access for accelerators

#### **CXL Specification Feature Summary**

| Features                                                                              | CXL 1.0 / 1.1 | CXL 2.0      | CXL 3.0      | CXL 3.1       |

|---------------------------------------------------------------------------------------|---------------|--------------|--------------|---------------|

| Release date                                                                          | 2019          | 2020         | August 2022  | November 2023 |

| Max link rate                                                                         | 32GTs         | 32GTs        | 64GTs        | 64GTs         |

| Flit 68 byte (up to 32 GTs)                                                           | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Flit 256 byte (up to 64 GTs)                                                          |               |              | $\checkmark$ | $\checkmark$  |

| Type 1, Type 2 and Type 3 Devices                                                     | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Memory Pooling w/ MLDs                                                                |               | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Global Persistent Flush                                                               |               | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| CXL IDE                                                                               |               | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Switching (Single-level)                                                              |               | ✓            | $\checkmark$ | $\checkmark$  |

| Switching (Multi-level)                                                               |               |              | $\checkmark$ | $\checkmark$  |

| Direct memory access for peer-to-peer                                                 |               |              | $\checkmark$ | $\checkmark$  |

| Enhanced coherency (256 byte flit)                                                    |               |              | $\checkmark$ | $\checkmark$  |

| Memory sharing (256 byte flit)                                                        |               |              | $\checkmark$ | $\checkmark$  |

| Multiple Type 1/Type 2 devices per root port                                          |               |              | $\checkmark$ | $\checkmark$  |

| Fabric capabilities (256 byte flit)                                                   |               |              | $\checkmark$ | $\checkmark$  |

| Fabric Manager API definition for PBR Switch                                          |               |              |              | ✓             |

| Host-to-Host communication with Global Integrated Memory (GIM) concept                |               |              |              | ✓             |

| Trusted-Execution-Environment (TEE) Security Protocol                                 |               |              |              | ✓             |

| Memory expander enhancements (up to 32-bit of meta data, RAS capability enhancements) |               |              |              | ✓             |

Not Supported 🖌 Sup

# CXL 3.1 Summary

- The CXL specification continues to evolve to meet the usage models

- New features introduced in the CXL 3.1 specification:

- CXL Fabric Improvements/Extensions

- Scale-out of CXL fabrics using PBR (Port Based Routing)

- Trusted-Execution-Environment Security Protocol (TSP)

- Allows for Virtualization-based, Trusted Execution Environments (TEEs) to host Confidential Computing Workloads

- Memory Expander Improvements

- Up to 32-bit of meta-data and RAS capability enhancements

#### www.ComputeExpressLink.org

Compute

Express

Please share your questions in the Question Box

Compute Express Link® and CXL® are trademarks of the Compute Express Link Consortium.

### Thank You

www.ComputeExpressLink.org