The CXL 2.0 specification introduced support for switching, memory pooling, and for persistent memory – all while preserving industry investments by supporting full backward compatibility. Based on member feedback, CXL 2.0 ECNs made significant improvements to the specifications in the areas of device management, RAS, Security, memory interleaving and others.

“An Overview of the Compute Express Link™ (CXL™) 2.0 ECN” webinar explored the key CXL 2.0 specification ECNs and the new usages. If you missed the live webinar, the recording is available on BrightTALK and YouTube. The presentation is also available for download on the CXL Consortium’s Resources webpage.

We received great questions during the Q&A portion of the webinar. Below is a recap of the questions and answers discussed in the webinar.

Q: Is 3-way interleaving only supported at the proprietary cross-host-bridge level? Or can it be supported at each of the levels (for example the CXL Host-bridge, USP, Device)?

We didn’t want to affect switches and have them implement an awkward 3-way operation that adds latency and complexity. Therefore, we limited the 3-way math to only the host in the host propriety logic and the device. There is no support for 3-way interleaving at the USP.

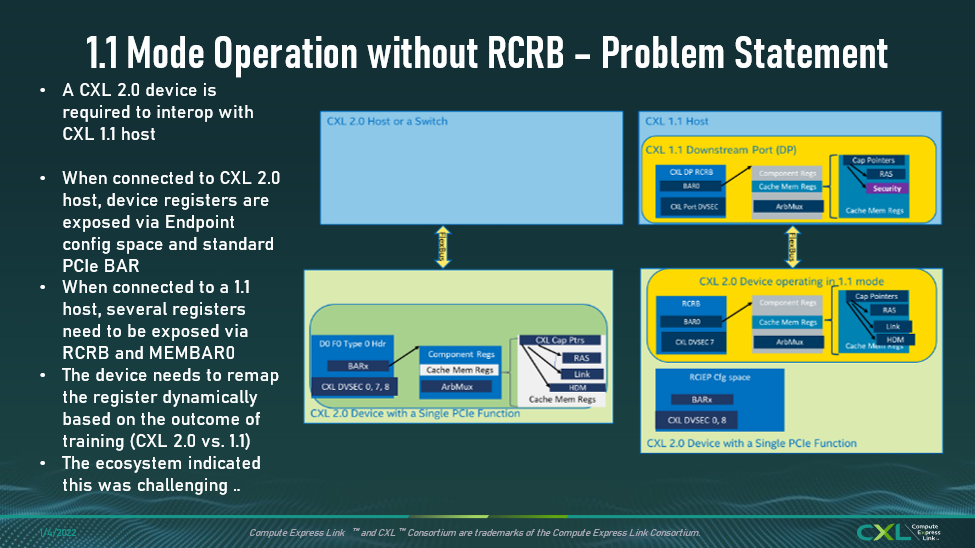

Q: What affect does no RCRB requirement have on RCEC requirements?

RCEC is required if the device is exposed as an RCIEP (Root Complex Integrated End Point). On slide 11, that aspect has not changed. The device on the right-hand side needs to be exposed as an RCIEP, and the link is still not visible to the legacy software because the downstream port has the same register layout as the CXL 1.1 specification. Therefore, you still need the host to implement the RCEC and the errors will always go with the RCEC. There is no difference in that behavior.

Q: What is BMC?

Baseboard Management Controller (BMC) is often used to manage the system in a manner that is isolated from the OS.

Q: Why are CXL IDE KM messages indicated as SPDM messages in the CXL IDE Establishment ECN? They are actually payload to the SPDM VENDOR_DEFINDE_REQUEST/*_RESPONSE messages.

This could be a matter of semantics. SPDM VENDOR_DEFINDE_REQUEST/*_RESPONSE are defined by the SPDM specificationfor vendor extensions.

Q: How do we distinguish the original CXL 2.0 specification vs. CXL 2.0 with ECN? Will the specification version be revised to CXL 2.1?

There is no plan for a CXL 2.1 specification. The CXL 2.0 ECN is available for download here. When the next-generation specification is released, the ECNs will be rolled into the new specification.

Q: Does the CXL 2.0 ECN support OS (Linux) for Integrity and Data Encryption (IDE)?

We are not aware of any code in the upstream right now that enables IDE. However, we are expecting that it will be available soon as we start seeing devices and designs take advantage of IDE.

Q: Where can we find the compliance tests? Is there a software application to do compliance tests like the PCIeCV Tests?

Chapter 14 of the CXL 2.0 specification lists the contents of the compliance tests. Download the CXL 2.0 specification here. The early version of the CXL compliance tests are available to the members.

Q: Is the latest version of CXL 2.0 with ECNs available on the CXL Consortium website?

Yes, the original CXL 2.0 specification and the standalone ECN documents are available for download here.

Stay tuned for future webinar presentations from the CXL Consortium. Subscribe to the CXL Consortium YouTube channel and CXL Consortium BrightTALK channel to be notified about upcoming webinars.

Follow us on Twitter and LinkedIn for more updates!

Compute Express Link™ and CXL™ Consortium are trademarks of the Compute Express Link Consortium.