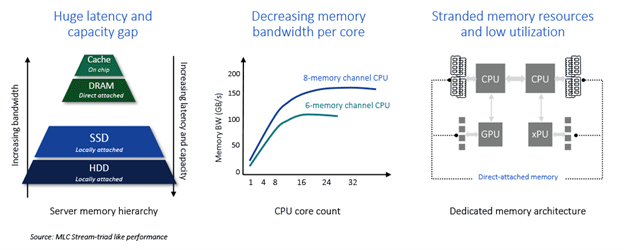

The disruption of GenAI over the last few years has forced system architects and hardware designers to rethink data center topologies. While AI model sizes and compute capability are growing exponentially, I/O throughput and memory access are growing linearly. These trends create an unsustainable gap that needs to be addressed across the stack starting from the physical layer at the chip level all the way to the network layer.

GenAI Data Center Challenges (Rambus)

New external cabling solutions enable ever-changing data center topologies. Rack scale connectivity, as an example, will define next-generation architectures over long-reach cables. Copper will work for a couple of meters, but optical solutions are needed for a rack-to-rack use case with a cable length of 7 meters and cable lengths exceeding 10 meters for larger clustering use cases.

GenAI Requires Higher-Performance Rack-to-Rack Optical Connectivity

Rambus, VIAVI, and Samtec will demonstrate CXL® (Compute Express Link®) over optics at the CXL Pavilion (Booth No. 1807) during Supercomputing (SC’24). The demo will show a CXL link over PCIe® using VIAVI’s Exerciser as the root complex with the Rambus DUT, as the endpoint.

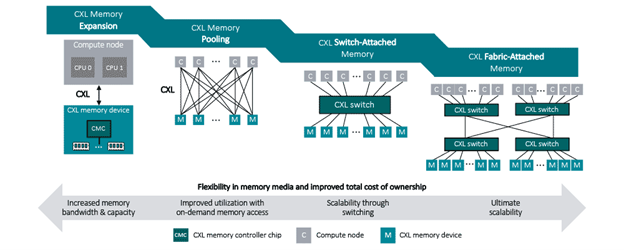

What is CXL?

CXL is a breakthrough high-speed CPU-to-Device and CPU-to-Memory interconnect designed to accelerate next-generation data center topologies.

CXL is an open industry standard offering high-bandwidth low-latency connectivity between the host processor and devices such as accelerators, memory controller/expander, and smart I/O devices for heterogeneous computing and disaggregation use cases.

The CXL Consortium is an open industry standard group formed to develop technical specifications that facilitate breakthrough performance for emerging usage models while supporting an open ecosystem for data center accelerators and other high-speed enhancements. The CXL Consortium represents a wide range of industry expertise including leading cloud service providers, communications OEMs, IP/silicon/device providers, and system OEMs.

Rambus CXL Controller IP

Rambus’ high-performance CXL controller IP is optimized for use in SoCs, ASICs, and FPGAs. These industry-leading solutions for high-performance interfaces address AI/ML, data center, and edge applications.

CXL Controller IP is used in a Variety of Applications

The Rambus CXL Controller IP leverages a silicon-proven PCIe controller architecture for the CXL.io path and adds CXL.cache and CXL.mem paths specific to the CXL standard. The controller IP exposes a native Tx/Rx user interface for CXL.io traffic as well as an Intel CXL-cache/mem Protocol Interface (CPI) for CXL.mem and CXL.cache traffic.

The provided Graphical User Interface (GUI) Wizard allows designers to tailor the IP to their exact requirements, by enabling, disabling, and adjusting a vast array of parameters, including CXL device type, PIPE interface configuration, buffer sizes, and latency, low power support, SR-IOV parameters, etc. for optimal throughput, latency, size, and power.

For more information about the Rambus CXL product portfolio, please visit www.rambus.com/cxl.

The controller IP can be delivered standalone or integrated with the customer’s choice of CXL/PCIe compliant SerDes. It can also be provided with example reference designs for integration with FPGA SerDes.

VIAVI CXL Products

VIAVI Xgig® Analyzer solutions for PCIe 5.0/6.0 support PCIe/CXL.io and CXL.cache/memory transactions with advanced trigger and filter templates that enable faster debugging and root cause analysis. The Xgig captures valuable real-time metrics and performs detailed analytics across multiple protocols.

VIAVI Xgig Analyzer

VIAVI Xgig Exerciser solutions also support CXL compliance and traffic generation.

VIAVI PCIe interposers, such as the Xgig PCIe 16-lane CEM Interposer, can be used to capture CXL traffic running on a PCIe physical layer. The interposer creates a bi-directional interface between the protocol analyzer and the system under test.

For more information about VIAVI’s CXL product portfolio, please visit www.viavisolutions.com/cxl.

Samtec CXL Over Optics Technology

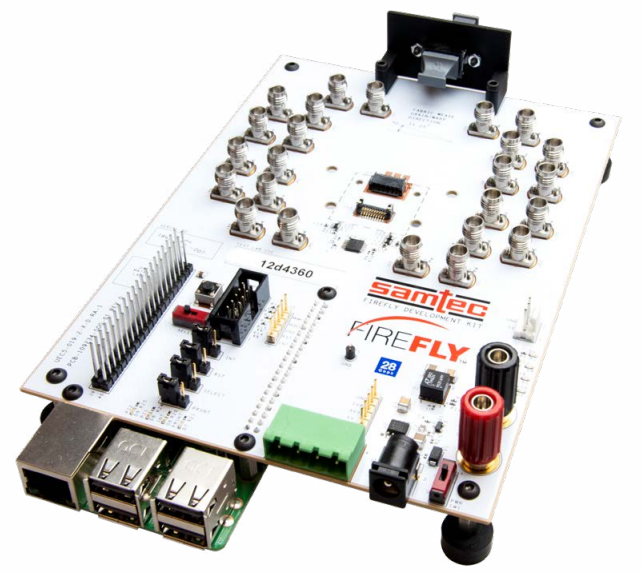

Samtec’s FireFly™ Micro Flyover System™ embedded and rugged optical transceivers take data connection via optical cable at greater distances or copper for cost optimization. FireFly is the first interconnect system that gives a designer the flexibility of using optical and copper interconnects interchangeably with the same connector system.

FireFly Evaluation Kit

Samtec’s PCUO series supports PCIe and CXL protocols via patented FireFly optical transceiver in x4, x8 and x16 configurations at PCIe 4.0/16 Gbps data rates. PCIe 5.0/32 Gbps and PCIe 6.0/64 Gbps PAM4 data rates are also under development. Additionally, Samtec also offers a growing family of optically-enables industry-standard PCB form factors (PCIe CEM AIC, OCP NIC 3.0, OCP OAI EXP, EDSFF E3.x 2T, etc.) for easy-to-use optical connectivity.

For more information about the Samtec CXL product portfolio, please visit www.samtec.com/cxl-interconnect.